何為ADC?

模擬數(shù)字轉(zhuǎn)換器,即A/D轉(zhuǎn)換器,或簡(jiǎn)稱ADC(Analog to Digital Converter),通常是指一個(gè)將模擬信號(hào)轉(zhuǎn)變?yōu)?a target="_blank">數(shù)字信號(hào)的電子元件。通常的模數(shù)轉(zhuǎn)換器是將一個(gè)輸入電壓信號(hào)轉(zhuǎn)換為一個(gè)輸出的數(shù)字信號(hào)。由于數(shù)字信號(hào)本身不具有實(shí)際意義,僅僅表示一個(gè)相對(duì)大小。故任何一個(gè)模數(shù)轉(zhuǎn)換器都需要一個(gè)參考模擬量作為轉(zhuǎn)換的標(biāo)準(zhǔn),比較常見的參考標(biāo)準(zhǔn)為最大的可轉(zhuǎn)換信號(hào)大小。而輸出的數(shù)字量則表示輸入信號(hào)相對(duì)于參考信號(hào)的大小。

A/D轉(zhuǎn)換的作用是將時(shí)間連續(xù)、幅值也連續(xù)的模擬信號(hào)轉(zhuǎn)換為時(shí)間離散、幅值也離散的數(shù)字信號(hào),因此,A/D轉(zhuǎn)換一般要經(jīng)過取樣、保持、量化及編碼4個(gè)過程。在實(shí)際電路中,這些過程有的是合并進(jìn)行的,例如,取樣和保持,量化和編碼往往都是在轉(zhuǎn)換過程中同時(shí)實(shí)現(xiàn)的。

這種轉(zhuǎn)換器的基本原理是把輸入的模擬信號(hào)按規(guī)定的時(shí)間間隔采樣,并與一系列標(biāo)準(zhǔn)的數(shù)字信號(hào)相比較,數(shù)字信號(hào)逐次收斂,直至兩種信號(hào)相等為止。然后顯示出代表此信號(hào)的二進(jìn)制數(shù),模擬數(shù)字轉(zhuǎn)換器有很多種,如直接的、間接的、高速高精度的、超高速的等。每種又有許多形式。同模擬數(shù)字轉(zhuǎn)換器功能相反的稱為“數(shù)字模擬轉(zhuǎn)換器”,亦稱“譯碼器”,它是把數(shù)字量轉(zhuǎn)換成連續(xù)變化的模擬量的裝置,也有許多種和許多形式。

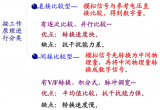

ADC的主要分類

下面簡(jiǎn)要介紹常用的幾種類型的基本原理及特點(diǎn):Σ-Δ調(diào)制型、逐次逼近型、積分型、并行比較型/串并行型、電容陣列逐次比較型及壓頻變換型。

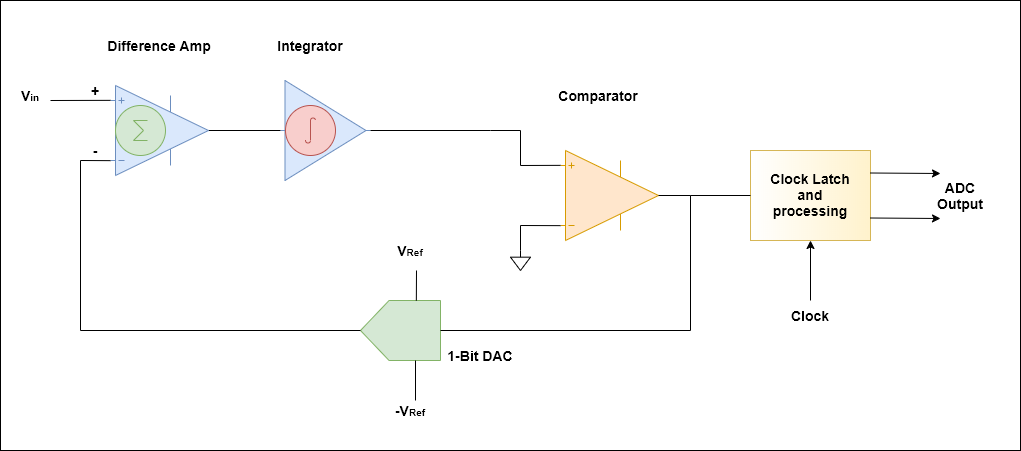

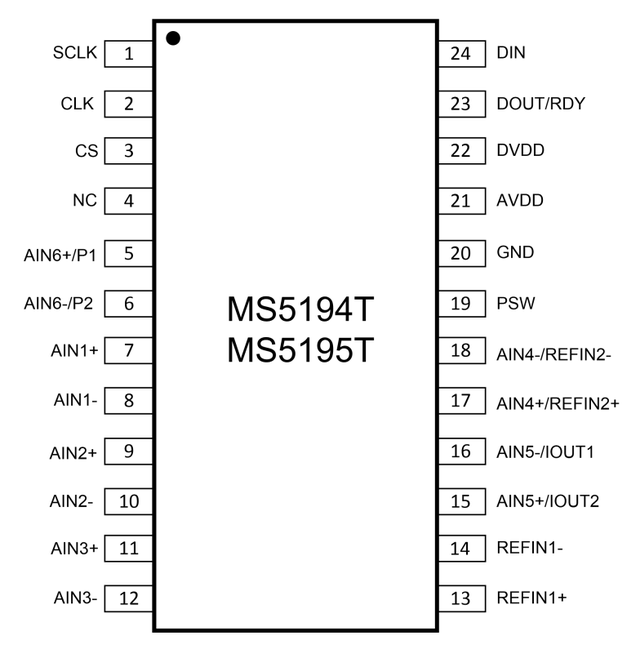

1、Σ-Δ ADC(Sigma-Delta)

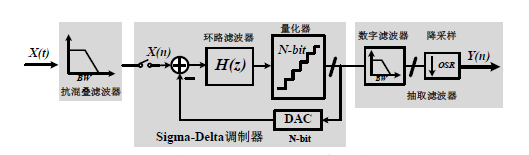

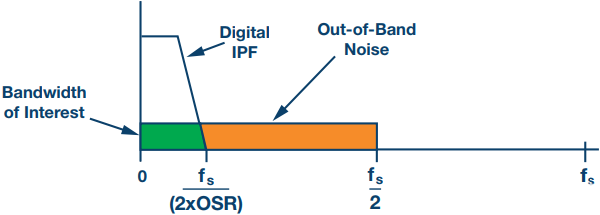

Σ-Δ ADC由積分器、比較器、1位DA轉(zhuǎn)換器和數(shù)字濾波器等組成。原理上近似于積分型,將輸入電壓轉(zhuǎn)換成時(shí)間(脈沖寬度)信號(hào),用數(shù)字濾波器處理后得到數(shù)字值。電路的數(shù)字部分基本上容易單片化,因此容易做到高分辨率。主要用于音頻和測(cè)量。

Σ-Δ ADC不是對(duì)信號(hào)的幅度進(jìn)行直接編碼,而是根據(jù)前一次采樣值與后一次采樣值之差(增量)進(jìn)行量化編碼,通常采用一位量化器,利用過采樣和∑-Δ調(diào)制技術(shù)來獲得極高的分辨率。Σ-ΔADC由非常簡(jiǎn)單的模擬電路和十分復(fù)雜的數(shù)字信號(hào)處理電路構(gòu)成。

∑-ΔADC三大關(guān)鍵技術(shù):過采樣,噪聲整形,數(shù)字濾波和采樣抽取。

優(yōu)點(diǎn):

分辨率較高,高達(dá)24位;轉(zhuǎn)換速率高,高于積分型和壓頻變換型ADC;價(jià)格低;內(nèi)部利用高倍頻過采樣技術(shù),實(shí)現(xiàn)了數(shù)字濾波,降低了對(duì)傳感器信號(hào)進(jìn)行濾波的要求。

缺點(diǎn):

高速Σ-Δ型ADC的價(jià)格較高;在轉(zhuǎn)換速率相同的條件下,比積分型和逐次逼近型ADC的功耗高。

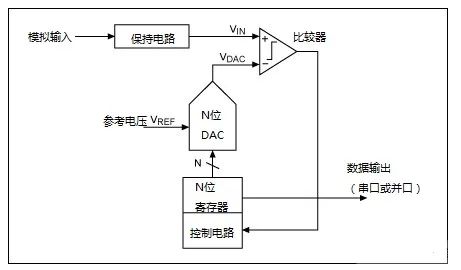

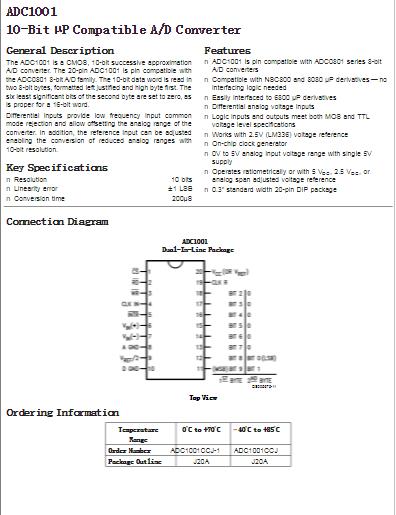

2、逐次逼近型(SAR)

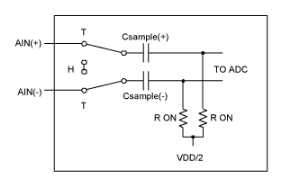

逐次逼近型ADC是應(yīng)用非常廣泛的模/數(shù)轉(zhuǎn)換方法,它包括1個(gè)比較器、1個(gè)數(shù)模轉(zhuǎn)換器、1個(gè)逐次逼近寄存器(SAR)和1個(gè)邏輯控制單元。它是將采樣輸入信號(hào)與已知電壓不斷進(jìn)行比較,1個(gè)時(shí)鐘周期完成位轉(zhuǎn)換,N位轉(zhuǎn)換需要N個(gè)時(shí)鐘周期,轉(zhuǎn)換完成,輸出二進(jìn)制數(shù)。

這一類型ADC的分辨率和采樣速率是相互矛盾的,分辨率低時(shí)采樣速率較高,要提高分辨率,采樣速率就會(huì)受到限制。

優(yōu)點(diǎn):

分辨率低于12位時(shí),價(jià)格較低,采樣速率可達(dá)1MSPS;與其它ADC相比,功耗相當(dāng)?shù)汀?/p>

缺點(diǎn):

在高于14位分辨率情況下,價(jià)格較高;傳感器產(chǎn)生的信號(hào)在進(jìn)行模/數(shù)轉(zhuǎn)換之前需要進(jìn)行調(diào)理,包括增益級(jí)和濾波,這樣會(huì)明顯增加成本。

SAR-ADC轉(zhuǎn)換器的原理比較簡(jiǎn)單,但是實(shí)現(xiàn)方式多種多樣,按照其中DAC的工作原理,大致可以將SAR-ADC轉(zhuǎn)換器分為三種類型:電壓定標(biāo)、電流定標(biāo)、電荷定標(biāo)。

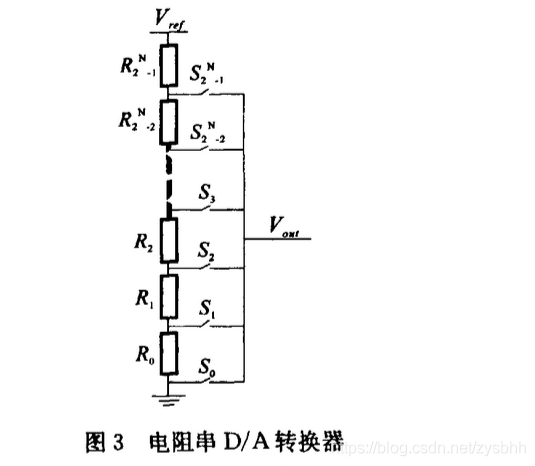

電壓定標(biāo)

電壓定標(biāo)出現(xiàn)最早,工作原理最簡(jiǎn)單,其電路結(jié)構(gòu)如下圖所示。

電阻串組成的電壓定標(biāo)型ADC最大的優(yōu)勢(shì)是能夠保持良好的單調(diào)性,得到了工業(yè)應(yīng)用。但是對(duì)于N位的SAR-ADC轉(zhuǎn)換器,需要2^N個(gè)單位電阻。隨著ADC轉(zhuǎn)換位數(shù)的增多,單位電阻和開關(guān)呈指數(shù)增加,例如對(duì)于8位的SAR-ADC,需要256個(gè)單位電阻和510個(gè)開關(guān),這么多單元所占芯片面積是相當(dāng)可觀的。

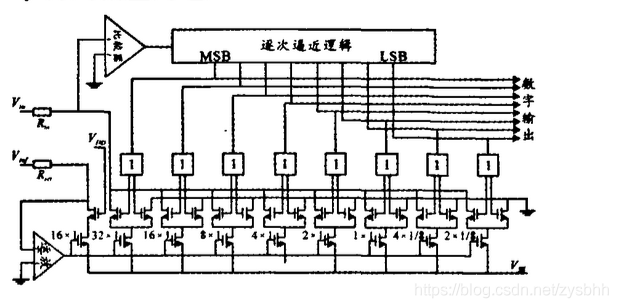

電流定標(biāo)

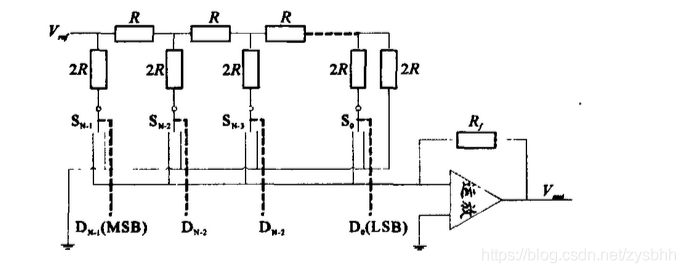

電流定標(biāo)也是早期常見的一種類型,它是利用二進(jìn)制加權(quán)的電流,配合開關(guān)實(shí)現(xiàn)二進(jìn)制搜索算法的。常見的電流定標(biāo)SAR-ADC又可以分為兩種,一種使用二進(jìn)制加權(quán)的電流源陣列,另一種使用R-2R階梯。

使用MOS管組成的這種結(jié)構(gòu),由于使用了電流開關(guān),所以轉(zhuǎn)換速度較快。但是MOS管的閾值電壓變化比較大,MOS管的參數(shù)的匹配誤差會(huì)影響二進(jìn)制加權(quán)電流源的匹配,給SAR-ADC轉(zhuǎn)換器帶來了較大的精度誤差。

使用R-2R階梯的電流定標(biāo)SAR-ADC可以在低電壓供電的情況下正常工作。但是MOS工藝的電阻匹配精度交叉,盡管可以使用溫度計(jì)編碼降低對(duì)電阻匹配精度的要求,但是,電阻阻值受溫度的影響較大,容易引入線性度誤差。

電荷定標(biāo)

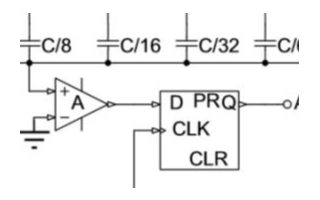

電荷定標(biāo)是目前應(yīng)用比較多的一種類型,它利用電容通過電荷再分配完成二進(jìn)制搜索算法,因此功耗一般比較小,而且不需要額外的采樣保持電路,按照電容的組織方式,可分為并行電容方式和串行電容方式。

并行電容

并行電容方式一般多指使用二進(jìn)制加權(quán)電容陣列的SAR-ADC,它的基本單元有二進(jìn)制加權(quán)的電容陣列、1個(gè)與LSB電容等值的電容、開關(guān)和比較器。

串行電容

串行電容方式使用串行DAC,僅通過2個(gè)等值電容的電荷再分配,即可 完成逐次逼近過程。對(duì)于一個(gè) N位的串行DAC,整個(gè)轉(zhuǎn)換需要N次預(yù)充電和N次電荷再分配過程。然而,串行DAC的轉(zhuǎn)換是從最低位開始的,故使用串行DAC的N位SAR ADC需要N(N+1)次充放電,而且需要N個(gè)比較器的建立時(shí)間。

串行電容方式的SAR ADC轉(zhuǎn)換器只需要兩個(gè)中等大小的電容,所以比并行電容SAR ADC轉(zhuǎn)換器的芯片面積更小,但是它能達(dá)到 精度受開關(guān)晶體管的寄生電容影響,而且轉(zhuǎn)換速度慢,應(yīng)用并不廣泛。

3、積分型

積分型AD工作原理是將輸入電壓轉(zhuǎn)換成時(shí)間(脈沖寬度信號(hào))或頻率(脈沖頻率),然后由定時(shí)器/計(jì)數(shù)器獲得數(shù)字值。

積分型ADC有不同的種類,常見的有單、雙斜率積分等。增加一個(gè)“斜率”,以犧牲轉(zhuǎn)換時(shí)間為代價(jià)而增加精度。

優(yōu)點(diǎn):

分辨率高,可達(dá) 22 位;線性度非常好。本質(zhì)上,輸入端與一個(gè)集成的參考電壓相比較來決定輸出端,所以線性度將取決于比較器的精度;電路實(shí)現(xiàn)拓?fù)浜?jiǎn)單,用于實(shí)現(xiàn)這些設(shè)備的元件相對(duì)較少,因此電路相對(duì)簡(jiǎn)單且生產(chǎn)成本較低。

缺點(diǎn):

轉(zhuǎn)換速率低,轉(zhuǎn)換速率在12 位時(shí)為100~300SPS。

初期的單片AD轉(zhuǎn)換器大多采用積分型,現(xiàn)在逐次逼近型已逐步成為主流。

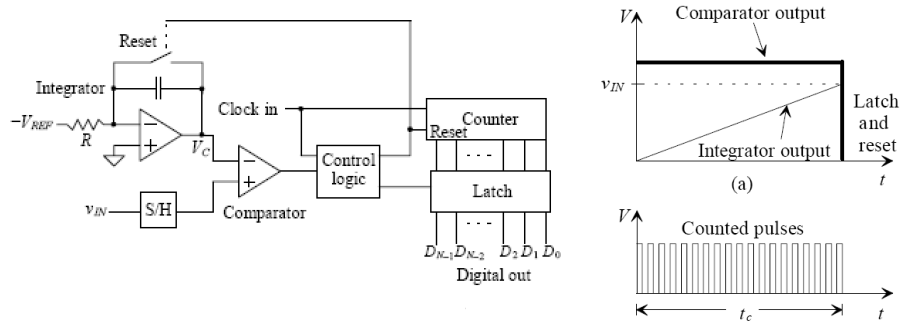

單斜率積分ADC

比較器將輸入電壓與集成基準(zhǔn)電壓的值進(jìn)行比較(請(qǐng)注意,由于已連接至運(yùn)算放大器的反相輸入,因此我們將設(shè)為負(fù))。同時(shí)計(jì)算時(shí)鐘周期數(shù)。當(dāng)積分器輸出等于時(shí),比較器輸出邏輯“ 0”,觸發(fā)計(jì)數(shù)器和積分器復(fù)位,鎖存器保持?jǐn)?shù)字輸出。

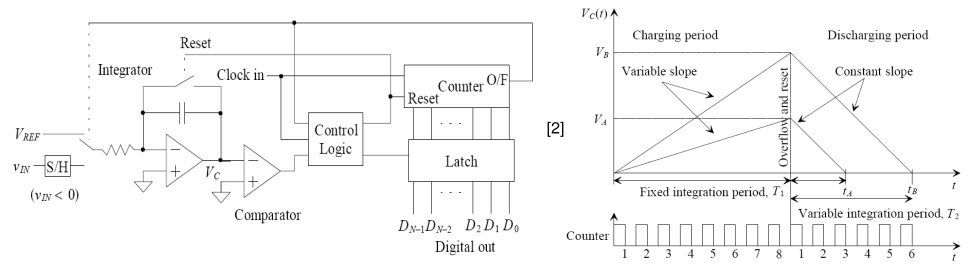

雙斜率積分ADC

雙斜率比單斜率ADC更慢,由于執(zhí)行了兩次積分, 與積分器斜率相關(guān)的誤差將被抵消,從而從原理上提高了精度。

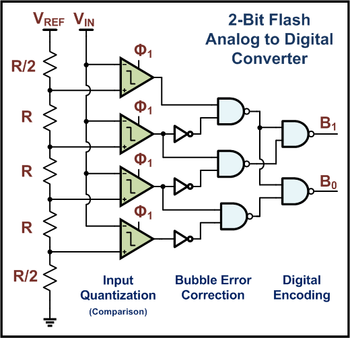

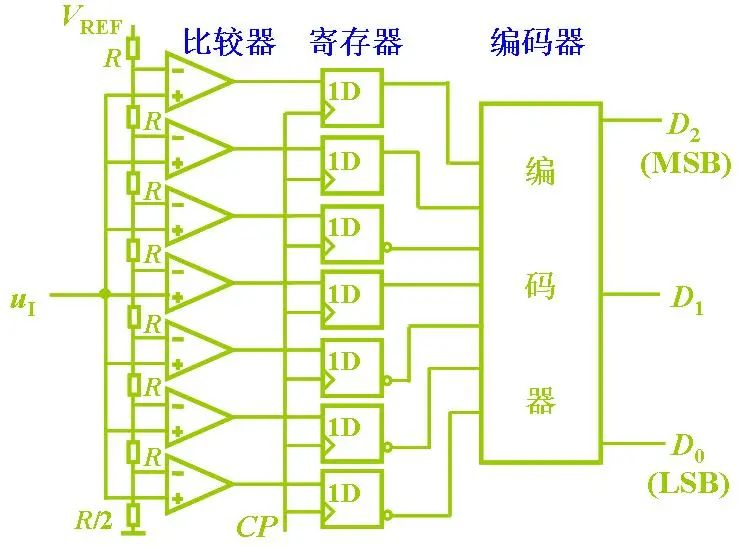

4、并行比較型/串并行比較型

并行比較型AD采用多個(gè)比較器,僅作一次比較而實(shí)行轉(zhuǎn)換,又稱FLash(快速)型。由于轉(zhuǎn)換速率極高,n位的轉(zhuǎn)換需要2n-1個(gè)比較器,因此電路規(guī)模也極大,價(jià)格也高,只適用于視頻AD轉(zhuǎn)換器等速度特別高的領(lǐng)域。

串并行比較型AD結(jié)構(gòu)上介于并行型和逐次比較型之間,最典型的是由2個(gè)n/2位的并行型AD轉(zhuǎn)換器配合DA轉(zhuǎn)換器組成,用兩次比較實(shí)行轉(zhuǎn)換,所以稱為 Half flash(半快速)型。

三步或多步實(shí)現(xiàn)AD轉(zhuǎn)換的叫做分級(jí)(Multistep/Subrangling)型AD,而從轉(zhuǎn)換時(shí)序角度又可稱為流水線(Pipelined)型AD,現(xiàn)代的分級(jí)型AD中還加入了對(duì)多次轉(zhuǎn)換結(jié)果作數(shù)字運(yùn)算而修正特性等功能。

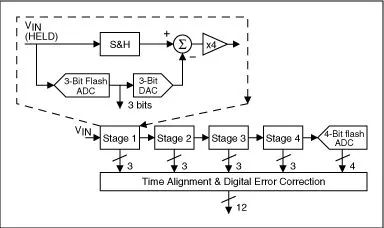

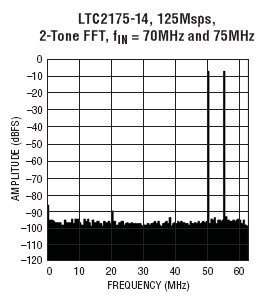

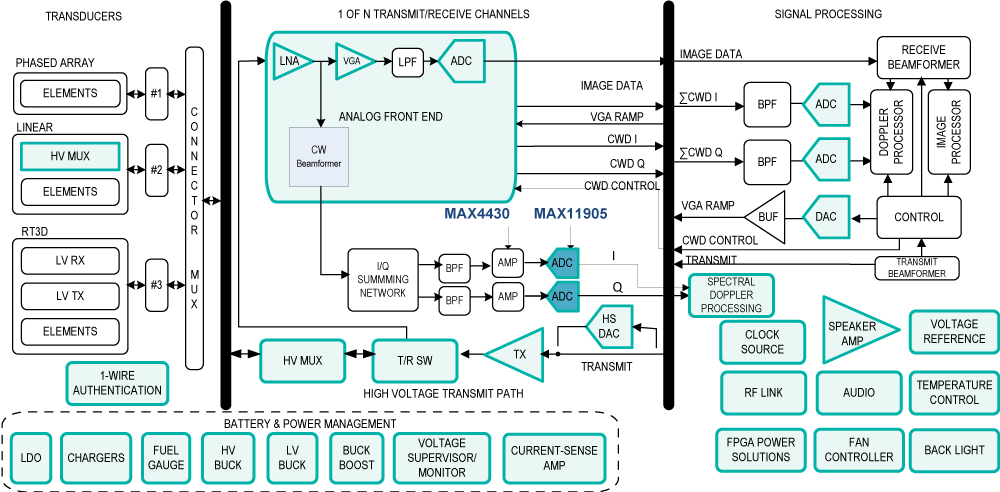

5、流水線型(Pipelined)

流水線結(jié)構(gòu)ADC,又稱為子區(qū)式 ADC,它是一種高效和強(qiáng)大的模數(shù)轉(zhuǎn)換器。它能夠提供高速、高分辨率的模數(shù)轉(zhuǎn)換,并且具有令人滿意的低功率消耗和很小的芯片尺寸;經(jīng)過合理的設(shè)計(jì),還可以提供優(yōu)異的動(dòng)態(tài)特性。流水線型 ADC 由若干級(jí)級(jí)聯(lián)電路組成,每一級(jí)包括一個(gè)采樣/保持放大器、一個(gè)低分辨率的 ADC 和 DAC 以及一個(gè)求和電路,其中求和電路還包括可提供增益的級(jí)間放大器。快速精確的 n 位轉(zhuǎn)換器分成兩段以上的子區(qū)(流水線)來完成 。首級(jí)電路的采樣/保持器對(duì)輸入信號(hào)取樣后先由一個(gè)m 位分辨率粗 A/D 轉(zhuǎn)換器對(duì)輸入進(jìn)行量化,接著用一個(gè)至少 n 位精度的乘積型數(shù)模轉(zhuǎn)換器(MDAC)產(chǎn)生一個(gè)對(duì)應(yīng)于量化結(jié)果的模/擬電平并送至求和電路,求和電路從輸入信號(hào)中扣除此模擬電平。并將差值精確放大某一固定增益后關(guān)交下一級(jí)電路處理。經(jīng)過各級(jí)這樣的處理后,最后由一個(gè)較高精度的 K 位細(xì) A/D 轉(zhuǎn)換器對(duì)殘余信號(hào)進(jìn)行轉(zhuǎn)換。將上述級(jí)粗、細(xì)A/D 的輸出組合起來即構(gòu)成高精度的 n 位輸出。

在這個(gè)原理圖中,模擬輸入VIN首先被采樣并由采樣保持器(S&H)保持穩(wěn)定,而第一階段的flash ADC將其量化為三位。然后將3位輸出饋給3位DAC(精確到12位),然后從輸入中減去模擬輸出。這個(gè)“剩余量”擴(kuò)大4倍并被送入下一階段(第二階段)。這個(gè)增加的剩余量繼續(xù)通過下級(jí)流水線,每一階段提供3位,直到它到達(dá)4位flash ADC,將解析最后的4LSB位。因?yàn)槊總€(gè)階段的位是在不同的時(shí)間點(diǎn)確定的,所以相同樣本對(duì)應(yīng)的所有位在被饋送到數(shù)字錯(cuò)誤校正邏輯之前都與移位寄存器進(jìn)行了時(shí)間對(duì)齊。請(qǐng)注意,當(dāng)一個(gè)流水完成對(duì)輸入樣本的處理,確定本流水采集位并將殘差傳遞到下一個(gè)流水時(shí),它便可以開始處理從每個(gè)流水中嵌入的采樣保持器接收到的下一個(gè)樣本。

這種流水線操作是高吞吐量的原因,這也是流水的概念。

流水線ADC可能有許多變化,這取決于幾個(gè)變量:每個(gè)階段解析多少位;LSB閃存ADC中的位數(shù);以及是否使用數(shù)字校準(zhǔn)或微調(diào)來提高前兩個(gè)階段的精度。每個(gè)階段的比特劃分部分由目標(biāo)采樣率和分辨率決定。

應(yīng)用

廣泛應(yīng)用于CCD成像、超聲波醫(yī)學(xué)成像、數(shù)字接收器、基站、數(shù)字視頻、電纜調(diào)制解調(diào)器和快速以太網(wǎng)。

采樣率比較低的應(yīng)用程序仍然是逐次逼近寄存器和集成體系結(jié)構(gòu)的領(lǐng)域,當(dāng)然還有過采樣。盡管如此,近年來各種形式的流水線ADC在速度、分辨率、動(dòng)態(tài)性能和低功耗方面都有了很大的提高。

大多數(shù)現(xiàn)代流水線ADC采用了一種“數(shù)字糾錯(cuò)”的技術(shù),大大降低了Flash ADC的精度要求。

優(yōu)點(diǎn):

有良好的線性和低失調(diào);可以同時(shí)對(duì)多個(gè)采樣進(jìn)行處理,有較高的信號(hào)處理速度,典型的為Tconv<100ns;低功率;高精度;高分辨率;可以簡(jiǎn)化電路。

缺點(diǎn):

基準(zhǔn)電路和偏置結(jié)構(gòu)過于復(fù)雜;輸入信號(hào)需要經(jīng)過特殊處理,以便穿過數(shù)級(jí)電路造成流水延遲;對(duì)鎖存定時(shí)的要求嚴(yán)格;對(duì)電路工藝要求很高,電路板上設(shè)計(jì)得不合理會(huì)影響增益的線性、失調(diào)及其它參數(shù)。

6、壓頻變換型

壓頻變換型(Voltage-Frequency Converter)是通過間接轉(zhuǎn)換方式實(shí)現(xiàn)模數(shù)轉(zhuǎn)換的。其原理是首先將輸入的模擬信號(hào)轉(zhuǎn)換成頻率,然 后用計(jì)數(shù)器將頻率轉(zhuǎn)換成數(shù)字量。從理論上講這種AD的分辨率幾乎可以無限增加,只要采樣的時(shí)間能夠滿足輸出頻率分辨率要求的累積脈沖個(gè)數(shù)的寬度。其優(yōu)點(diǎn)是分辯率高、功耗低、價(jià)格低,但是需要外部計(jì)數(shù)電路共同完成AD轉(zhuǎn)換。

優(yōu)點(diǎn):

精度高、價(jià)格較低、功耗較低。

缺點(diǎn):

類似于積分型 ADC,其轉(zhuǎn)換速率受到限制,12 位時(shí)為 100~300SPS。

?

以上介紹的是幾種常見的ADC類型和特點(diǎn),分享給大家參考。

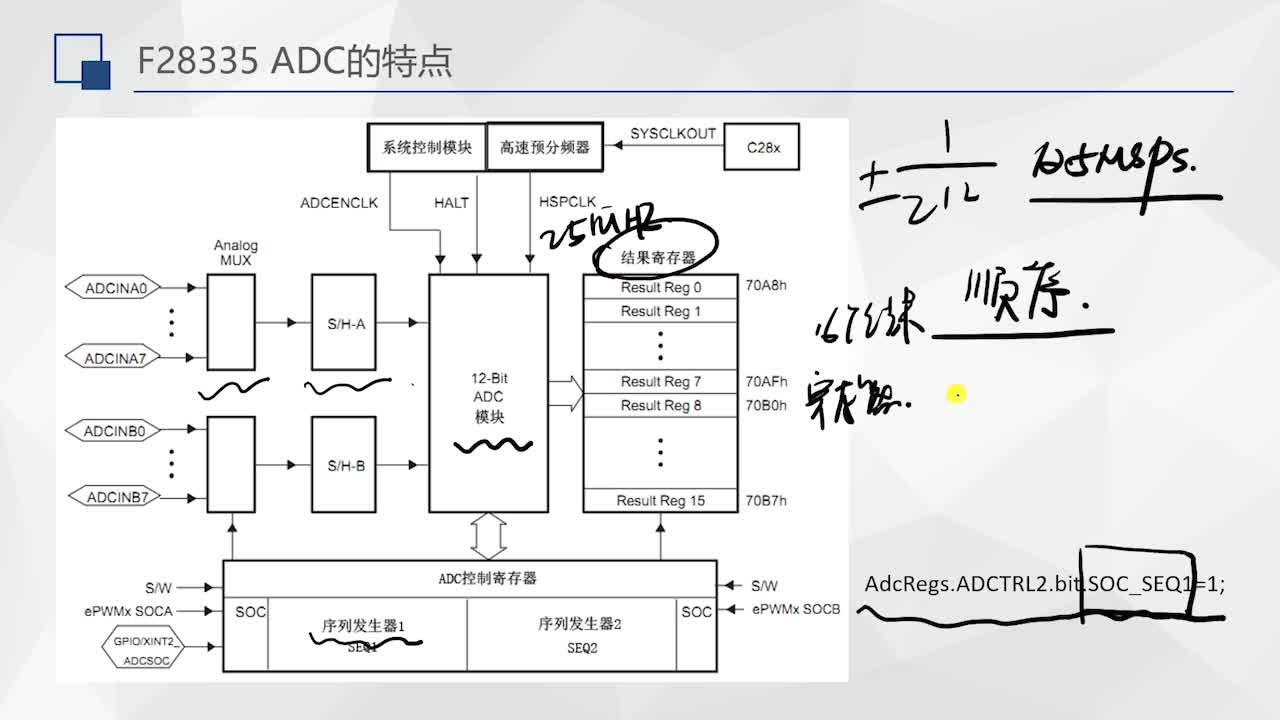

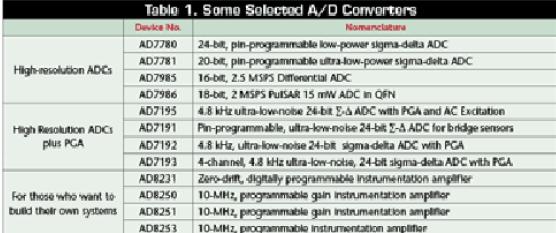

ADC芯片選型

針對(duì)各種ADC芯片,如何區(qū)分ADC芯片性能的好壞呢?

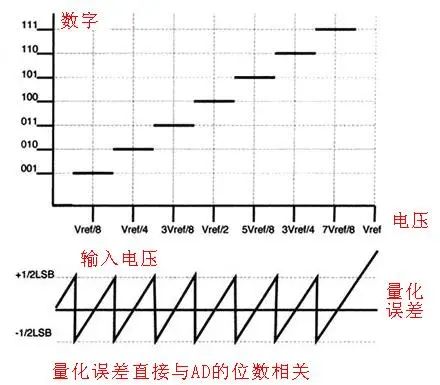

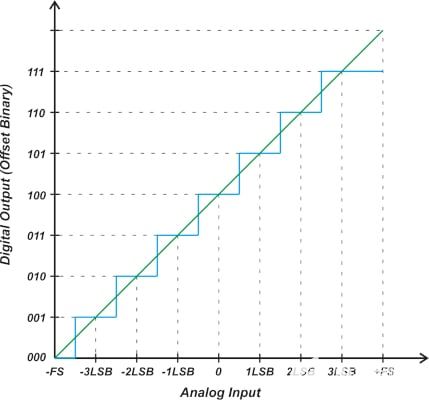

1、精度、也稱為分辨率(Resolution),單位(Bits)比特;精度越高的ADC轉(zhuǎn)換出來的數(shù)字信號(hào)越接近于原來真實(shí)的模擬信號(hào);另一方面,該精度只表示ADC輸出的位數(shù),不代表這些位數(shù)里真正的信號(hào)分量。

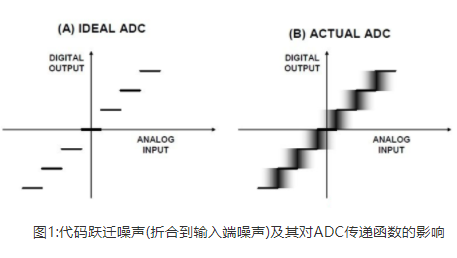

2、量化誤差 (Quantizing Error) 由于AD的有限分辯率而引起的誤差,即有限分辯率AD的階梯狀轉(zhuǎn)移特性曲線與無限分辯率AD(理想AD)的轉(zhuǎn)移特性曲線(直線)之間的最大偏差。通常是1 個(gè)或半個(gè)最小數(shù)字量的模擬變化量,表示為1LSB、1/2LSB。

在轉(zhuǎn)化過程中,由于存在量化誤差和系統(tǒng)誤差,精度會(huì)有所損失。其中量化誤差對(duì)于精度的影響是可計(jì)算的,它主要決定于A/D轉(zhuǎn)換器件的位數(shù)。

3、采樣速率(Input Sampling Rate)單位是SPS,如果ADC的采樣頻率是Fs(Hz),那么它可以轉(zhuǎn)換的模擬信號(hào)帶寬至多是Fs/2(Hz)。比如1Msps代表著1M Samples Per Second,對(duì)應(yīng)的ADC的采樣頻率就是1MHz,可以轉(zhuǎn)換的模擬信號(hào)帶寬至多是1/2MHz。

3、功耗 Power Diss 單位 mW;

4、噪聲 Chip Noise 單位 Vrms 均方根;

5、溫漂 Temperature Drift 單位 ppm/℃;

6、實(shí)際精度 ENOB ADC 輸出的信號(hào)位數(shù) 單位 比特;

7、信噪比 SNR 單位分貝。

ADC的選型指標(biāo)

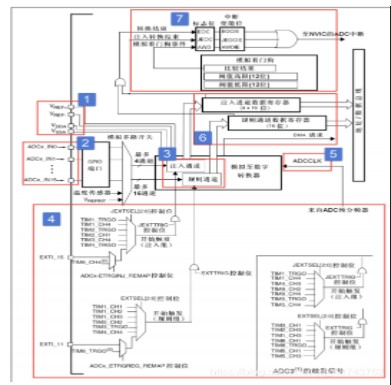

?采樣精度—— 即分辨率,一般有10位、12位、16位等;

?轉(zhuǎn)換時(shí)間—— 即每次采樣所需的時(shí)間,表征 ADC 的轉(zhuǎn)換速度,與 ADC 的時(shí)鐘頻率、采樣周期、轉(zhuǎn)換周期有關(guān);

?數(shù)據(jù)輸出方式—— 如并口輸出、串口輸出;

?ADC類型—— 不同類型的 ADC 有不同的性能極限;

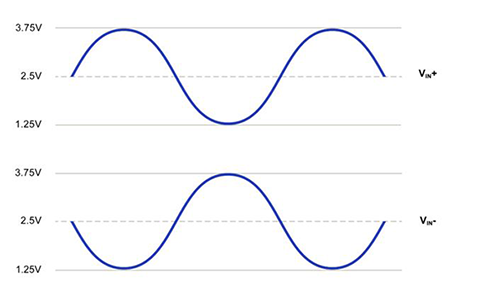

?工作電壓—— 需要注意 ADC 的工作電壓范圍、能否直接測(cè)量負(fù)電壓等;

?芯片封裝—— 芯片封裝是否符合產(chǎn)品設(shè)計(jì)要求;

?性價(jià)比—— 控制成本。

最主要的依據(jù)還是速度和精度。

目前ADC芯片的存在形式多種多樣:

1、傳統(tǒng)封裝片、集成電路;

2、ADC IP存在于各種SOC芯片中;

3、ADC集成模擬芯片(SIP),存在于各類數(shù)字傳感器芯片。

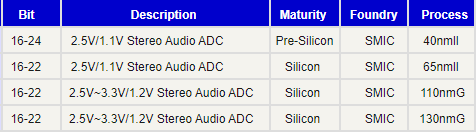

可見ADC IP應(yīng)用廣泛,致力于此的廠商也不在少數(shù)。

Archband、Faraday、銳成芯微等公司提供優(yōu)質(zhì)的AMBA IP產(chǎn)品。

部分工藝展示

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論