在PCB設(shè)計(jì)過(guò)程中,PCB過(guò)孔設(shè)計(jì)是經(jīng)常用到的一種方式,同時(shí)也是一個(gè)重要因素,但是過(guò)孔設(shè)計(jì)勢(shì)必會(huì)對(duì)信號(hào)完整性產(chǎn)生一定的影響,尤其是對(duì)高速PCB設(shè)計(jì)。本文在參閱一些相關(guān)資料,及在設(shè)計(jì)過(guò)程中的心得,對(duì)過(guò)孔進(jìn)行了一些簡(jiǎn)單的分析,希望能作為硬件設(shè)計(jì)人員的參考。

2022-10-25 18:02:02 5528

5528

在設(shè)計(jì)電子線路時(shí),比較多考慮的是產(chǎn)品的實(shí)際性能,而不會(huì)太多考慮產(chǎn)品的電磁兼容特性和電磁騷擾的抑制及電磁抗干擾特性,為了達(dá)到其兼容目的會(huì)在實(shí)際PCB設(shè)計(jì)中可采用以下電路措施: (1)為每個(gè)集成電路設(shè)一

2017-03-16 09:46:27

的PCB設(shè)計(jì)之電容量和耐壓。2.RC充放電回路電路是以一個(gè)RC充放電回路示意圖。假設(shè)PCB設(shè)計(jì)之電容器兩端的初始電壓為零,開(kāi)關(guān)K與1端接通的瞬間,電源通過(guò)電阻R對(duì)PCB設(shè)計(jì)之電容器充電,此時(shí)PCB設(shè)計(jì)之

2019-08-13 10:49:30

為什么我在分析運(yùn)放電路的時(shí)候總是會(huì)被電容影響,有了電容我就不會(huì)分析了(1)C2C3C4分別有什么作用?(2)C2C3C4在分析時(shí)可不可以看成斷開(kāi)?(3)第一個(gè)運(yùn)放的輸入級(jí)為什么要級(jí)聯(lián)3個(gè)68K電阻

2019-05-29 21:30:34

分析電流檢測(cè)運(yùn)放電路,輸入電流I和輸出電壓Vout的關(guān)系

2023-08-21 22:01:00

輸入端視為等電位,這一特性稱(chēng)為虛假短路,簡(jiǎn)稱(chēng)虛短。顯然不能將兩輸入端真正短路。那么在電路設(shè)計(jì)中,如何分析虛斷與虛短運(yùn)放電路呢?

2019-03-27 09:39:16

運(yùn)放電路,好像還有一些用,需要的來(lái)下載吧

2015-04-04 22:44:03

1、在PCB設(shè)計(jì)時(shí),芯片電源處旁路濾波等電容應(yīng)盡可能的接近器件,典型距離是小于3MM。 2、運(yùn)算放大器芯片電源處的小陶瓷旁路電容在放大器處于輸入高頻信號(hào)時(shí)可以為放大器的高頻特性提供能量電容值

2018-09-21 16:41:50

運(yùn)放電路PCB設(shè)計(jì)技巧

2020-12-29 07:50:05

本帖最后由 gk320830 于 2015-3-4 20:20 編輯

運(yùn)放電路是模擬電路中最基本的電路,也是每個(gè)工程師必須要掌握的電路!!

2012-07-27 20:13:54

運(yùn)放電路中的相位補(bǔ)償

2021-03-17 07:04:41

在網(wǎng)上找到的電路圖,請(qǐng)問(wèn)上下兩個(gè)電路圖中運(yùn)放輸出的Vref有什么不同我自己分析輸出的Vref是由輸出的負(fù)載Rref(圖上沒(méi)有)決定,上圖中的運(yùn)放輸出端允許被抬到VEE+12V,而下圖的運(yùn)放輸出則為固定5V。但不懂如何定性定量的分析電路,還請(qǐng)前輩幫忙分析一下,謝謝。

2019-01-07 11:03:16

常見(jiàn)外部噪聲源運(yùn)放電路如何降噪

2021-02-26 06:03:22

運(yùn)放電路的七大應(yīng)用場(chǎng)景

2021-03-11 07:49:46

在本系列中,我們將采用稱(chēng)為T(mén)INA的通用SPICE仿真軟件來(lái)分析運(yùn)放電路的穩(wěn)定性并給出相應(yīng)的結(jié)果。通常將此軟件稱(chēng)為T(mén)ina SPICE,您可以在www.designsoftware.com 上找到它

2021-04-06 08:36:30

各位前輩好,小弟初學(xué)開(kāi)關(guān)電源知識(shí),在學(xué)習(xí)電路過(guò)程中,遇到一個(gè)運(yùn)放電路(如圖所示),不是很理解。這應(yīng)該是一個(gè)反向比例放大器沒(méi)錯(cuò),可是電路中C54,C50以及R101各起什么作用呢,麻煩各位前輩不吝賜教,感激不盡~~

2015-12-10 10:36:27

此運(yùn)放電路怎么計(jì)算啊,求解答

2014-08-26 18:39:05

運(yùn)放電路輸出怎么計(jì)算

2021-08-23 11:57:19

電路如下,運(yùn)放電路,用手碰到電路板,運(yùn)放就會(huì)輸出一個(gè)很大的雜波,請(qǐng)問(wèn)各位大師怎么解決?放在不動(dòng)都是正常的,只要稍微碰到一點(diǎn)點(diǎn)電路板,就會(huì)輸出很大的雜波,碰到的地方?jīng)]有走線與覆銅,只是單純的PCB板材!

2016-03-01 14:10:43

循跡模塊上的LM324與LM339,哪個(gè)好些?跪求大神給一個(gè)LM324的滯回電壓比較器的proteus電路圖,急用!!!LM324D運(yùn)放電路故障分析LM324電感測(cè)量電路,預(yù)定的測(cè)量范圍為

2018-08-29 17:26:16

單獨(dú)的運(yùn)放電路好畫(huà),可怎么才能在原理圖中畫(huà)lm324的運(yùn)放電路,才能識(shí)別出dip14的封裝來(lái)啊,但是一個(gè)一個(gè)的運(yùn)放單獨(dú)畫(huà),由于運(yùn)放電路的管腳,這樣就不能得到lm的封裝了,請(qǐng)教高手指點(diǎn),是不是定義管腳啊,怎么定義啊

2009-02-11 19:35:34

1、很榮幸拿到這本《運(yùn)放電路環(huán)路穩(wěn)定性設(shè)計(jì) 原理分析、仿真計(jì)算、樣機(jī)測(cè)試》,花了幾天的時(shí)間瀏覽了一遍,書(shū)的內(nèi)容知識(shí)點(diǎn)很多,內(nèi)容確是非常豐富的,需要細(xì)細(xì)品味消化,需要對(duì)運(yùn)放有一點(diǎn)的了解,才能更加

2023-05-22 12:37:54

本帖最后由 松山歸人 于 2021-3-18 11:27 編輯

從虛斷,虛短分析基本運(yùn)放電路運(yùn)算放大器組成的電路五花八門(mén),令人眼花瞭亂,是模擬電路中學(xué)習(xí)的重點(diǎn)。在分析它的工作原理時(shí)常沒(méi)有抓住

2021-03-18 11:26:13

目前市場(chǎng)運(yùn)放種類(lèi)繁多,面對(duì)不同的使用條件和環(huán)境,是否都能選擇一樣的運(yùn)放呢?沒(méi)關(guān)系,這是很多電子工程師都會(huì)困惑的問(wèn)題,接下來(lái)為你揭開(kāi)運(yùn)放選型的神秘面紗。一、該如何分析運(yùn)放電路呢?在學(xué)習(xí)運(yùn)放選型前,我們

2021-09-08 06:00:00

對(duì)兩個(gè)運(yùn)放電路的原理分析不明白,希望論壇里的高手能指導(dǎo)一下,比如,電路中每個(gè)輸出點(diǎn)的電壓是多少以及原理是什么,希望各位的指導(dǎo)能讓我理解的更正確,更全面!

2016-03-30 17:11:48

這個(gè)電路左邊輸入,右邊輸出,請(qǐng)問(wèn)輸入和輸出什么關(guān)系。運(yùn)放學(xué)的不好,大家?guī)兔?b class="flag-6" style="color: red">分析一下。

2019-01-15 15:36:49

—05 單電源運(yùn)放電路實(shí)例從零學(xué)運(yùn)放—06 運(yùn)放中器件介紹&音頻功放電路從零學(xué)運(yùn)放—07 理想晶體管-運(yùn)放從零學(xué)運(yùn)放—08 積分電路_開(kāi)關(guān)電源等一些電路講解從零學(xué)運(yùn)放—09 電容電感PCB設(shè)計(jì)

2017-04-08 16:44:35

從零學(xué)運(yùn)放—02怎樣分析運(yùn)放電路分析運(yùn)放分兩個(gè)概念一個(gè)是虛短,一個(gè)是虛斷。最全最透徹運(yùn)放項(xiàng)目實(shí)戰(zhàn)視頻1、用虛短和虛斷分析運(yùn)放電路1.1、虛短負(fù)反饋環(huán)路下,同相輸入端電壓與反向輸入端電壓基本相當(dāng),像

2017-04-21 09:57:53

我最近使用multisim12仿真分析簡(jiǎn)單運(yùn)放電路的總輸出噪聲,電路圖如下所示,但是發(fā)現(xiàn)仿真輸出結(jié)果和自己根據(jù)運(yùn)放datasheet上的數(shù)據(jù)計(jì)算出來(lái)的結(jié)果相差很大。也不知道是不是我用錯(cuò)了,請(qǐng)問(wèn)該如何使用?求大神幫忙。

2016-03-25 17:19:32

從虛斷,虛短分析基本運(yùn)放電路運(yùn)算放大器組成的電路五花八門(mén),令人眼花瞭亂,是模擬電路中學(xué)習(xí)的重點(diǎn)。在分析它的工作原理時(shí)倘沒(méi)有抓住核心,往往令人頭大。

2019-06-18 06:00:00

源,用電路去生成負(fù)電源也是不劃算的,沒(méi)人會(huì)這么做。那么要用運(yùn)放的時(shí)候這么辦呢?----將雙電源運(yùn)放電路改為單電源運(yùn)放電路。那么如何做呢?產(chǎn)生一個(gè)虛地VCC/2:?jiǎn)坞娫垂ぷ鞯?b class="flag-6" style="color: red">運(yùn)放需要外部提供...

2021-12-27 07:10:45

在分析過(guò)程中,為什么運(yùn)放的反相輸入端電壓為0?求高人指點(diǎn)。

2014-04-15 16:45:41

各種運(yùn)放電路

2015-03-14 19:22:25

`這個(gè)電路接收12K的無(wú)線信號(hào),將其轉(zhuǎn)換為電壓輸出,求助大神們分析下每級(jí)運(yùn)放的功能,在下感激不盡`

2017-06-29 17:01:48

的設(shè)計(jì),復(fù)合反饋電路的設(shè)計(jì),都是很有用的設(shè)計(jì)思想和方法,如果能把各個(gè)圖的電路原理分析并且推導(dǎo)每個(gè)公式,會(huì)有受益的.最后的結(jié)論供大家在電路設(shè)計(jì)的時(shí)候參考.其實(shí)如何復(fù)雜的運(yùn)放電路都是由最基本的典型電路組成,理解運(yùn)用好了典型電路,也就用好了運(yùn)放,暫時(shí)是這么認(rèn)為的。 `

2011-07-23 09:43:36

`30個(gè)常用運(yùn)放電路供壇友學(xué)習(xí)點(diǎn)擊下載:[hide][/hide]`

2011-10-14 10:35:40

` 本帖最后由 weijianli000 于 2012-12-5 09:24 編輯

常用運(yùn)放電路集錦,希望對(duì)大家有幫助`

2012-12-05 09:22:42

一個(gè)拇指大小的運(yùn)放電路,4層PCB,雙運(yùn)放,約放大10000倍。因?yàn)樘砑悠帘握植环奖悖敲丛趺丛O(shè)計(jì)PCB可以提高這個(gè)PCB的抗輻射干擾,周?chē)性O(shè)備時(shí),總是有雜波。我的想法是,運(yùn)放往下4層,分別

2014-12-10 12:38:49

運(yùn)放的正負(fù)輸入級(jí)那里的C31和C20什么作用,還有前面一大堆電阻電容什么組合,還有這個(gè)運(yùn)放的放大倍數(shù)怎么算,麻煩大神幫我分析下電路,不勝感激

2017-01-16 11:44:48

接地問(wèn)題分析(PCB設(shè)計(jì))

2012-08-05 21:35:36

求大神幫分析一下運(yùn)放電路圖,運(yùn)放包含了正反饋和負(fù)反饋,不知道該怎么分析了,請(qǐng)老師指點(diǎn),感謝!

2019-05-31 04:03:32

大家用SIM900A免提運(yùn)放電路推薦下 謝謝

2019-01-10 10:25:33

電源噪聲對(duì)高頻 PC B 設(shè)計(jì)干擾分析隨著電子產(chǎn)品工作頻率的提高 ,高頻PCB設(shè)計(jì)越來(lái)越多,但與低頻PCB設(shè)計(jì) 相比出現(xiàn)了諸多干擾 ,總結(jié)起來(lái) 捷配在以來(lái)主要有電源噪聲、傳輸線干擾、耦合、電磁干擾

2018-09-13 14:59:30

作為電子工程師,運(yùn)算放大器算是很常見(jiàn)的一種IC了。那么,今天就說(shuō)說(shuō)運(yùn)放電路一些設(shè)計(jì)的細(xì)節(jié)內(nèi)容。本電子書(shū)將通過(guò)多款經(jīng)典電路的識(shí)圖分析及運(yùn)放參數(shù)的詳細(xì)解釋?zhuān)瑤ьI(lǐng)大家了解熟悉運(yùn)放電路,本電子書(shū)篇幅較長(zhǎng)

2020-06-04 16:00:15

本帖最后由 一只耳朵怪 于 2018-6-19 10:22 編輯

從虛斷,虛短分析基本運(yùn)放電路運(yùn)算放大器組成的電路五花八門(mén),令人眼花瞭亂,是模擬電路中學(xué)習(xí)的重點(diǎn)。在分析它的工作原理時(shí)倘沒(méi)有抓住

2018-06-14 18:09:16

!!!經(jīng)典運(yùn)放電路分析.pdf 2015-6-2 15:36 上傳 點(diǎn)擊文件名下載附件 428.62 KB, 下載次數(shù): 14 運(yùn)放資料

2018-07-19 02:08:40

這是一個(gè)運(yùn)放電路,我不太清楚是什么原理,請(qǐng)教各位老師解答,感謝!

2020-04-20 10:42:56

這個(gè)運(yùn)放電路怎么分析?

2019-09-12 02:27:42

各位老鐵,麻煩幫忙看看,這個(gè)運(yùn)放電路怎么分析?

2019-09-09 02:39:39

請(qǐng)教壇內(nèi)大佬,是否能分享跟隨運(yùn)放的電路圖并附上原理分析和計(jì)算方式。

2021-07-14 17:40:29

這個(gè)運(yùn)放電路是一個(gè)超聲波接收電路,最左邊的R1收到回波后轉(zhuǎn)換成脈沖,這個(gè)運(yùn)放電路實(shí)在是太復(fù)雜,看不懂啊,求大神給個(gè)計(jì)算式子什么的,我畢業(yè)答辯老師問(wèn)了,我回答的狗屁不通啊

2014-06-07 17:24:05

`高速電路PCB設(shè)計(jì)與EMC技術(shù)分析`

2017-09-21 21:31:03

`高速電路PCB設(shè)計(jì)與EMC技術(shù)分析資料大派感興趣的趕緊戳進(jìn)來(lái)瞧一瞧吧:http://www.tjjbhg.com/soft/22/163/2015/20150514371002.html `

2015-05-15 12:24:54

高速電路信號(hào)完整性分析與設(shè)計(jì)—PCB設(shè)計(jì)多層印制板分層及堆疊中應(yīng)遵徇的基本原則;電源平面應(yīng)盡量靠近接地平面。布線層應(yīng)安排與映象平面層相鄰。重要信號(hào)線應(yīng)緊臨地層。[hide] [/hide][此貼子已經(jīng)被作者于2009-9-12 10:38:14編輯過(guò)]

2009-09-12 10:37:02

:從虛斷,虛短分析基本[url=https://bbs.elecfans.com/jishu_200255_1_1.html]:從虛斷,虛短分析基本運(yùn)放電路 運(yùn)放電路[/url]

2012-09-23 15:42:16

介紹了采用Protel99SE進(jìn)行射頻電路PCB設(shè)計(jì)的設(shè)計(jì)流程,為了保證電路的性能,在進(jìn)行射頻電路PCB設(shè)計(jì)時(shí)應(yīng)考慮電磁兼容性,因而重點(diǎn)討論了元器件的布局與布線原則來(lái)達(dá)到電磁兼容的

2009-03-25 15:37:39 0

0 高速PCB設(shè)計(jì)中的串?dāng)_分析與控制:物理分析與驗(yàn)證對(duì)于確保復(fù)雜、高速PCB板級(jí)和系統(tǒng)級(jí)設(shè)計(jì)的成功起到越來(lái)越關(guān)鍵的作用。本文將介紹在信號(hào)完整性分析中抑制和改善信號(hào)串?dāng)_的

2009-06-14 10:02:38 0

0 介紹采用Protel99 SE進(jìn)行射頻電路PCB設(shè)計(jì)的流程。為保證電路性能,在進(jìn)行射頻電路PCB設(shè)計(jì)時(shí)應(yīng)考慮電磁兼

2006-04-16 22:17:22 1352

1352 高頻電路pcb設(shè)計(jì)

2008-08-14 21:37:43 926

926 RF電路PCB設(shè)計(jì)

介紹采用Protel99 SE進(jìn)行射頻電路PCB設(shè)計(jì)的流程。為保證電路性能,在進(jìn)

2009-01-18 13:16:53 983

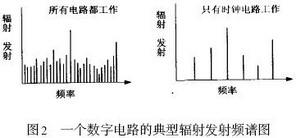

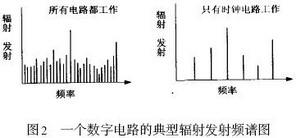

983 差模輻射和輻射抗擾性在PCB設(shè)計(jì)中的分析

在印制電路板設(shè)計(jì)階段進(jìn)行電磁兼容性(EMC)設(shè)計(jì)非常重要。分析了引起數(shù)字差模輻射干

2009-10-07 16:34:20 1767

1767

PCB設(shè)計(jì)時(shí)怎樣抗靜電放電

靜電對(duì)于精密的半導(dǎo)體芯片會(huì)造成各種損傷,例如穿透元器件內(nèi)部薄的絕緣層;損毀MOSFET和CMOS元器件的柵極

2010-03-13 14:55:50 1661

1661 信號(hào)完整性分析及其在高速PCB設(shè)計(jì)中的應(yīng)用,教你如何設(shè)計(jì)高速電路。

2016-04-06 17:29:45 15

15 在分析運(yùn)放電路工作原理時(shí),從虛斷,虛短分析基本運(yùn)放電路。

2016-05-10 14:24:39 101

101 RF電路的PCB設(shè)計(jì)技巧。

2016-05-17 11:09:40 10

10 基于信號(hào)完整性分析的PCB設(shè)計(jì)流程如圖所示。 主要包含以下步驟: 圖基于信號(hào)完整性分析的高速PCB設(shè)計(jì)流程 (1)因?yàn)檎麄€(gè)設(shè)計(jì)流程是基于信號(hào)完整性分析的,所以在進(jìn)行PCB設(shè)計(jì)之前,必須建立或獲取高速

2017-12-04 10:46:30 0

0 高速電路PCB設(shè)計(jì)與EMC技術(shù)分析.pdf

2021-11-21 10:09:40 0

0 高速電路信號(hào)完整性分析與設(shè)計(jì)—PCB設(shè)計(jì)1

2022-02-10 17:31:51 0

0 高速電路信號(hào)完整性分析與設(shè)計(jì)—PCB設(shè)計(jì)2

2022-02-10 17:34:49 0

0 在設(shè)計(jì)的時(shí)候都需要考慮清楚,這樣才能事半功倍。但實(shí)際情況往往是:在PCB設(shè)計(jì)后進(jìn)行電路實(shí)物板生產(chǎn),通常會(huì)因?yàn)樵O(shè)計(jì)與生產(chǎn)設(shè)備的工藝制成不匹配,導(dǎo)致設(shè)計(jì)好的PCB板無(wú)法生

2022-09-30 09:42:25 1104

1104

在設(shè)計(jì)的時(shí)候都需要考慮清楚,這樣才能事半功倍。但實(shí)際情況往往是:在PCB設(shè)計(jì)后進(jìn)行電路實(shí)物板生產(chǎn),通常會(huì)因?yàn)樵O(shè)計(jì)與生產(chǎn)設(shè)備的工藝制成不匹配,導(dǎo)致設(shè)計(jì)好的PCB板無(wú)法生產(chǎn)成實(shí)物電路板。因此,設(shè)計(jì)工程師在設(shè)計(jì)過(guò)

2022-09-30 11:45:28 12

12 射頻電路PCB設(shè)計(jì)

2022-12-30 09:21:27 15

15 PCB設(shè)計(jì)之高速電路

2023-12-05 14:26:22 288

288

射頻(Radio Frequency,RF)電路在現(xiàn)代電子領(lǐng)域中扮演著至關(guān)重要的角色,涵蓋了廣泛的應(yīng)用,從通信系統(tǒng)到雷達(dá)和射頻識(shí)別(RFID)等。在高速PCB設(shè)計(jì)中,射頻電路的分析和處理是一項(xiàng)具有

2023-11-30 07:45:01 316

316

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論