筆者擬通過(guò)系列文章,以“結(jié)構(gòu)-行為-績(jī)效”的分析框架對(duì)低功耗廣域網(wǎng)絡(luò)產(chǎn)業(yè)進(jìn)行初步分析,本文先對(duì)低功耗廣域網(wǎng)絡(luò)的市場(chǎng)結(jié)構(gòu)進(jìn)行梳理,并且將分析企業(yè)行為和市場(chǎng)績(jī)效。

2016-09-14 10:33:26 2875

2875 數(shù)據(jù)透?jìng)魇沁x擇低功耗WiFi模塊還是低功耗藍(lán)牙模塊好?

2021-01-04 06:55:35

作者:Scott低功耗的射頻技術(shù)正在飛奔著進(jìn)入人們的生活。像我們乘坐公交時(shí)使用的公交卡,方便大家隨時(shí)隨地上網(wǎng)的無(wú)線(xiàn)路由器,以及大紅大紫的任天堂Wii游戲機(jī)的無(wú)線(xiàn)手柄,這些工具/產(chǎn)品背后無(wú)不有低功耗

2019-07-15 08:03:56

低功耗的射頻技術(shù)正在飛奔著進(jìn)入人們的生活。像我們乘坐公交時(shí)使用的公交卡,方便大家隨時(shí)隨地上網(wǎng)的無(wú)線(xiàn)路由器,以及大紅大紫的任天堂Wii游戲機(jī)的無(wú)線(xiàn)手柄,這些工具/產(chǎn)品背后無(wú)不有低功耗無(wú)線(xiàn)射頻技術(shù)的身影

2019-07-12 08:05:43

Altera公司產(chǎn)品和企業(yè)市場(chǎng)副總裁DannyBiran低功耗是一種戰(zhàn)略?xún)?yōu)勢(shì) 在器件的新應(yīng)用上,F(xiàn)PGA功耗和成本結(jié)構(gòu)的改進(jìn)起到了非常重要的作用。Altera針對(duì)低功耗,同時(shí)對(duì)體系結(jié)構(gòu)和生產(chǎn)工藝進(jìn)行

2019-07-16 08:28:35

計(jì)算,云端則需要基于人工智能來(lái)實(shí)現(xiàn)數(shù)據(jù)建模與分析,并且最終能夠決策和執(zhí)行。從低功耗無(wú)線(xiàn)網(wǎng)絡(luò)可以知道,由于應(yīng)用場(chǎng)景具有復(fù)雜性,并不是一個(gè)網(wǎng)絡(luò)可以適用所有的應(yīng)用場(chǎng)景,在未來(lái)很長(zhǎng)一段之間之內(nèi),多個(gè)網(wǎng)絡(luò)可以共存,最終,只有具備安全性的通行技術(shù)可以適應(yīng)物聯(lián)網(wǎng)的發(fā)展。`

2020-04-27 22:01:13

本人一直從事于低功耗產(chǎn)品的研發(fā)應(yīng)用領(lǐng)域,先后就職于國(guó)內(nèi)上市通信技術(shù)公司,以及知名穿戴產(chǎn)品硬件公司。在工作的過(guò)程中,也接觸過(guò)各種功耗測(cè)試儀,或者叫功耗分析儀,說(shuō)白了,這些測(cè)試設(shè)備就是能夠正確的檢測(cè)

2020-12-28 22:59:20

可穿戴設(shè)備可分為哪幾類(lèi)?低功耗藍(lán)牙技術(shù)在可穿戴電子中有什么應(yīng)用?

2021-05-24 07:16:07

的自放電特性也需要予以考慮,常溫下儲(chǔ)存,每年容量損失小于 2%。這些因素在計(jì)算工作時(shí)間時(shí)也需要予以考慮。 低功耗藍(lán)牙如何實(shí)現(xiàn)低功耗和傳統(tǒng)藍(lán)牙技術(shù)相比,低功耗藍(lán)牙技術(shù)功耗方面的降低主要得益于以下幾個(gè)方面

2018-02-06 15:32:54

功能,比如連接手機(jī)與藍(lán)牙音箱、開(kāi)車(chē)時(shí)的免提電話(huà)、兩臺(tái)筆記本電腦之間共享文件以及連接游戲機(jī)與支持藍(lán)牙的游戲控制器等。低功耗藍(lán)牙:低功耗藍(lán)牙是一種智能、低功耗的藍(lán)牙無(wú)線(xiàn)技術(shù)。這項(xiàng)技術(shù)通過(guò)縮小智能設(shè)備的尺寸

2018-12-22 10:58:05

可重構(gòu)體系結(jié)構(gòu)分為哪幾種?典型動(dòng)態(tài)可重構(gòu)系統(tǒng)結(jié)構(gòu)有哪幾種?動(dòng)態(tài)可重構(gòu)系統(tǒng)有哪些應(yīng)用實(shí)例?

2021-04-28 06:13:00

可重構(gòu)體系的結(jié)構(gòu)是由哪些部分組成的?可重構(gòu)制造系統(tǒng)有哪些應(yīng)用?

2021-09-30 06:18:17

在天線(xiàn)的方向圖可重構(gòu)方面,目前的研究主要集中在采用八木形式的結(jié)構(gòu)上。即通過(guò)開(kāi)關(guān)控制來(lái)改變反射器或引向器的有效諧振長(zhǎng)度,從而實(shí)現(xiàn)反射或者引向作用,使天線(xiàn)的輻射方向發(fā)生變化。但是,這種方式需要多個(gè)天線(xiàn)

2019-07-31 08:01:51

°天線(xiàn)廣闊,而且其小區(qū)之間的零點(diǎn)指標(biāo)也比不上90°天線(xiàn)。 較普通的90度水平波束天線(xiàn)來(lái)講,具有三自由度的可重構(gòu)波束天線(xiàn)采用多陣列結(jié)構(gòu),能夠形成優(yōu)秀的場(chǎng)圖和水平場(chǎng)圖滾降特性。設(shè)置在90°水平波束寬度

2019-06-11 07:31:19

可重構(gòu)計(jì)算技術(shù)在汽車(chē)電子領(lǐng)域的應(yīng)用前景可重構(gòu)計(jì)算技術(shù)在汽車(chē)電子領(lǐng)域面臨的問(wèn)題

2021-05-12 06:40:18

可重用機(jī)床編碼技術(shù)及重構(gòu)算法研究摘要:在產(chǎn)品開(kāi)發(fā)過(guò)程中80%的設(shè)計(jì)工作是在重用的基礎(chǔ)上進(jìn)行的。設(shè)計(jì)重用能夠縮短產(chǎn)品開(kāi)發(fā)周期、降低設(shè)計(jì)成本和避免重復(fù)性錯(cuò)誤。本文從可重用機(jī)床的模塊分析入手,詳細(xì)分析了可

2009-05-17 11:58:53

方法可以降低功耗。FPGA的類(lèi)型、IP核、系統(tǒng)設(shè)計(jì)、軟件算法、功耗分析工具及個(gè)人設(shè)計(jì)方法都會(huì)對(duì)產(chǎn)品功耗產(chǎn)生影響。值得注意的是,如果使用不當(dāng),有些方法反而會(huì)增加功耗,因此必須根據(jù)實(shí)際情況選擇適當(dāng)?shù)脑O(shè)計(jì)方法

2015-02-09 14:58:01

可重構(gòu)設(shè)計(jì)是指利用可重用的軟、硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計(jì)方法。FPGA器件可多次重復(fù)配置邏輯的特性使可重構(gòu)系統(tǒng)成為可能,使系統(tǒng)兼具靈活、便捷、硬件資源可復(fù)用等性能

2011-05-27 10:22:36

結(jié)合采用低功耗元件和低功耗設(shè)計(jì)技術(shù)在目前比以往任何時(shí)候都更有價(jià)值。隨著元件集成更多功能,并越來(lái)越小型化,對(duì)低功耗的要求持續(xù)增長(zhǎng)。當(dāng)把可編程邏輯器件用于低功耗應(yīng)用時(shí),限制設(shè)計(jì)的低功耗非常重要。如何減小動(dòng)態(tài)和靜態(tài)功耗?如何使功耗最小化?

2019-08-27 07:28:24

關(guān)于低功耗的問(wèn)題就比較棘手了,比如某些可以低到微安級(jí)的MCU微控制器,而自己設(shè)計(jì)的低功耗怎么測(cè)都是毫安級(jí)的,電流竟然能夠高出標(biāo)準(zhǔn)幾百到上千倍,遇到這種情況干萬(wàn)不要怕,只要認(rèn)真你就贏了。接著仔細(xì)分析一下這其中的原因。

2020-12-30 06:55:55

本帖最后由 mr.pengyongche 于 2013-4-30 03:24 編輯

通用微處理器具有良好的接口功能,便于構(gòu)建可重構(gòu)系統(tǒng)。按照MPU與FPGA之間的相互關(guān)系以及在系統(tǒng)中所起的作用,主要可以分為兩類(lèi):MPU控制FPGA工作的可重構(gòu)系統(tǒng)和MPU協(xié)同F(xiàn)PGA工作的可重構(gòu)系統(tǒng)

2011-05-27 10:29:16

無(wú)線(xiàn)通信的全球標(biāo)準(zhǔn)。低功耗藍(lán)牙繼承了傳統(tǒng)藍(lán)牙技術(shù)良好的互操作性特點(diǎn),可確保不同廠(chǎng)商的低功耗藍(lán)牙芯片與設(shè)備之間的兼容性;可以使用紐扣電池供電,可實(shí)現(xiàn)以往難以實(shí)現(xiàn)的嵌入式應(yīng)用。在一顆傳統(tǒng)藍(lán)牙芯片的基礎(chǔ)上

2013-09-17 10:58:42

stm32進(jìn)入低功耗之后外部iic連接的芯片不能工作是什么原因?求大神指點(diǎn)!!!順便有三種低功耗設(shè)置代碼可附上。謝謝!!!

2017-04-25 21:13:03

FPGA可重構(gòu)設(shè)計(jì)的基礎(chǔ)是什么?基于FPGA的可重構(gòu)系統(tǒng)結(jié)構(gòu)是怎樣構(gòu)成的?基于FPGA的可重構(gòu)系統(tǒng)的應(yīng)用有哪些?

2021-04-30 07:16:04

,這樣的范圍可以讓一個(gè)房子里所有的智能燈通過(guò)一個(gè)星形拓?fù)?b class="flag-6" style="color: red">結(jié)構(gòu)與中央集線(xiàn)器通信,而不是較為復(fù)雜、且常用于提高低功耗無(wú)線(xiàn)技術(shù)范圍的網(wǎng)狀網(wǎng)絡(luò)。通過(guò)使用可檢測(cè)和修復(fù)接收器中通信錯(cuò)誤的前向糾錯(cuò)功能 (FEC

2017-05-02 15:45:38

結(jié)合采用低功耗元件和低功耗設(shè)計(jì)技術(shù)在目前比以往任何時(shí)候都更有價(jià)值。隨著元件集成更多功能,并越來(lái)越小型化,對(duì)低功耗的要求持續(xù)增長(zhǎng)。當(dāng)把可編程邏輯器件用于低功耗應(yīng)用時(shí),限制設(shè)計(jì)的低功耗非常重要。本文將討論減小動(dòng)態(tài)和靜態(tài)功耗的各種方法,并且給出一些例子說(shuō)明如何使功耗最小化。

2019-07-12 06:38:08

由于可重構(gòu)系統(tǒng)的研究歷史很短,目前尚未形成標(biāo)準(zhǔn)的結(jié)構(gòu)形式,在此僅根據(jù)已有的應(yīng)用做初步分析。 按重構(gòu)的粒度和方式,可重構(gòu)系統(tǒng)可以粗略地分為兩種。一種是粗粒度重構(gòu)單元的模塊級(jí)重構(gòu),即重構(gòu)時(shí)改變

2011-05-27 10:24:20

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運(yùn)算情況重組自身資源,實(shí)現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計(jì)算技術(shù)。動(dòng)態(tài)可重構(gòu)技術(shù)可快速實(shí)現(xiàn)器件的邏輯重建,它的出現(xiàn)為處理大規(guī)模計(jì)算問(wèn)題提供了一種兼具通用處理器靈活性

2019-07-10 07:56:06

大家好有誰(shuí)對(duì)FPGA的動(dòng)態(tài)可重構(gòu)有研究嗎?本人現(xiàn)在在搞這塊尋人共同探討。。。謝謝

2014-03-10 16:03:58

可重構(gòu)技術(shù)是指利用可重用的軟硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計(jì)方法。常規(guī)SRAM工藝的FPGA都可以實(shí)現(xiàn)重構(gòu),那我們具體該怎么做呢?

2019-08-09 07:35:02

,智能化方向邁進(jìn)。改變以往由儀器 生產(chǎn)廠(chǎng)家定義儀器功能、用戶(hù)只能使用的局面,使用戶(hù)可自定義儀器、根據(jù)不同測(cè)試需求對(duì)儀器進(jìn)行重構(gòu),已經(jīng)成為現(xiàn)代測(cè)試技術(shù)發(fā)展的一個(gè)重要方面。由于其能夠大大減少測(cè)試設(shè)備 的維修成本、提高資源利用率,可重構(gòu)儀器技術(shù)已引起高度重視。

2019-08-15 06:57:25

如何利用Freeze技術(shù)的FPGA實(shí)現(xiàn)低功耗設(shè)計(jì)?

2021-04-29 06:27:52

和傳統(tǒng)藍(lán)牙技術(shù)相比,低功耗藍(lán)牙技術(shù)的低功耗是如何實(shí)現(xiàn)的?

2021-05-18 06:23:30

怎樣去分析可重構(gòu)系統(tǒng)中軟/硬件任務(wù)間通信?什么是可重構(gòu)系統(tǒng)中消息隊(duì)列通信機(jī)制?如何對(duì)可重構(gòu)系統(tǒng)中任務(wù)間的通信機(jī)制進(jìn)行模擬實(shí)驗(yàn)?

2021-04-27 06:03:34

如何用可重構(gòu)射頻前端簡(jiǎn)化LTE設(shè)計(jì)復(fù)雜性?

2021-05-24 07:10:08

您好,我是新手用FPGA設(shè)計(jì)可重構(gòu)硬件。我只是想了解它。誰(shuí)能給我一些建議?哪些書(shū)籍文件適合我參考?網(wǎng)站或論壇也不錯(cuò)。謝謝?

2020-06-11 10:05:15

一種基于NiosⅡ的可重構(gòu)DSP系統(tǒng)設(shè)計(jì)

2021-03-17 06:41:55

如何降低可重構(gòu)系統(tǒng)的整體功耗?有什么方法能使可重構(gòu)系統(tǒng)的性能和功耗需求之間達(dá)到平衡?

2021-04-08 07:09:23

可重構(gòu)技術(shù)具有什么優(yōu)點(diǎn)?怎么實(shí)現(xiàn)基于FPGA可重構(gòu)智能儀器的設(shè)計(jì)

2021-05-06 06:44:38

本文提出的通過(guò)微處理器加FPGA結(jié)合串行菊花鏈實(shí)現(xiàn)可重構(gòu)的方式,實(shí)現(xiàn)了動(dòng)態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計(jì)的一種應(yīng)用。

2021-05-10 06:22:19

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運(yùn)算情況重組自身資源,實(shí)現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計(jì)算技術(shù)。動(dòng)態(tài)可重構(gòu)技術(shù)可快速實(shí)現(xiàn)器件的邏輯重建,它的出現(xiàn)為處理大規(guī)模計(jì)算問(wèn)題提供了一種兼具通用處理器靈活性和ASIC電路高速性的解決方案。

2019-08-13 07:56:00

提出了一種可用于手持移動(dòng)終真?zhèn)€可重構(gòu)天線(xiàn)的設(shè)計(jì)方法。該天線(xiàn)安裝有兩個(gè)RF-PIN開(kāi)關(guān),可通過(guò)一個(gè)直流控制電路控制開(kāi)關(guān)的狀態(tài),以使 線(xiàn)的極化方式和輻射方向圖發(fā)生變化,從而實(shí)現(xiàn)極化可重構(gòu)和方向圖可重構(gòu)。該天線(xiàn)結(jié)構(gòu)緊湊,易于與電路板集成在一起,在移動(dòng)終端中有良好的應(yīng)用價(jià)值。

2019-09-26 07:49:45

近年來(lái),隨著FPGA技術(shù)的發(fā)展,支持重構(gòu)的FPGA器件新品迭現(xiàn)。Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表結(jié)構(gòu)。Xilinx支持模塊化動(dòng)態(tài)部分重構(gòu)的器件族有

2011-05-27 10:23:28

0 引言可重構(gòu)體系結(jié)構(gòu)已經(jīng)成為FPGA系統(tǒng)開(kāi)發(fā)的研究熱點(diǎn),并已有許多令人矚目的研究成果及產(chǎn)品應(yīng)用。FPGA可重構(gòu)的應(yīng)用為用戶(hù)提供了方便的系統(tǒng)升級(jí)模式,同時(shí)也實(shí)現(xiàn)了基于相同硬件系統(tǒng)的不同工作模式功能

2019-07-31 07:15:40

有關(guān)低功耗LVDT信號(hào)調(diào)理器的分析

2021-05-19 06:54:44

什么是可重構(gòu)技術(shù)? 它有哪些優(yōu)點(diǎn)?可重構(gòu)智能儀器的硬件怎樣去設(shè)計(jì)?可重構(gòu)智能儀器的軟件設(shè)計(jì)怎樣去設(shè)計(jì)?

2021-04-29 06:23:17

本文基于現(xiàn)代測(cè)控系統(tǒng)的通用化結(jié)構(gòu)特征和可重構(gòu)的現(xiàn)場(chǎng)可編程門(mén)陣列FPGA技術(shù)的發(fā)展,提出一種可重構(gòu)測(cè)控系統(tǒng)(Reconfigurable Mo—nitoring System,RMS)的設(shè)計(jì)構(gòu)想,并給出其應(yīng)用實(shí)例。

2021-04-30 06:40:43

功能模塊的平均使用率將下降。因此,系統(tǒng)設(shè)計(jì)應(yīng)該從傳統(tǒng)追求大規(guī)模、高密度的方向,轉(zhuǎn)向如何提高資源利用率,用有限的資源實(shí)現(xiàn)更大規(guī)模的邏輯設(shè)計(jì)上來(lái)。可重構(gòu)計(jì)算技術(shù)能夠提供硬件的效率和軟件的可編程性,它綜合了微處理器和ASIC的特點(diǎn),在空間維和時(shí)間維上均可變。

2019-09-11 11:52:43

,提出一種支持可重構(gòu)單元陣列快速容錯(cuò)的輔助布線(xiàn)電路,該電路結(jié)構(gòu)由二維的輔助布線(xiàn)模塊構(gòu)成,每個(gè)輔助布線(xiàn)模塊可以讀取并修改所在可重構(gòu)單元的可編程開(kāi)關(guān)配置數(shù)據(jù).可重構(gòu)單元陣列容錯(cuò)時(shí),輔助布線(xiàn)電路代替外部軟件執(zhí)行

2010-04-24 09:01:53

從制造過(guò)程開(kāi)始,一直到所有的應(yīng)用領(lǐng)域,極低功耗技術(shù)逐漸成為所有設(shè)計(jì)中必不可少的需求。對(duì)能源敏感的應(yīng)用,特別是必須以單顆電池提供連續(xù)數(shù)小時(shí)運(yùn)作時(shí)間的產(chǎn)品,更需要加入超低功耗設(shè)計(jì)概念。要滿(mǎn)足這些要求

2019-05-15 10:57:02

方法 通過(guò)分析功耗產(chǎn)生的原因,可以判斷降低功耗受到很多約束,需要在各個(gè)要素之間反復(fù)衡量。數(shù)字IC低功耗的設(shè)計(jì)應(yīng)該從頂層到底層各個(gè)階段進(jìn)行優(yōu)化,如工藝級(jí)低功耗技術(shù)、電路級(jí)低功耗技術(shù)、RTL級(jí)(寄存器

2020-07-07 11:40:06

本帖最后由 gk320830 于 2015-3-9 17:57 編輯

藍(lán)牙低功耗技術(shù) 藍(lán)牙低功耗技術(shù)是新一代的藍(lán)牙技術(shù),只要消耗的以前藍(lán)牙十分之一的能源就能做到一樣的效果!它將擴(kuò)大到很低功耗

2011-05-13 11:25:59

藍(lán)牙低功耗技術(shù) 藍(lán)牙低功耗技術(shù)是新一代的藍(lán)牙技術(shù),只要消耗的以前藍(lán)牙十分之一的能源就能做到一樣的效果!它將擴(kuò)大到很低功耗設(shè)備應(yīng)用,僅有很低的電池容量就可以使用很長(zhǎng)時(shí)間。藍(lán)牙低功耗的技術(shù)

2013-09-04 14:20:42

低功耗藍(lán)牙有哪些特性?低功耗藍(lán)牙有哪些技術(shù)?

2021-05-14 07:08:40

的重新安排卻只能降低5%的翻轉(zhuǎn)次數(shù)。在不同的低功耗設(shè)計(jì)層次,考慮的重點(diǎn)也不相同。比如說(shuō)只有在工藝級(jí)設(shè)計(jì)時(shí),設(shè)計(jì)者才考慮通過(guò)擴(kuò)散區(qū)的摻雜濃度來(lái)影響閾值電壓。近年來(lái),降低功耗的技術(shù)逐漸從電路層向結(jié)構(gòu)層,從

2013-05-16 20:00:33

,但只要涉及低功耗的問(wèn)題就比較棘手了,比如某些可以低到微安級(jí)的MCU,而自己設(shè)計(jì)的低功耗怎么測(cè)都是毫安級(jí)的,電流竟然能夠高出標(biāo)準(zhǔn)幾百到上千倍,遇到這種情況千萬(wàn)不要怕,只要認(rèn)真你就贏了。下邊咱們仔細(xì)分析一下這其中的原因。

2019-07-12 06:34:33

如何利用FPGA設(shè)計(jì)技術(shù)降低功耗?

2021-04-13 06:16:21

,Dialog半導(dǎo)體也是低功耗藍(lán)牙技術(shù)的領(lǐng)先創(chuàng)新廠(chǎng)商。對(duì)于國(guó)內(nèi)用戶(hù),大家所熟悉的小米手環(huán)里所使用的藍(lán)牙芯片就是Dialog的產(chǎn)品。除了低功耗藍(lán)牙產(chǎn)品,Dialog最近新推出了超低功耗的Wi-Fi芯片,貌似要在某些

2020-05-24 07:37:24

可重構(gòu)計(jì)算技術(shù)概述隨著20世紀(jì)80年代中期Xilinx公司推出其第一款現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)以來(lái),另一種實(shí)現(xiàn)手段——可重構(gòu)計(jì)算技術(shù)逐漸受到人們的重視,因?yàn)樗軌蛱峁┯布δ艿男屎蛙浖目删幊绦?隨著可編程器件容量根據(jù)摩爾定律的不斷增大和自動(dòng)設(shè)計(jì)技術(shù)的發(fā)展,可重構(gòu)技術(shù)正迅速地成熟起來(lái)。

2019-07-29 06:26:03

面向HID應(yīng)用的藍(lán)牙低功耗和專(zhuān)有射頻技術(shù)對(duì)比分析

2021-05-25 06:41:03

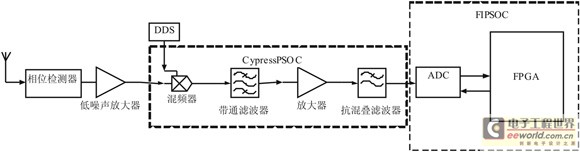

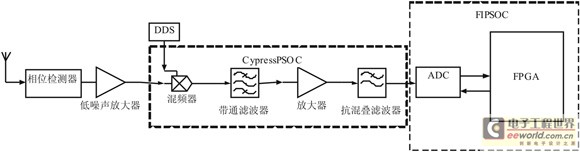

描述了一種低功耗擴(kuò)頻全雙工衛(wèi)星收發(fā)機(jī)通用基帶處理結(jié)構(gòu)。此構(gòu)架采用了一系列針對(duì)低功耗衛(wèi)星通信的優(yōu)化,包括頻域抗干擾算法、插值技術(shù)、頻域并行捕獲算法和雙級(jí)AGC技術(shù)

2010-11-26 18:13:27 18

18 動(dòng)態(tài)可重構(gòu)系統(tǒng)的通信結(jié)構(gòu)分析

動(dòng)態(tài)可重構(gòu)技術(shù)能在一定控制邏輯的驅(qū)動(dòng)下,對(duì)全部或部分邏輯資源實(shí)現(xiàn)在系統(tǒng)的動(dòng)態(tài)功能變換和硬

2009-03-29 15:12:52 909

909

PAD在接收機(jī)動(dòng)態(tài)可重構(gòu)結(jié)構(gòu)中的應(yīng)用設(shè)計(jì)

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運(yùn)算情況重組自身資源,實(shí)現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計(jì)算技術(shù)。動(dòng)態(tài)可重構(gòu)技術(shù)可快

2009-12-28 09:15:32 717

717

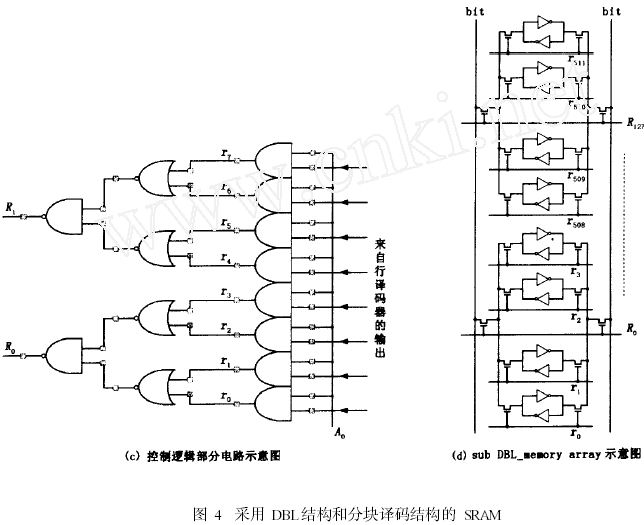

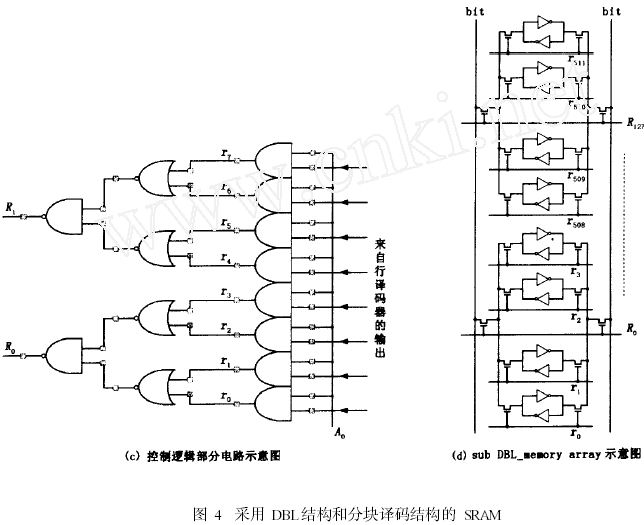

基于DBL結(jié)構(gòu)的嵌入式64kb SRAM的低功耗設(shè)計(jì)

針對(duì)嵌入式系統(tǒng)的低功耗要求,采用位線(xiàn)分割結(jié)構(gòu)和存儲(chǔ)陣列分塊譯碼結(jié)構(gòu),完成了64 kb低功耗SRAM模塊的設(shè)計(jì)。 與一般布局的

2010-01-12 10:03:47 983

983

低溫漂低功耗的帶隙基準(zhǔn)源技術(shù)設(shè)計(jì)

摘 要:設(shè)計(jì)一種低溫漂低功耗的帶隙基準(zhǔn)結(jié)構(gòu),在傳統(tǒng)帶隙基準(zhǔn)核心電路結(jié)構(gòu)上增加一對(duì)PNP管,兩個(gè)雙極型晶

2010-04-28 08:59:11 1332

1332

本文參照計(jì)算機(jī)存儲(chǔ)結(jié)構(gòu),利用虛擬存儲(chǔ)技術(shù),對(duì)存儲(chǔ)系統(tǒng)的結(jié)構(gòu)進(jìn)行了改進(jìn)。在DSP中引入二級(jí)Cache存儲(chǔ)器結(jié)構(gòu),在較小的硬件開(kāi)銷(xiāo)下提高了DSP的工作速度。結(jié)合高性能低功耗DSP cache設(shè)計(jì)

2011-12-10 16:25:52 2062

2062

現(xiàn)代高速處理器的設(shè)計(jì)中對(duì)于cache技術(shù)的研究已經(jīng)成為了提高處理器性能的關(guān)鍵技術(shù),本文針對(duì)在流水線(xiàn)結(jié)構(gòu)中采用非阻塞cache技術(shù)進(jìn)行分析研究,提高cache的命中率,降低缺少代價(jià),提高處理器的性能,并介紹了“龍騰”R2處理器的流水線(xiàn)結(jié)構(gòu)的非阻塞cache 的設(shè)計(jì)。

2015-12-28 09:54:57 8

8 的起源、應(yīng)用產(chǎn)品和技術(shù)發(fā)展歷程,并對(duì)低功耗藍(lán)牙的硬件結(jié)構(gòu),協(xié)議構(gòu)成,連接模式等技術(shù)特點(diǎn)進(jìn)行分析,并和當(dāng)前流行的無(wú)線(xiàn)通信技術(shù)進(jìn)行比較,闡明了低功耗藍(lán)牙技術(shù)的優(yōu)勢(shì)和特點(diǎn)。最后對(duì)低功耗藍(lán)牙的發(fā)展前景做出預(yù)測(cè)。

2017-09-13 17:21:29 14

14 基于SRAM的FPGA的問(wèn)世標(biāo)志著現(xiàn)代可重構(gòu)技術(shù)的開(kāi)端,并極大地推動(dòng)了其發(fā)展。可編程FPGA可以根據(jù)不同算法設(shè)計(jì)合理的硬件結(jié)構(gòu),以達(dá)到提高執(zhí)行效率的目的。動(dòng)態(tài)可重構(gòu)FPGA可以在程序運(yùn)行中動(dòng)態(tài)完成

2017-11-25 10:20:01 12296

12296

要實(shí)現(xiàn)可重構(gòu)Cache,首先Cache的結(jié)構(gòu)要支持運(yùn)行過(guò)程中的動(dòng)態(tài)劃分,其次要有檢測(cè) Cache命中率的硬件或者軟件機(jī)制,并且有相應(yīng)的動(dòng)態(tài)配置算法。

2018-07-17 09:09:00 1335

1335

更詳細(xì)的講,cache的結(jié)構(gòu)其實(shí)和內(nèi)存的結(jié)構(gòu)類(lèi)似,也包含地址和內(nèi)容,只是cache的內(nèi)容除了存的數(shù)據(jù)(data)之外,還包含存的數(shù)據(jù)的物理內(nèi)存的地址信息(tag),因?yàn)镃PU發(fā)出的尋址信息都是針對(duì)

2019-06-03 14:24:13 10851

10851

低功耗設(shè)計(jì)的實(shí)現(xiàn)是我們關(guān)注的焦點(diǎn),現(xiàn)代企業(yè)越來(lái)越注重低功耗。因?yàn)椋?b class="flag-6" style="color: red">低功耗往往能為器件帶來(lái)更好的性能。在前文中,小編對(duì)FPGA低功耗設(shè)計(jì)有所闡述。為增進(jìn)大家對(duì)低功耗的認(rèn)識(shí),本文將對(duì)基于Freeze技術(shù)的低功耗設(shè)計(jì)予以介紹。如果你對(duì)低功耗設(shè)計(jì)具有興趣,不妨繼續(xù)往下閱讀哦。

2021-02-14 17:50:00 1895

1895 本論文研究和分析了低功耗設(shè)計(jì)技術(shù)的背景、功耗的組成和降低功耗的方法途徑。目前主要是通過(guò)降低工作電壓、降低電容和減小活動(dòng)性來(lái)達(dá)到降低功耗的目的。低功耗設(shè)計(jì)大致分為系統(tǒng)結(jié)構(gòu)級(jí)、寄存器傳輸級(jí)、門(mén)級(jí)、電路

2021-04-13 16:49:37 19

19 本文會(huì)從結(jié)構(gòu),原理以及應(yīng)用方面對(duì) MPU 和 Cache 進(jìn)行分析,主要目的是希望讀者對(duì) Cache 有基本的了解,在具體的實(shí)際應(yīng)用中,使用帶有一級(jí) cache 的 MCU 時(shí),避免常見(jiàn)的錯(cuò)誤。

2022-09-28 11:05:20 0

0 FPGA上的可重構(gòu)技術(shù)根據(jù)FPGA芯片內(nèi)部的不同結(jié)構(gòu)可以分為兩種,分別是動(dòng)態(tài)可重構(gòu)和靜態(tài)可重構(gòu)。

2022-11-03 20:09:39 757

757

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論