電路描述

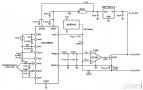

本應用中用到ADuCM360的下列特性:

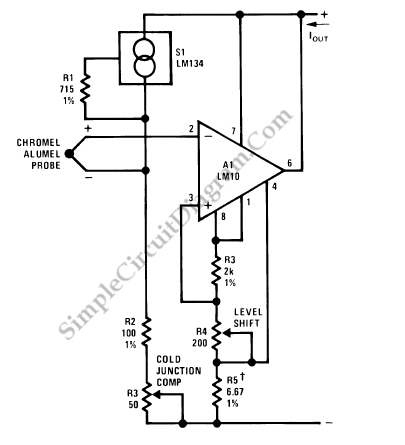

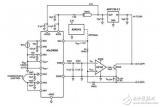

12位DAC輸出及其靈活的片內輸出緩沖器用于控制外部NPN晶體管BC548。通過控制此晶體管的VBE電壓,可將經過47Ω負載電阻的電流設置為所需的值。

DAC為12位單調式,但其輸出精度通常在3 LSB左右。此外,雙極性晶體管引入了線性誤差。為提高DAC輸出的精度并消除失調和增益端點誤差,ADC0會測量反饋電壓,從而反映負載電阻(RLOAD)兩端的電壓。根據此ADC0讀數,DAC輸出將通過源代碼糾正。這樣就針對4 mA至20 mA的輸出提供了±0.5°C的精度。

24位Σ-Δ 型ADC內置PGA,在軟件中為熱電偶和RTD設置32的增益。ADC1在熱電偶與RTD電壓采樣之間連續切換。

可編程激勵電流源驅動受控電流流過RTD。雙通道電流源可在0μA至2 mA范圍內以一定的階躍進行配置。本例使用200μA設置,以便將RTD自熱效應引起的誤差降至最小。

ADuCM360中的ADC內置了1.2 V基準電壓源。內部基準電壓源精度高,適合測量熱電偶電壓。

ADuCM360中ADC的外部基準電壓源。測量RTD電阻時,我們采用比率式設置,將一個外部基準電阻(RREF)連接在外部VREF+和VREF?引腳上。由于該電路中的基準電壓源為高阻抗,因此需要使能片內基準電壓輸入緩沖器。片內基準電壓緩沖器意味著無需外部緩沖器即可將輸入泄漏影響降至最低。

偏置電壓發生器(VBIAS)。VBIAS功能用于將熱電偶共模電壓設置為AVDD/2 (900 mV)。同樣,這樣便無需外部電阻,便可以設置熱電偶共模電壓。

ARM Cortex-M3內核。功能強大的32位ARM內核集成了126 KB閃存和8 KBSRAM存儲器,用來運行用戶代碼,可配置和控制ADC,并利用ADC將熱電偶和RTD輸入轉換為最終的溫度值。它還可以利用來自AIN9電壓電平的閉環反饋控制并持續監控DAC輸出。出于額外調試目的,它還可以控制UART/USB接口上的通信。

UART用作與PC主機的通信接口。這用于對片內閃存進行編程。它還可作為調試端口,用于校準DAC和ADC。

兩個外部開關用來強制該器件進入閃存引導模式。使 SD處于低電平,同時切換RESET按鈕, ADuCM360將進入引導模式,而不是正常的用戶模式。在引導模式下,通過UART接口可以對內部閃存重新編程。

J1連接器是一個8引腳雙列直插式連接器,與CN0300支持硬件隨附的USB-SWD/UART板相連。配合J-Link-Lite 板可對此應用電路板進行編程和調試。參見圖3。

熱電偶和RTD產生的信號均非常小,因此需要使用可編程增益放大器(PGA)來放大這些信號。

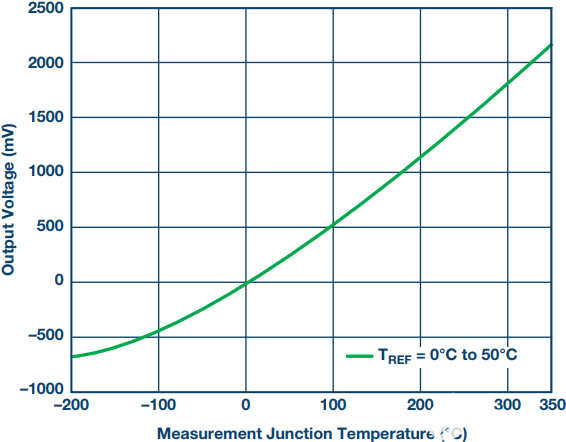

本應用使用的熱電偶為T型(銅-康銅),其溫度范圍為?200°C至+350°C,靈敏度約為40ΩV/°C,這意味著ADC在雙極性模式和32倍PGA增益設置下可以覆蓋熱電偶的整個溫度范圍。

RTD用于冷結補償。本電路使用的RTD為100Ω鉑RTD,型號為Enercorp PCS 1.1503.1。它采用0805表貼封裝,溫度變化率為0.385 Ω/°C。

注意,基準電阻RREF必須為精密5.6 kΩ (±0.1%)電阻。

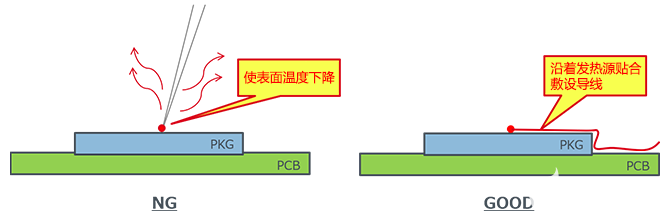

本電路必須構建在具有較大面積接地層的多層電路板(PCB)上。為實現最佳性能,必須采用適當的布局、接地和去耦技術(請參考 指南MT-031——“實現數據轉換器的接地并解開AGND和DGND的謎團”、 指南MT-101——“去耦技術”以及 ADuCM360TCZ評估板布局)。

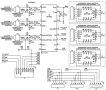

評估本電路所用的PCB如圖2所示。

圖2. 本電路所用的EVAL-CN0300-EB1Z板

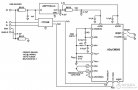

圖3. 連接至USB-SWD/UART板和SEGGER J-Link-Lite板的EVAL-CN0300-EB1Z板

圖3顯示了USB-SWD/UART板。此板用作PC USB端口的接口板。該USB端口可用于通過基于UART的下載器對器件進行編程。它也可用于連接PC上的COM端口(虛擬串行端口)。這是運行校準程序所需要的條件。

J-Link-Lite插入USB-SWD/UART板的20引腳連接器中。 J-Link-Lite提供代碼調試和編程支持。它通過另一個USB連接器連接至PC。

代碼說明

用于測試本電路的源代碼可從 ADuCM360 產品頁面下載 (zip壓縮文件)。源代碼使用示例代碼隨附的函數庫。圖4 顯示了利用KeilμVision4工具查看時項目中所用的源文件列表。

圖4. Vision4中查看的源文件

電子發燒友App

電子發燒友App

評論