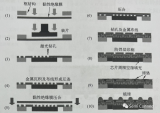

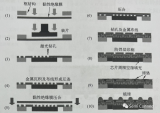

板級(jí)埋人式封裝是一種在基板制造工藝的基礎(chǔ)上融合芯片封裝工藝及 SMT工藝的集成封裝技術(shù),既可以是單芯片封裝、多芯片封裝,也可以是模組封裝、堆疊封裝。與傳統(tǒng)封裝中在基板表面貼裝芯片或元件不同,板級(jí)埋人式封裝直接將芯片或元件嵌人基板中間,因此它具有更短的互連路徑、更小的體積、更優(yōu)的電熱性能及更高的集成度。

2023-05-09 10:21:53 833

833

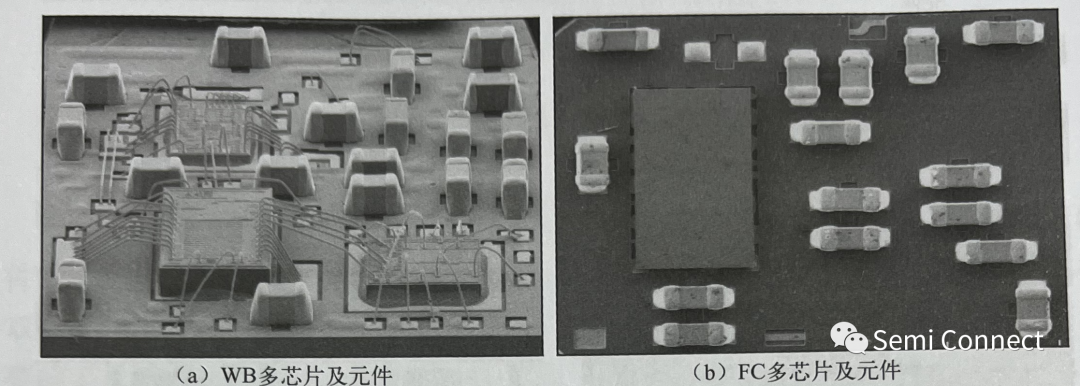

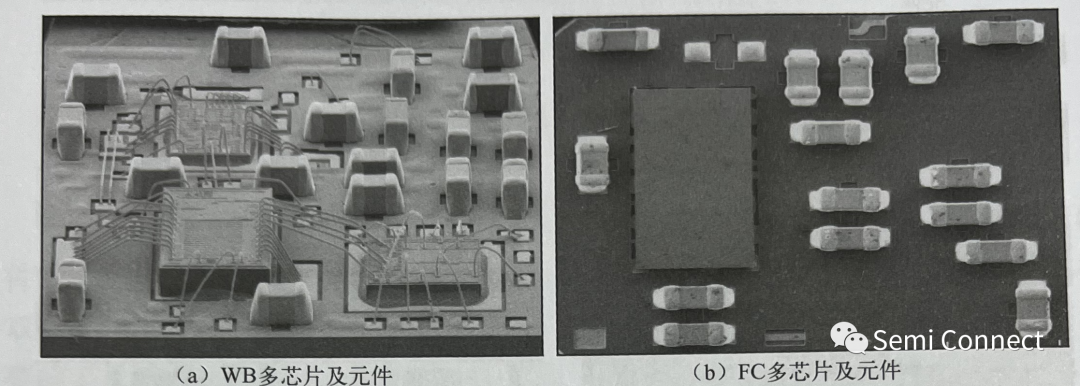

系統(tǒng)級(jí)封裝 (System in Package, SiP)是指將單個(gè)或多個(gè)芯片與各類(lèi)元件通過(guò)系統(tǒng)設(shè)計(jì)及特定的封裝工藝集成于單一封裝體或模塊,從而實(shí)現(xiàn)具完整功能的電路集成,如圖 7-115 所示

2023-05-10 16:54:32 829

829

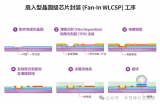

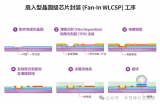

在上篇文章中介紹了扇入型晶圓級(jí)芯片封裝(Fan-In WLCSP)、扇出型晶圓級(jí)芯片封裝(Fan-Out WLCSP)、重新分配層(RDL)封裝、倒片(Flip Chip)封裝,這篇文章著重介紹硅通孔(TSV)封裝工藝。

2023-11-08 10:05:53 1827

1827

在本文中,我們將重點(diǎn)介紹半導(dǎo)體封裝的另一種主要方法——晶圓級(jí)封裝(WLP)。本文將探討晶圓級(jí)封裝的五項(xiàng)基本工藝,包括:光刻(Photolithography)工藝、濺射(Sputtering)工藝

2024-01-24 09:39:09 335

335

為適應(yīng)異構(gòu)集成技術(shù)的應(yīng)用背景,封裝天線(xiàn)的實(shí)現(xiàn)技術(shù)也應(yīng)有所變化,利用封裝工藝的優(yōu)點(diǎn)以實(shí)現(xiàn)更佳的性能。

2024-02-29 11:11:30 157

157

封裝技術(shù)與加密技術(shù)一.4大主流封裝技術(shù)半導(dǎo)體 封裝 是指將通過(guò)測(cè)試的晶圓按照產(chǎn)品型號(hào)及功能需求加工得到獨(dú)立芯片的過(guò)程。封裝技術(shù)是一種將集成電路用絕緣的塑料或陶瓷材料打包的技術(shù)。以CPU為例,實(shí)際看到

2022-01-25 06:50:46

以后到現(xiàn)在AiP技術(shù)在國(guó)內(nèi)外取得的最新成果。此外,本文也是作者介紹封裝天線(xiàn)技術(shù)系列文章的第二篇:譜新篇。文章首先從新聞發(fā)布、媒體報(bào)道及市場(chǎng)分析報(bào)告角度出發(fā)關(guān)注當(dāng)前AiP技術(shù)熱點(diǎn),接著追蹤研討會(huì)、捕捉AiP技術(shù)新的發(fā)展動(dòng)向,然后重點(diǎn)介紹AiP技術(shù)在材料、工藝、設(shè)計(jì)、測(cè)試等方面的新進(jìn)展。

2019-07-16 07:12:40

摘 要 :集成無(wú)源元件技術(shù)可以集成多種電子功能,具有小型化和提高系統(tǒng)性能的優(yōu)勢(shì),以取代體積龐大的分立無(wú)源元件.文章主要介紹了集成無(wú)源元件技術(shù)的發(fā)展情況,以及采用IPD薄膜技術(shù)實(shí)現(xiàn)電容.電阻和電感

2018-09-11 16:12:05

`本文指出了集成電源是電源技術(shù)發(fā)展的必然方向,目前混合封裝技術(shù)是集成電源模塊的主流方式,闡述了混合封裝技術(shù)的若干關(guān)鍵技術(shù)問(wèn)題和發(fā)展方向,最后介紹了若干基于混合封裝技術(shù)的集成電源模塊。`

2011-03-09 17:15:59

研究院(先進(jìn)電子封裝材料廣東省創(chuàng)新團(tuán)隊(duì))、上海張江創(chuàng)新學(xué)院、深圳集成電路設(shè)計(jì)產(chǎn)業(yè)化基地管理中心、桂林電子科技大學(xué)機(jī)電工程學(xué)院承辦的 “第二期集成電路封裝技術(shù) (IC Packaging

2016-03-21 10:39:20

` 集成電路按生產(chǎn)過(guò)程分類(lèi)可歸納為前道測(cè)試和后到測(cè)試;集成電路測(cè)試技術(shù)員必須了解并熟悉測(cè)試對(duì)象—硅晶圓。測(cè)試技術(shù)員應(yīng)該了解硅片的幾何尺寸形狀、加工工藝流程、主要質(zhì)量指標(biāo)和基本檢測(cè)方法;集成電路晶圓測(cè)試基礎(chǔ)教程ppt[hide][/hide]`

2011-12-02 10:20:54

《集成電路芯片封裝技術(shù)》是一本通用的集成電路芯片封裝技術(shù)通用教材,全書(shū)共分13章,內(nèi)容包括:集成電路芯片封裝概述、封裝工藝流程、厚膜與薄膜技術(shù)、焊接材料、印制電路板、元件與電路板的連接、封膠材料

2012-01-13 13:59:52

和其他LSI集成電路都起著重要的作用。新一代CPU的出現(xiàn)常常伴隨著新的封裝形式的使用。芯片的封裝技術(shù)已經(jīng)歷了好幾代的變遷,從DIP、QFP、PGA、BGA到CSP再到MCM,技術(shù)指標(biāo)一代比一代先進(jìn),包括

2018-08-28 11:58:30

集成電路芯片封裝技術(shù)知識(shí)詳解本電子書(shū)對(duì)封裝介紹的非常詳細(xì),所以和大家分享。因?yàn)樘螅瑳](méi)有上傳。請(qǐng)點(diǎn)擊下載。[此貼子已經(jīng)被作者于2008-5-12 22:45:41編輯過(guò)]

2008-05-12 22:44:28

《集成電路芯片封裝與測(cè)試技術(shù)》考試試卷試題 班級(jí): 學(xué)號(hào)姓名 題號(hào)一二三四總分 得分 一 一、填空題(每空格1分共18分)1、封裝工藝屬于集成電路制造工藝的工序。 2、按照器件

2012-01-13 11:23:00

。另一種方法稱(chēng)為陰極濺射,其中來(lái)自由所需薄膜材料制成的陰極的原子沉積在位于陰極和陽(yáng)極之間的基板上。厚膜集成電路它們通常也被稱(chēng)為印刷薄膜電路。通過(guò)使用稱(chēng)為絲網(wǎng)印刷技術(shù)的制造工藝在陶瓷物質(zhì)上獲得所需

2022-03-31 10:46:06

別告訴我把它打開(kāi),然后把那里面的庫(kù)提取出來(lái)。我以前在選PCB封裝時(shí),可以直接選集成庫(kù)里的封裝,最近不知怎么的集成庫(kù)里的封裝就不顯了,我希望可以把這個(gè)功能調(diào)出來(lái),使用時(shí)會(huì)方便很多。電腦重啟了,軟件重裝

2012-11-09 18:40:18

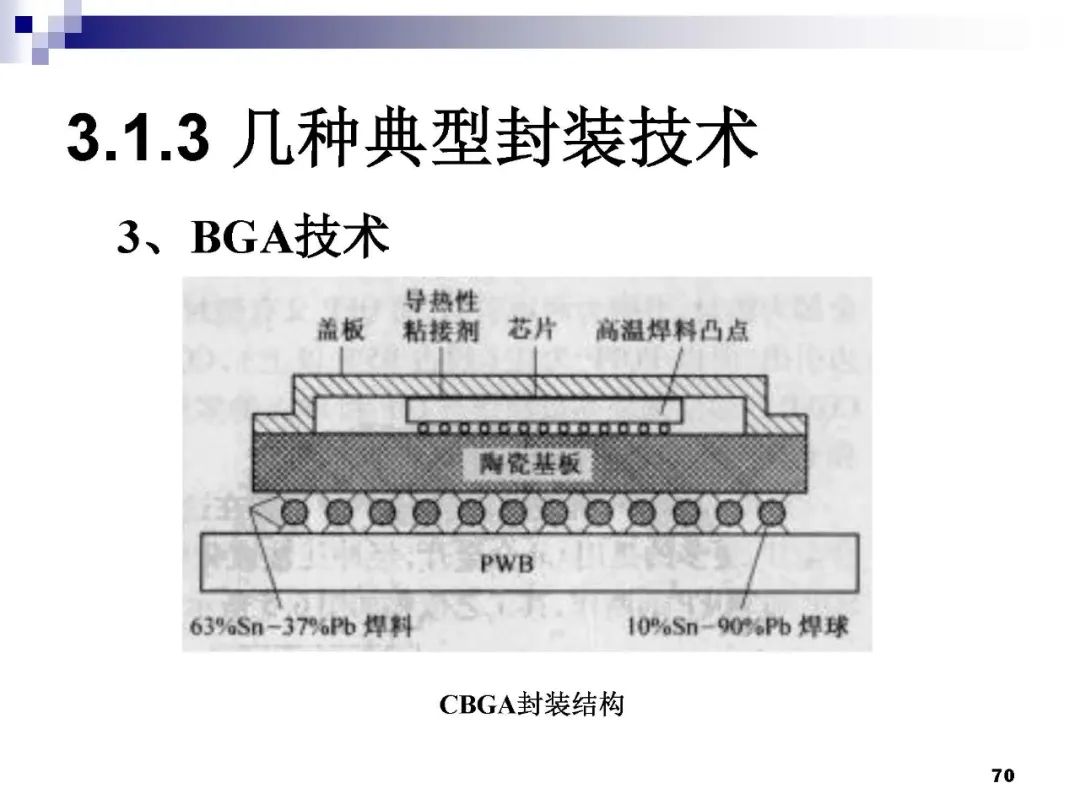

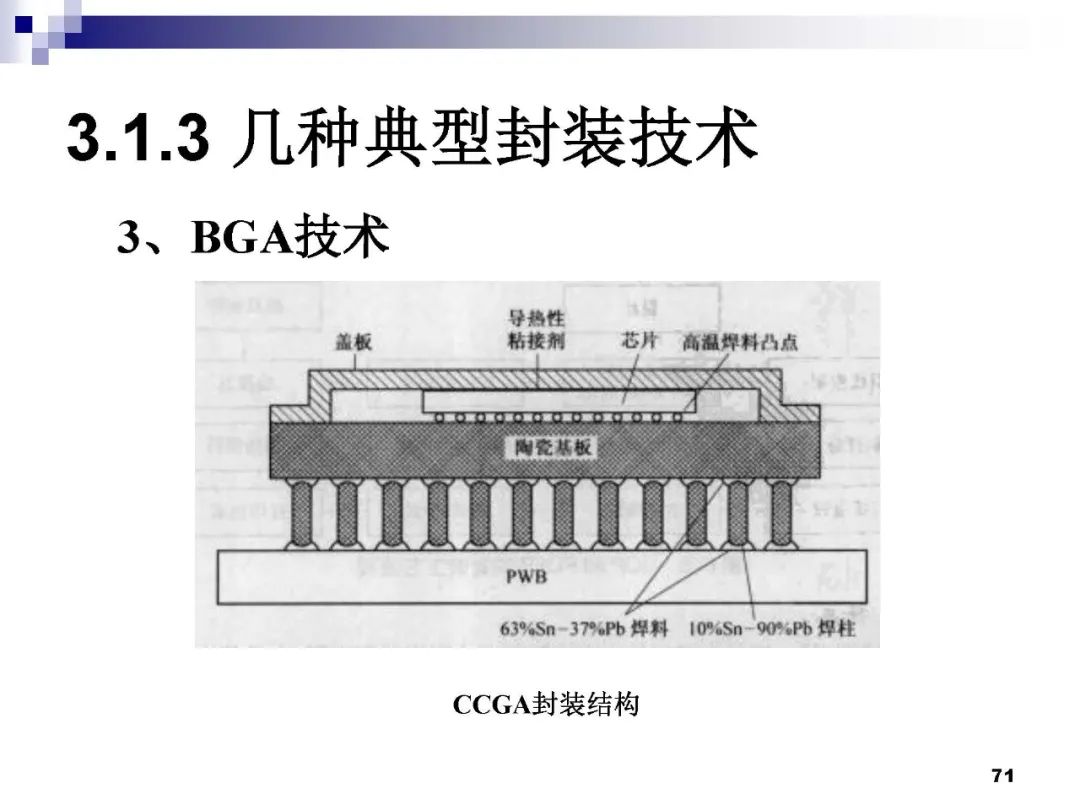

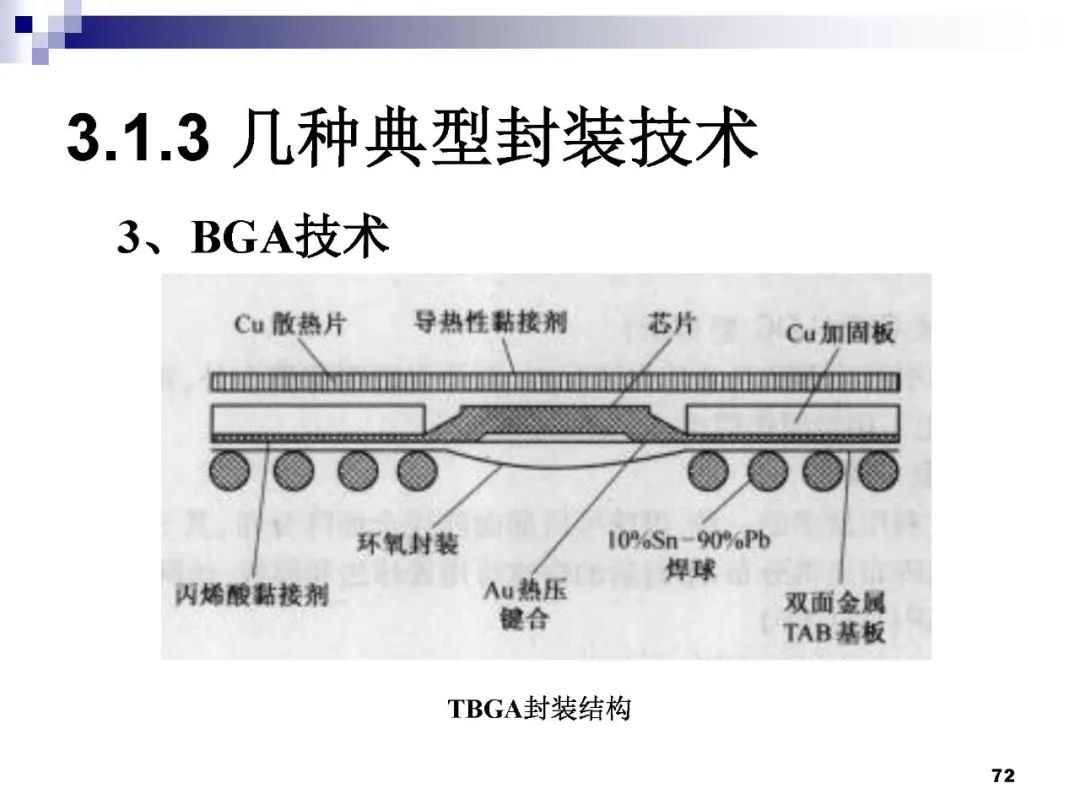

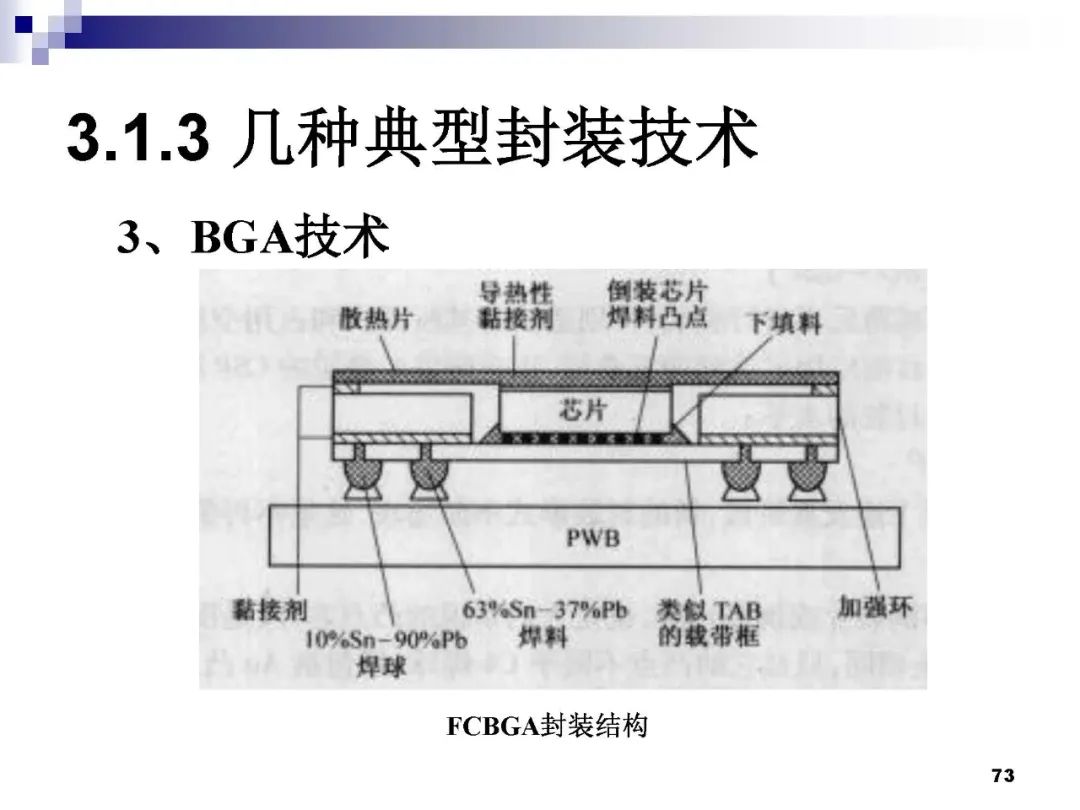

BGA封裝技術(shù)是一種先進(jìn)的集成電路封裝技術(shù),主要用于現(xiàn)代計(jì)算機(jī)和移動(dòng)設(shè)備的內(nèi)存和處理器等集成電路的封裝。與傳統(tǒng)的封裝方式相比,BGA封裝具有更小的體積,更好的散熱性能和電性能,可在相同體積下提高

2023-04-11 15:52:37

技術(shù)。CMOS集成電路設(shè)計(jì)手冊(cè)原書(shū)由淺入深介紹從模型到器件,從電路到系統(tǒng)的全面內(nèi)容,可作為CMOS基礎(chǔ)知識(shí)的重要參考書(shū)

2019-03-15 18:09:22

非易失性MRAM芯片組件通常在半導(dǎo)體晶圓廠(chǎng)的后端工藝生產(chǎn),下面英尚微電子介紹關(guān)于MRAM關(guān)鍵工藝步驟包括哪幾個(gè)方面.

2021-01-01 07:13:12

性和可裝配性等因素。所以DFM又是并行工程中最重要的支持工具。它的關(guān)鍵是設(shè)計(jì)信息的工藝性分析、制造合理性評(píng)價(jià)和改進(jìn)設(shè)計(jì)的建議。本文我們就將對(duì)PCB工藝中的DFM通用技術(shù)要求做簡(jiǎn)單介紹。

2021-01-26 07:17:12

方法對(duì)應(yīng)的檢測(cè)設(shè)備及安裝布局一般分為在線(xiàn)(串聯(lián)在流水線(xiàn)中)和離線(xiàn)(獨(dú)立于流水線(xiàn)外)兩種。在以下條件前提下應(yīng)優(yōu)先采用在線(xiàn)檢測(cè)工藝布局以提高檢測(cè)效率和流水線(xiàn)作業(yè)效率: 二、檢測(cè)技術(shù)∕工藝概述 適用于

2023-04-07 14:41:37

天線(xiàn)在分切過(guò)程中放卷復(fù)卷造成的損傷,這對(duì)比較敏感的銀漿印制天線(xiàn)尤其重要,同時(shí)生產(chǎn)速度也高很多。等產(chǎn)品從該生產(chǎn)線(xiàn)上下來(lái),RFID標(biāo)簽的整套工藝就結(jié)束了。二、標(biāo)簽封裝流程1、涉及集成電路封裝技術(shù),比較特殊

2008-05-26 14:21:40

高速模擬IO、甚至一些射頻電路集成在一起,只要它不會(huì)太復(fù)雜。 由于工藝技術(shù)的不兼容性,RF集成通常被認(rèn)為是一種基本上尚未解決的SoC挑戰(zhàn)。在數(shù)字裸片上集成RF電路會(huì)限制良品率或?qū)е赂甙旱?b class="flag-6" style="color: red">測(cè)試成本,從而

2019-07-05 08:04:37

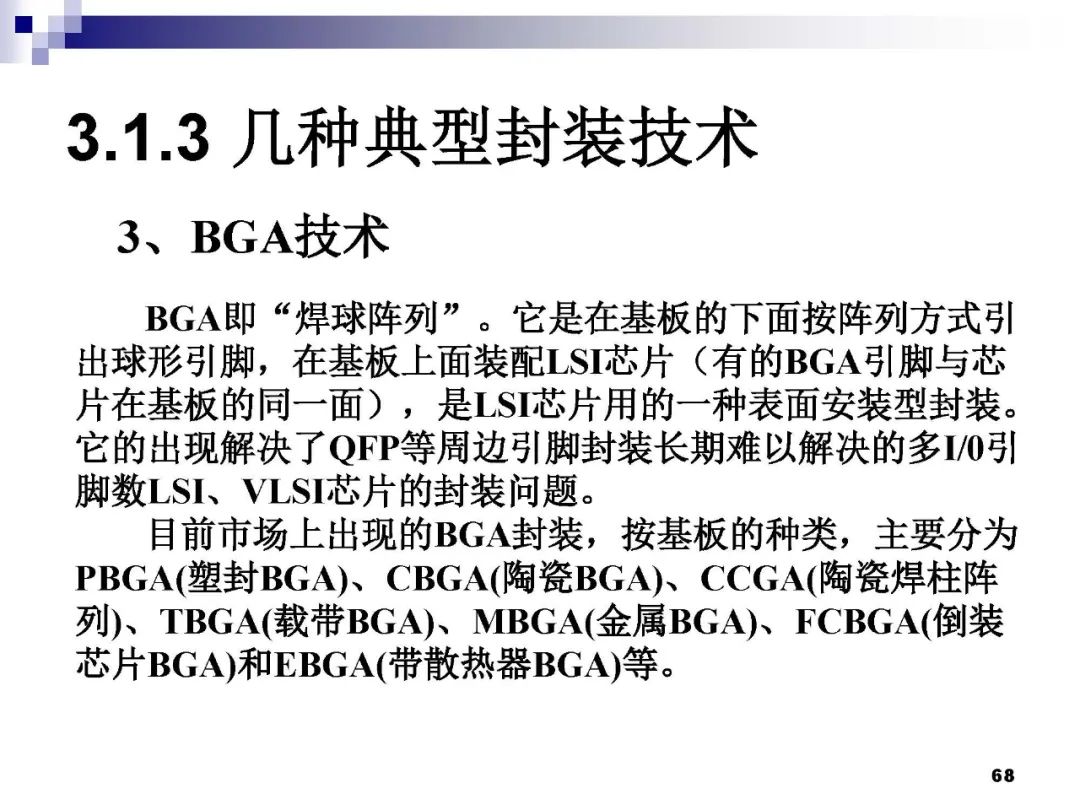

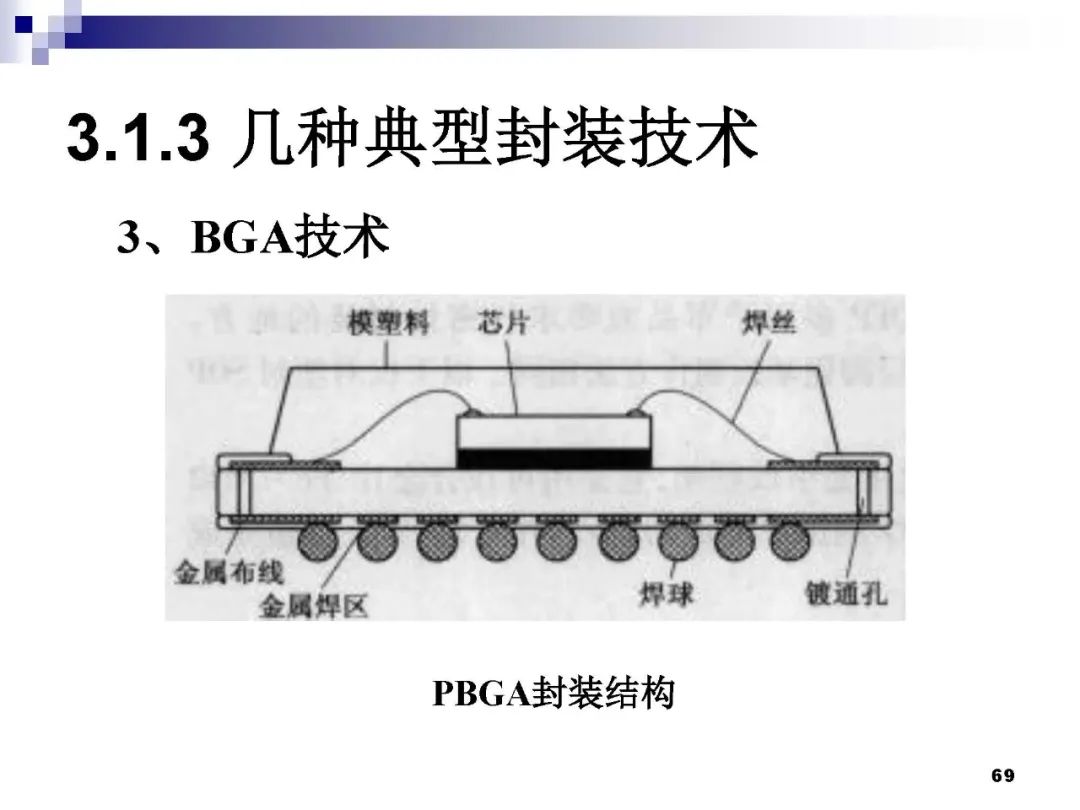

隨著市場(chǎng)對(duì)芯片集成度要求的提高,I/O引腳數(shù)急劇增加,功耗也隨之增大,對(duì)集成電路封裝更加嚴(yán)格。為了滿(mǎn)足發(fā)展的需要,BGA封裝開(kāi)始被應(yīng)用于生產(chǎn)。BGA也叫球狀引腳柵格陣列封裝技術(shù),它是一種高密度表面

2018-09-18 13:23:59

= 2.0 mA/μm2) 達(dá)到MTTF> 1 × 106 小時(shí)的壽命使之適用于測(cè)試級(jí)別的應(yīng)用。DHBTs 集成了3層互聯(lián)金屬,包括2級(jí)電阻和MIM電容。在3”生產(chǎn)線(xiàn)上這種IC 技術(shù)已被用于制造

2019-07-04 06:52:01

隨著射頻無(wú)線(xiàn)通信事業(yè)的發(fā)展和移動(dòng)通訊技術(shù)的進(jìn)步,射頻微波器件的性能與速度成為人們關(guān)注的重點(diǎn),市場(chǎng)對(duì)其的需求也日益增多。目前,CMOS工藝是數(shù)字集成電路設(shè)計(jì)的主要工藝選擇,對(duì)于模擬與射頻集成電路來(lái)說(shuō),有哪些選擇途徑?為什么要選擇標(biāo)準(zhǔn)CMOS工藝集成肖特基二極管?

2019-08-01 08:18:10

互聯(lián)網(wǎng)技術(shù)中最新路由交換測(cè)試技術(shù)的介紹,看完你就懂了

2021-05-26 06:00:56

集成無(wú)源元件技術(shù)可以集成多種電子功能,具有小型化和提高系統(tǒng)性能的優(yōu)勢(shì),以取代體積龐大的分立無(wú)源元件。文章主要介紹了什么是集成無(wú)源元件?集成無(wú)源元件對(duì)PCB技術(shù)發(fā)展產(chǎn)生了什么影響?

2019-08-02 07:04:23

1 引言 半導(dǎo)體技術(shù)的進(jìn)步大大提高了芯片晶體管數(shù)量和功能,這一集成規(guī)模在幾年前是無(wú)法想象的。因此,如果沒(méi)有IC封裝技術(shù)快速的發(fā)展,不可能實(shí)現(xiàn)便攜式電子產(chǎn)品的設(shè)計(jì)。在消費(fèi)類(lèi)產(chǎn)品小型化和更輕、更薄

2018-08-27 15:45:31

前端制造工藝對(duì)封裝技術(shù)的影響半導(dǎo)體前端制造工藝的發(fā)展總是直接迅速地反應(yīng)在后端生產(chǎn)技術(shù)上。圖7顯示了引線(xiàn)鍵合及倒裝芯片的焊盤(pán)間距隨半導(dǎo)體集成電路線(xiàn)寬的變化趨勢(shì)[4]。集成電路的線(xiàn)寬將由目前的O.09μm

2018-11-23 17:03:35

微電子三級(jí)封裝是什么?新型微電子封裝技術(shù)介紹

2021-04-23 06:01:30

半導(dǎo)體發(fā)展至今,無(wú)論是從結(jié)構(gòu)和加工技術(shù)多方面都發(fā)生了很多的改進(jìn),如同Gordon E. Moore老大哥預(yù)測(cè)的一樣,半導(dǎo)體器件的規(guī)格在不斷的縮小,芯片的集成度也在不斷提升,工藝制程從90nm

2020-12-10 06:55:40

)、氮化鎵(GaN)、碳化硅(SiC)、雙極硅、絕緣硅(SoI)和藍(lán)寶石硅(SoS)等工藝技術(shù)給業(yè)界提供了豐富的選擇。雖然半導(dǎo)體器件的集成度越來(lái)越高,但分立器件同樣在用這些工藝制造。隨著全球電信網(wǎng)絡(luò)向

2019-07-05 08:13:58

)、氮化鎵(GaN)、碳化硅(SiC)、雙極硅、絕緣硅(SoI)和藍(lán)寶石硅(SoS)等工藝技術(shù)給業(yè)界提供了豐富的選擇。雖然半導(dǎo)體器件的集成度越來(lái)越高,但分立器件同樣在用這些工藝制造。隨著全球電信網(wǎng)絡(luò)向長(zhǎng)期

2019-08-20 08:01:20

存在多個(gè)供應(yīng)商供應(yīng)芯片封裝在一起而引出的商業(yè)挑戰(zhàn),尤其是大容量存儲(chǔ)器和超大規(guī)模芯片存在的測(cè)試及老化問(wèn)題,但在電子產(chǎn)品多樣化的需求和封裝測(cè)試技術(shù)不斷進(jìn)步的推動(dòng)下,MCM封裝會(huì)在今天的基礎(chǔ)上克服挑戰(zhàn),贏得更大的發(fā)展。本文摘自《集成電路應(yīng)用》 :

2018-08-28 15:49:25

沒(méi)有讀者認(rèn)識(shí)到發(fā)生在3DIC集成中的技術(shù)進(jìn)步,他們認(rèn)為該技術(shù)只是疊層和引線(xiàn)鍵合,是一種后端封裝技術(shù)。而我們?cè)撊绾稳フ?DIC集成技術(shù)?

2021-04-07 06:23:51

本帖最后由 eehome 于 2013-1-5 09:50 編輯

常用IC封裝技術(shù)介紹

2012-12-05 08:21:29

”的縮寫(xiě),即球柵陣列封裝。20世紀(jì)90年代,隨著技術(shù)的進(jìn)步,芯片集成度不斷提高,I/O引腳數(shù)急劇增加,功耗也隨之增大,對(duì)集成電路封裝的要求也更加嚴(yán)格。為了滿(mǎn)足發(fā)展的需要,BGA封裝開(kāi)始被應(yīng)用于生產(chǎn)

2020-03-16 13:15:33

封裝。20世紀(jì)90年代,隨著技術(shù)的進(jìn)步,芯片集成度不斷提高,I/O引腳數(shù)急劇增加,功耗也隨之增大,對(duì)集成電路封裝的要求也更加嚴(yán)格。為了滿(mǎn)足發(fā)展的需要,BGA封裝開(kāi)始被應(yīng)用于生產(chǎn)。采用BGA技術(shù)封裝的內(nèi)存

2020-02-24 09:45:22

的現(xiàn)有低寄生電感封裝方式進(jìn)行分類(lèi)對(duì)比;羅列比較現(xiàn)有提高封裝高溫可靠性的材料和制作工藝,如芯片連接材料與技術(shù);最后,討論現(xiàn)有多功能集成封裝方法,介紹多種先進(jìn)散熱方法。在前面綜述的基礎(chǔ)上,結(jié)合電力電子

2023-02-22 16:06:08

方案。在工藝及封裝測(cè)試方面,目前長(zhǎng)運(yùn)通可以按照不同的工藝流程設(shè)計(jì)IC產(chǎn)品,設(shè)計(jì)面覆蓋各種工藝模型和工藝形式。長(zhǎng)運(yùn)通一直與ROHM、UMC、AMPI保持密切合作,以保證產(chǎn)品具有很好的一致性。此外,長(zhǎng)運(yùn)通的所有IC產(chǎn)品都進(jìn)行晶圓及封裝成品測(cè)試,以確保向客戶(hù)交付高標(biāo)準(zhǔn)產(chǎn)品。

2020-10-28 09:31:28

近年來(lái),有關(guān)將CMOS工藝在射頻(RF)技術(shù)中應(yīng)用的可能性的研究大量增多。深亞微米技術(shù)允許CMOS電路的工作頻率超過(guò)1GHz,這無(wú)疑推動(dòng)了集成CMOS射頻電路的發(fā)展。目前,幾個(gè)研究組已利用標(biāo)準(zhǔn)

2019-08-22 06:24:40

與工藝開(kāi)發(fā)等技術(shù)工作;7. 完成領(lǐng)導(dǎo)安排的其他日常工作。封裝工藝/設(shè)備工程師崗位要求:1. 3年以上半導(dǎo)體行業(yè)封裝設(shè)備工作經(jīng)驗(yàn);2. 熟悉大功率半導(dǎo)體器件封裝關(guān)鍵工藝流程;3. 大學(xué)本科及以上學(xué)歷,電氣

2022-02-22 11:15:35

是提高集成度、改進(jìn)器件性能的關(guān)鍵。特征尺寸的減小主要取決于光刻技術(shù)的改進(jìn)。集成電路的特征尺寸向深亞微米發(fā)展,目前的規(guī)模化生產(chǎn)是0.18μm、0.15 μm 、0.13μm工藝, Intel目前將大部分芯片

2018-08-24 16:30:28

1 前言 電路產(chǎn)業(yè)已成為國(guó)民經(jīng)濟(jì)發(fā)展的關(guān)鍵,而集成電路設(shè)計(jì)、制造和封裝測(cè)試是集成電路產(chǎn)業(yè)發(fā)展的三大產(chǎn)業(yè)之柱。這已是各級(jí)領(lǐng)導(dǎo)和業(yè)界的共識(shí)。微電子封裝不但直接影響著集成電路本身的電性能、機(jī)械性能

2018-09-12 15:15:28

2種新型的芯片封裝技術(shù)介紹在計(jì)算機(jī)內(nèi)存產(chǎn)品工藝中,內(nèi)存的封裝技術(shù)是內(nèi)存制造工藝中最關(guān)鍵一步,采用不同封裝技術(shù)的內(nèi)存條,在性能上存在較大差距。只有高品質(zhì)的封裝技術(shù)才能生產(chǎn)出完美的內(nèi)存產(chǎn)品。本文就主要

2009-04-07 17:14:08

是蜂窩通信系統(tǒng),該類(lèi)系統(tǒng)的RF功能集成的重點(diǎn)在于無(wú)源元件的集成。本文介紹了通過(guò)多片封裝或模塊實(shí)現(xiàn)無(wú)源元件與RF有源元件集成的策略。信息在通信系統(tǒng)的兩點(diǎn)傳輸過(guò)程中,射頻功能扮演了重要角色。在這類(lèi)系統(tǒng)中,RF

2019-06-25 07:35:19

` 晶圓級(jí)封裝是一項(xiàng)公認(rèn)成熟的工藝,元器件供應(yīng)商正尋求在更多應(yīng)用中使用WLP,而支持WLP的技術(shù)也正快速走向成熟。隨著元件供應(yīng)商正積極轉(zhuǎn)向WLP應(yīng)用,其使用范圍也在不斷擴(kuò)大。 目前有5種成熟

2011-12-01 14:33:02

本文系統(tǒng)地介紹了12種簡(jiǎn)化設(shè)計(jì)技術(shù),這些技術(shù)解決了系統(tǒng)集成中的所有常見(jiàn)問(wèn)題,有助確保在系統(tǒng)芯片中成功集成高性能數(shù)據(jù)轉(zhuǎn)換器。

2021-02-23 07:19:13

有功率半導(dǎo)體器件外,還包含驅(qū)動(dòng)電路、控制電路、傳感器、保護(hù)電路、輔助電源及無(wú)源元件。集成與封裝技術(shù)作為電力電子集成模塊的一個(gè)重點(diǎn)研究方向,主要研究模塊的集成和封裝工藝。目前已有越來(lái)越多的學(xué)者認(rèn)識(shí)到,能否

2018-08-28 11:58:28

的主要制造技術(shù)。內(nèi)容包括電子制造技術(shù)概述、集成電路基礎(chǔ)、集成電路制造技術(shù)、元器件封裝工藝流程、元器件封裝形式及材料、光電器件制造與封裝、太陽(yáng)能光伏技術(shù)、印制電路板技術(shù)以及電子組裝技術(shù)。書(shū)中簡(jiǎn)要介紹了

2017-03-23 19:39:21

電源管理ic芯片--集成電路介紹及原理應(yīng)用(恒佳興電子)集成電路介紹及原理應(yīng)用集成電路是一種采用特殊工藝,將晶體管、電阻、電容等元件集成在硅基片上而形成的具有一定功能的器件,英文為縮寫(xiě)為IC,也俗稱(chēng)

2015-07-14 15:14:35

鮮 飛(烽火通信科技股份有限公司,湖北 武漢 430074)摘 要:微電子技術(shù)的飛速發(fā)展也同時(shí)推動(dòng)了新型芯片封裝技術(shù)的研究和開(kāi)發(fā)。本文主要介紹了幾種芯片封裝技術(shù)的特點(diǎn),并對(duì)未來(lái)的發(fā)展趨勢(shì)及方向進(jìn)行了

2018-11-23 16:59:52

;?引腳數(shù)。引腳數(shù)越多,越高級(jí),但是工藝難度也相應(yīng)增加;其中,CSP由于采用了FlipChip技術(shù)和裸片封裝,達(dá)到了 芯片面積/封裝面積=1:1,為目前最高級(jí)的技術(shù);芯片封裝測(cè)試流程詳解ppt[hide]暫時(shí)不能上傳附件 等下補(bǔ)上[/hide]

2012-01-13 11:46:32

芯片封裝測(cè)試工藝教程教材資料,完整的介紹了芯片封裝測(cè)試工藝流程,及每一個(gè)技術(shù)點(diǎn),有圖有流程,能夠幫助大家快速理解芯片封裝測(cè)試工藝。粘片就是將芯片固定在某一載體上的過(guò)程。共晶合金法:芯片背面和載體之間

2012-01-13 14:46:21

芯片封裝詳細(xì)介紹裝配工藝一、DIP雙列直插式封裝DIP(DualIn-LINE PACKAGE)是指采用雙列直插形式封裝的集成電路芯片,絕大多數(shù)中小規(guī)模集成電路(IC)均采用這種封裝形式,其引腳數(shù)

2021-11-03 07:41:28

請(qǐng)?jiān)敿?xì)敘述腐蝕工藝工段的工藝流程以及整個(gè)前道的工藝技術(shù)

2011-04-13 18:34:13

集成電路圓片級(jí)芯片封裝技術(shù)(WLCSP)及其產(chǎn)品屬于集成創(chuàng)新,是江陰長(zhǎng)電先進(jìn)封裝有限公司結(jié)合了銅柱凸塊工藝技術(shù)及公司自身在封裝領(lǐng)域的技術(shù)沉淀,開(kāi)發(fā)出的區(qū)別于國(guó)外技

2009-12-14 09:51:59 27

27 MCM(MCP)封裝測(cè)試技術(shù)及產(chǎn)品:南通富士通的MCM 封裝測(cè)試技術(shù)是利用陶瓷基板或硅基板作為芯片間的互連,將二片以上的超大規(guī)模集成電路芯片安裝在多層互連基板上,再用金絲與金屬

2009-12-17 14:47:00 15

15 摘要在當(dāng)今電子產(chǎn)品的組裝中各種新的封裝技術(shù)不斷涌現(xiàn)BGA/CSP是當(dāng)今新的封裝主流主要論述了BGA封裝技術(shù)的主要類(lèi)型特性并根據(jù)實(shí)際經(jīng)驗(yàn)介紹了實(shí)際生產(chǎn)中如何實(shí)施BGA的返修工藝

2010-11-13 23:20:04 52

52 “封裝工藝員”課程詳細(xì)介紹

2010-11-16 00:36:40 53

53 2種新型的芯片封裝技術(shù)介紹

在計(jì)算機(jī)內(nèi)存產(chǎn)品工藝中,內(nèi)存的封裝技術(shù)是內(nèi)存制造工藝中最關(guān)鍵一步,采用不同封裝技術(shù)的內(nèi)存條,在性

2009-04-07 17:13:28 840

840 超細(xì)線(xiàn)蝕刻工藝技術(shù)介紹

目前,集成度呈越來(lái)越高的趨勢(shì),許多公司紛紛開(kāi)始SOC技術(shù),但SOC并不能解決所有系統(tǒng)集成的問(wèn)題,因

2010-03-30 16:43:08 1181

1181 介紹了電子集成塊的封裝工藝,針對(duì)電子集成線(xiàn)路封裝要求,提出了傳遞模結(jié)構(gòu)設(shè)計(jì)的要.點(diǎn),尤其對(duì)大型封裝傳遞模的流道設(shè)計(jì)、注入壓頭結(jié)構(gòu)、型腔設(shè)計(jì)和預(yù)防小島移動(dòng)等提出新的要

2011-10-26 16:47:28 48

48 在回顧現(xiàn)行的引線(xiàn)鍵合技術(shù)之后,本文主要探討了集成電路封裝中引線(xiàn)鍵合技術(shù)的發(fā)展趨勢(shì)。球形焊接工藝比楔形焊接工藝具有更多的優(yōu)勢(shì),因而獲得了廣泛使用。傳統(tǒng)的前向拱絲越來(lái)越

2011-10-26 17:13:56 86

86 文章介紹了幾種新的封裝工藝,如新型圓片級(jí)封裝工藝OSmium 圓片級(jí)封裝工藝,它能夠把裸片面積減少一半;新型SiP封裝工藝Smafti封裝工藝,它改進(jìn)了傳統(tǒng)SiP封裝工藝,把傳輸速度提高了

2011-12-29 15:34:45 82

82 電子專(zhuān)業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料—集成電路測(cè)試技術(shù)簡(jiǎn)單介紹

2016-09-01 17:24:53 0

0 PCB測(cè)試工藝技術(shù),很詳細(xì)的

2016-12-16 21:54:48 0

0 一、什么是COB封裝? COB封裝,是英語(yǔ)Chip On Board的縮寫(xiě),直譯就是芯片放在板上。 是一種區(qū)別于DIP和SMD封裝技術(shù)的新型封裝方式。如圖所示 在LED顯示技術(shù)領(lǐng)域,COB封裝工藝

2017-09-30 11:10:25 95

95 本文以集成電路測(cè)試儀為中心、主要介紹了什么是集成電路測(cè)試儀、集成電路測(cè)試儀有哪些種類(lèi)、電路測(cè)試儀的組成以及集成電路測(cè)試儀的選購(gòu)技巧。

2017-12-20 11:33:51 13079

13079 本期將為大家介紹單晶硅制造、晶圓加工和封裝測(cè)試環(huán)節(jié)的工藝流程、相關(guān)設(shè)備及其供應(yīng)商。

2018-07-15 09:41:27 29444

29444 本文檔的主要內(nèi)容詳細(xì)介紹的是IC封裝工藝測(cè)試流程的詳細(xì)資料詳解資料免費(fèi)下載。

2018-12-06 16:06:56 132

132 昨(22)日,聯(lián)合微電子中心攜手50余家產(chǎn)業(yè)鏈上下游企業(yè)、科研院所等,聯(lián)合倡議成立了中國(guó)集成電路特色工藝及封裝測(cè)試聯(lián)盟。該聯(lián)盟將整合國(guó)內(nèi)晶圓廠(chǎng)、封測(cè)廠(chǎng)、中試線(xiàn)等領(lǐng)域相關(guān)資源,覆蓋材料、器件、工藝、裝備全產(chǎn)業(yè)鏈,推動(dòng)行業(yè)特色工藝共性技術(shù)的整體水平邁上新臺(tái)階。

2019-01-23 16:08:09 3343

3343 本文介紹集成電路芯片制造后端大馬士革銅布線(xiàn)多層互聯(lián)及測(cè)試等工藝。目的是科普集成電路芯片制造工藝(制程)知識(shí),也可供第六代IGBT和汽車(chē)電子器件制造(工藝)技術(shù)人員參考。

2019-04-10 08:00:00 44

44 芯片封裝測(cè)試的流程你了解嗎IC封裝工藝詳細(xì)PPT簡(jiǎn)介

2019-05-12 09:56:59 28447

28447 ,然后封裝在一個(gè)管殼內(nèi),使整個(gè)電路的體積大大縮小,引出線(xiàn)和焊接點(diǎn)的數(shù)目也大為減少。集成的設(shè)想出現(xiàn)在50年代末和60年代初,是采用硅平面技術(shù)和薄膜與厚膜技術(shù)來(lái)實(shí)現(xiàn)的。電子集成技術(shù)按工藝方法分為以硅平面工藝為基礎(chǔ)的單片集成電路、以薄膜技術(shù)為基礎(chǔ)的薄膜集成

2020-03-27 16:45:07 3065

3065 原文標(biāo)題:工藝 | IC封裝測(cè)試工藝流程 文章出處:【微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。 責(zé)任編輯:haq

2020-10-10 17:42:13 7643

7643

關(guān)于封裝測(cè)試工藝教育資料分享。

2021-04-08 16:14:11 63

63 集成電路封裝測(cè)試與可靠性分析。

2021-04-09 14:21:51 110

110 集成電路芯片封裝工藝流程有哪些?

2021-07-28 15:28:16 12132

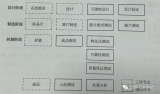

12132 電路基本的工藝流程步驟 集成電路的生產(chǎn)流程可分為: 設(shè)計(jì) 制造 封裝與測(cè)試 而其中,封裝與測(cè)試貫穿了整個(gè)過(guò)程,封裝與測(cè)試包括: 芯片設(shè)計(jì)中的設(shè)計(jì)驗(yàn)證 晶圓制造中的晶圓檢測(cè) 封裝后的成品測(cè)試 芯片設(shè)計(jì)中的設(shè)計(jì)驗(yàn)證 測(cè)試晶圓樣

2022-02-01 16:40:00 30223

30223 IGBT 功率模塊基本的封裝工藝介紹,給初入半導(dǎo)體芯片制造封裝的工程師作為參考資料。

2022-06-17 14:28:42 51

51 通過(guò)對(duì) EPSON 生產(chǎn)的 NS-6000 系列高速 IChandler 的介紹,討論了集成電路封裝的測(cè)試原理和測(cè)試方法,并基于 NS-6000 系列 handler,給出了具體測(cè)試實(shí)例分析。

2022-07-06 15:53:34 4

4 。其他名稱(chēng)包括半導(dǎo)體器件組裝、組裝、封裝或密封。封裝階段之后是集成電路的測(cè)試。下面小編就來(lái)講訴一下半導(dǎo)體集成電路封裝技術(shù)的作用,以及體集成電路芯片封裝的意義。 集成電路封裝技術(shù) “封裝”一詞伴隨集成電路制造技術(shù)

2022-12-13 09:18:24 3863

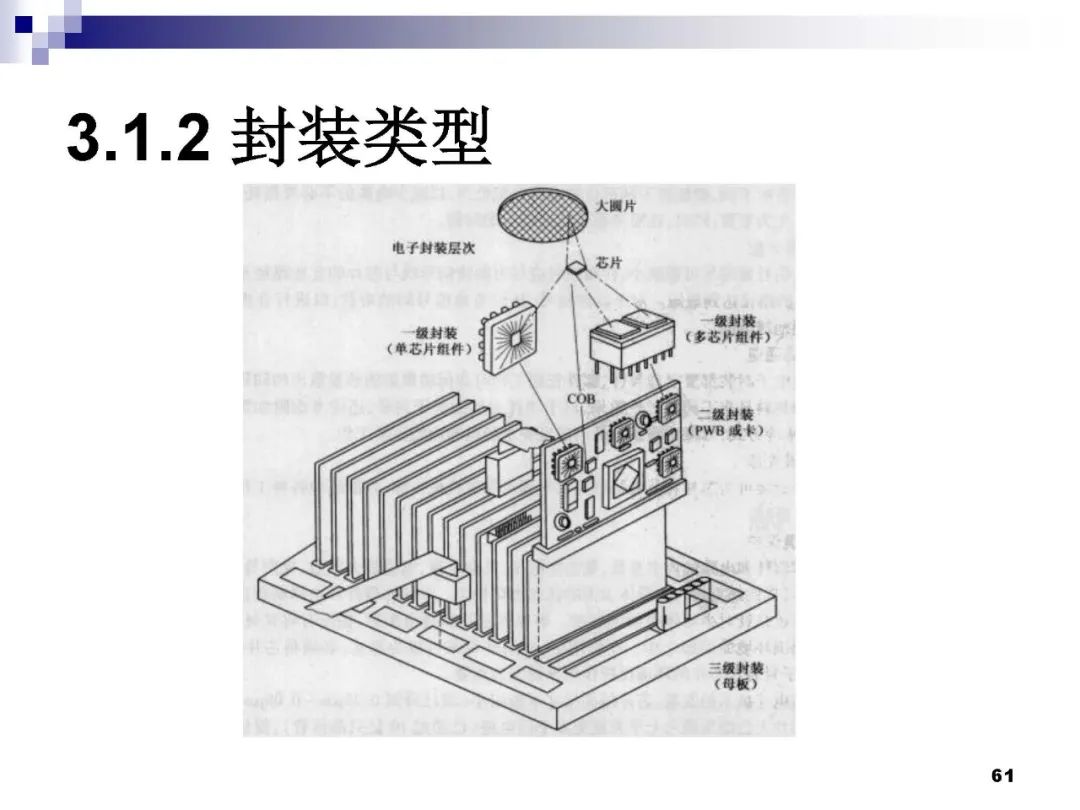

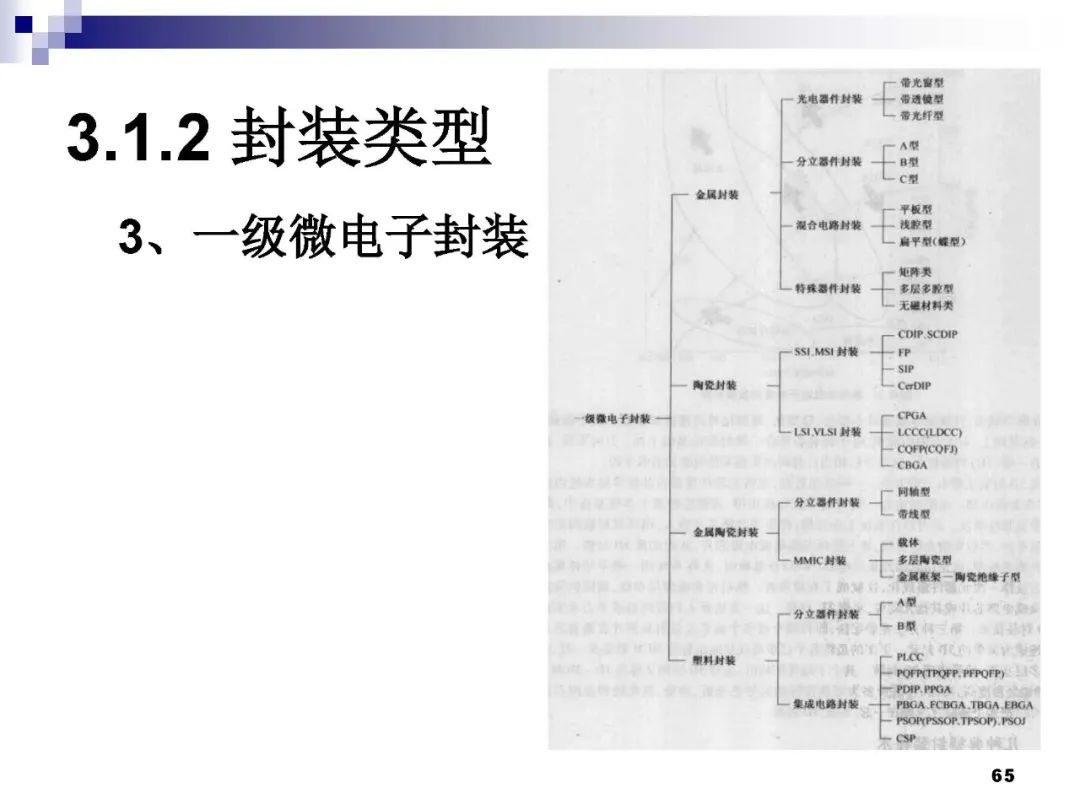

3863 功能的作用。下面__【科準(zhǔn)測(cè)控】__小編就來(lái)為大家介紹一下半導(dǎo)體集成電路封裝工藝的技術(shù)層次以及封裝的分類(lèi)有哪些?一起往下看吧! 1、封裝工藝的技術(shù)層次 電子封裝始于集成電路芯片制成之后,包括集成電路芯片的粘貼固定、電路連線(xiàn)

2022-12-16 14:24:29 1957

1957

, WLP)、硅通孔(Through Silicon Via, TSV)、三維集成等先進(jìn)封裝工藝,帶來(lái)了新的測(cè)試工序和復(fù)雜光機(jī)電集成失效特性:這些技術(shù)的演進(jìn)也導(dǎo)致集成電路測(cè)試變得日益復(fù)雜。互聯(lián)網(wǎng)、物聯(lián)網(wǎng)、云計(jì)算、大數(shù)據(jù)等新應(yīng)用、新業(yè)態(tài)的出現(xiàn),不斷推動(dòng)集成電路測(cè)試技術(shù)的發(fā)展和信息化進(jìn)程。

2023-05-25 09:48:39 1102

1102

集成電路封裝測(cè)試是指對(duì)集成電路封裝進(jìn)行的各項(xiàng)測(cè)試,以確保封裝的質(zhì)量和性能符合要求。封裝測(cè)試通常包括以下內(nèi)容。

2023-05-25 17:32:52 1382

1382 詳解半導(dǎo)體封裝測(cè)試工藝

2023-05-31 09:42:18 997

997

含量。在現(xiàn)代科技發(fā)展的時(shí)代,芯片封裝測(cè)試工藝技術(shù)不斷更新和深入探索,需要進(jìn)行大量的研究和開(kāi)發(fā)。本文將從以下幾個(gè)方面講述芯片封裝測(cè)試的技術(shù)含量。 1.封裝測(cè)試是干嘛的? 芯片封裝測(cè)試是將芯片進(jìn)行封裝后,對(duì)它進(jìn)行各種類(lèi)型的

2023-08-24 10:41:57 2322

2322 半導(dǎo)體封裝技術(shù)的發(fā)展一直都是電子行業(yè)持續(xù)創(chuàng)新的重要驅(qū)動(dòng)力。隨著集成電路技術(shù)的發(fā)展,半導(dǎo)體封裝技術(shù)也經(jīng)歷了從基礎(chǔ)的封裝到高密度、高性能的封裝的演變。本文將介紹半導(dǎo)體封裝工藝的四個(gè)等級(jí),以助讀者更好地理解這一關(guān)鍵技術(shù)。

2023-10-09 09:31:55 933

933

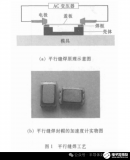

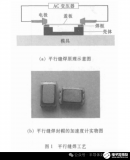

密性等。本文介紹了五種用于MEMS封裝的封帽工藝技術(shù),即平行縫焊、釬焊、激光焊接、超聲焊接和膠粘封帽。總結(jié)了不同封帽工藝的特點(diǎn)以及不同MEMS器件對(duì)封帽工藝的選擇。本文還介紹了幾種常用的吸附劑類(lèi)型,針對(duì)吸附劑易于飽和問(wèn)題,給出了封帽工藝解決方案,探

2024-02-25 08:39:28 171

171

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

833

833

829

829

1827

1827

335

335

157

157

27

27 15

15 52

52

840

840

1181

1181 48

48 86

86 82

82 0

0 95

95 13079

13079 29444

29444 132

132 3343

3343 44

44 28447

28447 3065

3065 7643

7643

30223

30223 4

4 3863

3863 1957

1957

1102

1102

1382

1382 2322

2322 933

933

171

171

評(píng)論