設(shè)備、材料和封裝技術(shù)的進步都會導(dǎo)致問題。

汽車供應(yīng)鏈上的企業(yè)遍布全球,越來越多的企業(yè)將自身的非核心業(yè)務(wù)外包給第三方企業(yè),因而汽車供應(yīng)鏈的結(jié)構(gòu)也更加復(fù)雜化。但是,汽車供應(yīng)鏈日益全球化,復(fù)雜化,多級化,精益化的特點,以及車企和供應(yīng)鏈對精益生產(chǎn)的追求和運營的精細化,導(dǎo)致供應(yīng)鏈本身的彈性不足,這增加了汽車供應(yīng)鏈網(wǎng)絡(luò)運營環(huán)境的不確定性。

對于每個新節(jié)點,都必須考慮額外的物理影響,但并非所有這些影響都具有相同的關(guān)鍵級別。這些影響里被更頻繁提及的一種是自熱。

所有設(shè)備都會消耗電力,當它們這樣做時,它就會變成熱量。“本質(zhì)上,所有有源器件都會在載流子移動時產(chǎn)生熱量,從而為電流通過柵極創(chuàng)造通道,”西門子 EDA Calibre 設(shè)計解決方案集團 DRC 應(yīng)用營銷總監(jiān) John Ferguson 說。“在歷史悠久的 CMOS 時代,這些影響在很大程度上是可控的,因為在柵極捕獲的熱量有一條相對簡單的路徑可以通過硅襯底消散。不幸的是,CMOS 方法最終遇到了物理限制,在這種情況下它無法繼續(xù)在可靠運行的同時持續(xù)縮小尺寸。”

縮放比例也有影響。“直到 20 世紀 90 年代,這個問題還不是問題,”Synopsys TCAD 產(chǎn)品組的研究員 Victor Moroz 說。“那是因為人們能夠降低電源電壓,這確實有助于降低功耗。但一旦人們發(fā)現(xiàn)技術(shù)的局限性,就無法將電源電壓降低到遠低于 0.7V 左右。”

自熱與活動有關(guān)。Cadence 產(chǎn)品管理總監(jiān) Jay Madiraju 表示:“芯片最活躍部分的自熱效應(yīng)最高,這給設(shè)計人員帶來了額外的瓶頸。”“當電路運行時,設(shè)備和互連的溫度會根據(jù)活動量增加。當設(shè)備在運行過程中消耗功率時,它會產(chǎn)生熱量。類似地,對于金屬互連,溫度升高將由在互連中流動的電流通過電阻損耗產(chǎn)生熱量(即焦耳熱)引起。這兩個因素都會導(dǎo)致產(chǎn)生熱量。”

收縮使事情變得更糟。“隨著設(shè)備和電線的幾何尺寸減小,電流密度增加,”Lightelligence 的物理設(shè)計負責(zé)人 Rob Kuhn 說。“這加劇了自熱及其對性能和可靠性的相關(guān)影響。同樣在高級節(jié)點中,finFET 和納米線器件會進一步增加自熱,因為導(dǎo)熱性會降低并且熱量會長時間滯留在器件附近。”

材料有影響。“制造器件所用材料的變化導(dǎo)致熱效應(yīng)進一步增加,”Cadence 的 Madiraju 說。“例如,低 K 電介質(zhì)比以前的金屬間電介質(zhì)具有更高的熱阻。自熱開始成為 65nm 以下傳統(tǒng)節(jié)點設(shè)計的一個問題,并且隨著特征尺寸的縮小而變得更具挑戰(zhàn)性,特別是對于先進節(jié)點工藝,即 finFET 設(shè)計。”

形狀也會產(chǎn)生問題。Ansys 研發(fā)總監(jiān) Tianhao Zhang 表示:“FinFET 新型三維結(jié)構(gòu)的自熱效應(yīng)比平面器件更為顯著。”“此外,finFET 結(jié)構(gòu)中使用的材料的導(dǎo)熱性差,以及難以從被介電材料包圍的隔離鰭片散熱到基板,導(dǎo)致 finFET 器件的溫度更高。反過來,這會對互連線造成更高的熱耦合效應(yīng)。”

雖然縮放有助于解決一些問題,但其他問題會變得更糟。Synopsys 的 Moroz 說:“自 finFET 推出以來,功率密度變得足夠大,人們注意到并開始擔(dān)心它。”“晶體管密度每年增加大約 10% 到 15%。一個晶體管的功耗降低很慢,因為人們在一點一點地改進技術(shù)。當你減少幾何形狀時,電容也會減少。功耗主要與電容有關(guān),因為所有電路都在切換。無論何時切換,都必須為電容充電,而該電容來自你要切換的下一個晶體管。每次給它充電或放電時,能量都會沿著其他組件(電線)傳遞。因此,當你減小晶體管尺寸時,晶體管電容會減小,從而幫助降低功耗。而且因為它們更小,它們之間的電線變得更短,這也有幫助。但它跟不上密度的提高,總的來說你會看到你的功率密度在不斷增加。”

當設(shè)備產(chǎn)生熱量時,熱量會通過封裝、電路板和散熱器散發(fā)出去。西門子的 Ferguson 說:“新材料和與硅散熱器直接相互作用最少的非常薄的層增加了熱阻。”“這使得散熱變得更加困難。因此,設(shè)備被迫在更高且可能增加的溫度負載下工作。這些高溫會影響器件的閾值電壓和性能,最終導(dǎo)致可靠性挑戰(zhàn)。3D-IC 設(shè)計的趨勢可能會進一步加劇這個問題,進一步增加總散熱路徑。”

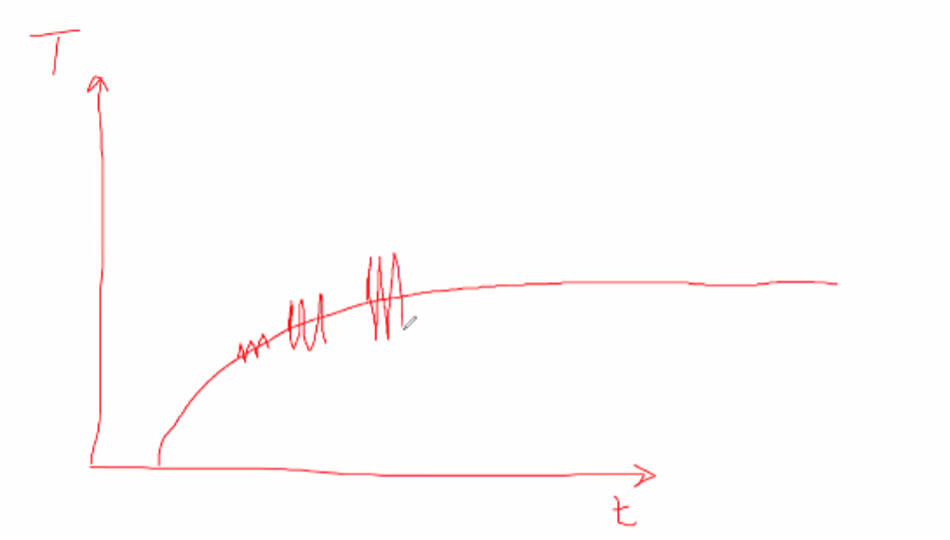

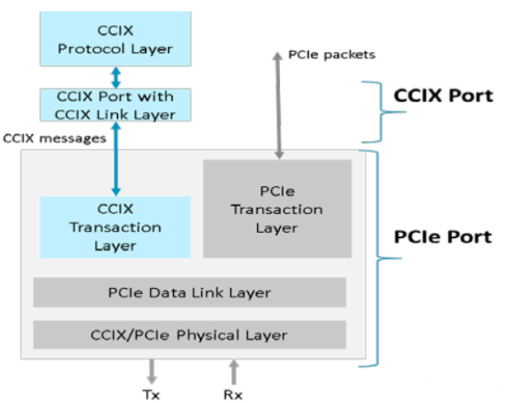

熱量的產(chǎn)生和散熱必須平衡。“考慮圖 1(下圖),”Moroz說。“在某個時候,你開始操作設(shè)備,溫度會上升,直到它飽和并在這個平衡點變得穩(wěn)定。這是因為你必須管理芯片的功率預(yù)算,以免整個芯片過熱。如果查看單個開關(guān),并從一個平面晶體管(在左側(cè))開始,它會打開然后關(guān)閉。在局部,晶體管溫度會先高后低,再高又低。當人們改用 finFET(中)時,總體上沒有任何變化,因為它仍然取決于你的功率預(yù)算和電路活動以及封裝的散熱能力。但是finFET有一個窄鰭,與平面相比,它的導(dǎo)熱和散熱能力不如平面,因此局部溫度會升高。現(xiàn)在人們正在改用環(huán)柵(右),熱量更難從它們中逸出,因為它們很小并且被不導(dǎo)電的東西包圍著。所以在本地,有一個更大的問題。但對于芯片規(guī)模,沒有任何改變。”

圖 1:芯片溫度和自熱。

熱量是芯片的殺手。即使溫度沒有高到足以毀壞設(shè)備,該設(shè)備也會受到長期影響。“對于設(shè)備而言,自熱會影響遷移率和閾值電壓,這反過來會限制設(shè)備性能并增加功耗,”Lightelligence的 Kuhn 說。“熱載流子注入、隨時間變化的電介質(zhì)擊穿 (TDDB) 和負偏置溫度不穩(wěn)定性 (NBTI) 會降低設(shè)備的長期可靠性。電線的固有電阻隨著溫度的升高而增加,這會通過減慢數(shù)據(jù)傳輸來影響芯片性能。隨著時間的推移,自熱還會加速電遷移效應(yīng),從而導(dǎo)致芯片故障。隨著技術(shù)的進步,這兩種趨勢都會惡化。”

行動計劃

與所有問題一樣,越早了解問題,處理起來就越容易,成本也就越低。過早老化設(shè)備的問題不僅需要對設(shè)計采取糾正措施,還需要成本更高的現(xiàn)場更換有缺陷的部件。

Ferguson概述了三個總體原則:

對設(shè)備行為的熱影響進行建模,以準確模擬預(yù)制造

使用任何和所有方法來減少總熱影響

尋找替代的消散路徑

“由于對芯片可靠性和性能的高度不利影響,對任何芯片或系統(tǒng)級封裝 (SiP) 的熱流進行建模至關(guān)重要,”Kuhn 說。“Ansys 和 Cadence 等公司提供的工具在這一領(lǐng)域變得越來越重要,因為它們使設(shè)計人員能夠識別可靠性和性能問題,并通過增加導(dǎo)線尺寸(降低電阻)和提高基板導(dǎo)熱性等技術(shù)來緩解這些問題”

所有分析都從模型開始。Cadence 高級產(chǎn)品經(jīng)理 Art Schaldenbrand 表示:“設(shè)備建模[CMC] 已經(jīng)認識到考慮自熱的必要性,最近的設(shè)備模型 BSIM-C 和 BSIM-I 包括自熱效應(yīng)。”“這些模型連同模擬器的增強功能,可以計算設(shè)備和互連中消耗的功率。代工廠通常會為高級節(jié)點工藝提供具有自加熱功能的模型。設(shè)計人員在使用 SPICE 仿真時可以考慮自熱對其設(shè)計的影響,從而深入了解電路性能由于其操作而發(fā)生的變化。雖然設(shè)計人員可以在仿真中包含自熱效應(yīng),但存在仿真性能成本,因此他們需要在如何分析熱效應(yīng)方面具有戰(zhàn)略意義。

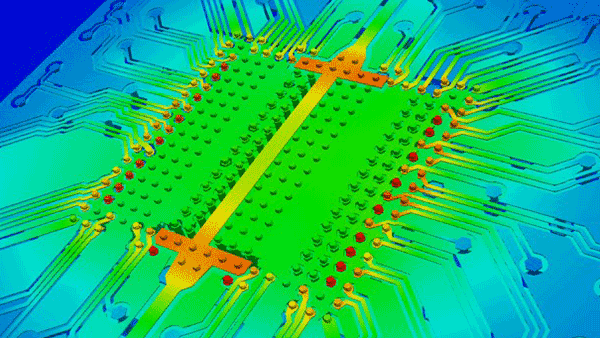

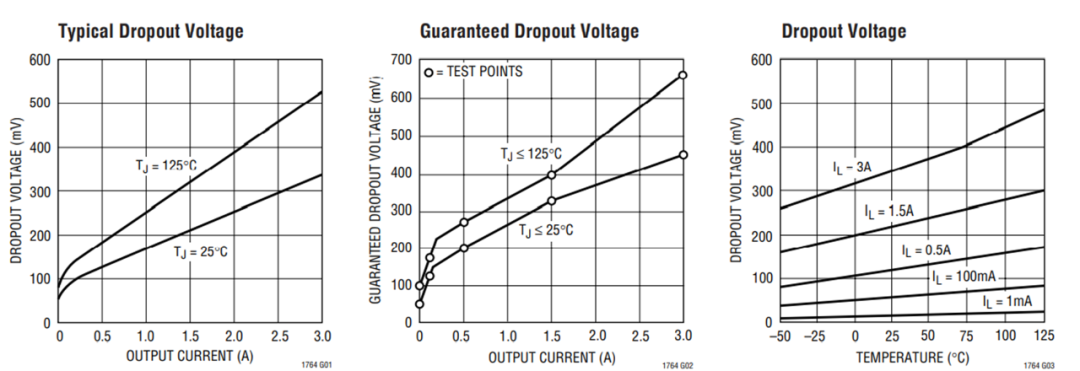

圖 2:IC 封裝互連結(jié)構(gòu)的溫度曲線。來源:Cadence

其他簡化可能導(dǎo)致悲觀的結(jié)果。“芯片上均勻的最壞情況環(huán)境溫度通常過于悲觀,”Ansys 的 Zhang 說。“要獲得準確、高分辨率的結(jié)果,甚至基于金屬層的環(huán)境溫度,以及自熱是分析電路可靠性所必需的。”

模擬晶體管自熱是否足夠?“你產(chǎn)生的熱量與阻力成正比,”Moroz說。“對于電線,每微米會有幾十歐姆。如果查看信號網(wǎng),它就是將開關(guān)連接到下一個開關(guān)的電線。這通常是幾微米長,而該網(wǎng)的電阻將是幾百歐姆。一個晶體管,它有兩種狀態(tài)。兩個階段之間有一個瞬態(tài),但兩個狀態(tài)是開和關(guān)。在關(guān)閉狀態(tài)下,它具有兆歐姆電阻。在開啟狀態(tài)下,通常它具有幾千歐姆的電阻。它支配著導(dǎo)線電阻。所以,如果一根電線是 100 歐姆,而你的開關(guān)是 10 千歐姆,那么電線會產(chǎn)生熱量,但要少 100 倍。”

雖然信號線的自熱本身可能不是問題,但熱耦合會增加這些溫度。Ansys 的 Zhang 表示:“電線的更高溫度對可靠性構(gòu)成了挑戰(zhàn),因為為這些電線定義了更小的允許電流以滿足預(yù)期的平均無故障時間 (MTTF)。”“這是電遷移造成的故障,隨著時間的推移會產(chǎn)生不希望的開路或短路。”

電力網(wǎng)絡(luò)中的電線有不同的問題。“電源網(wǎng)絡(luò)比信號網(wǎng)絡(luò)復(fù)雜得多,”Ansys 產(chǎn)品營銷總監(jiān) Marc Swinnen 說。“信號線是點對點或多點的,但電力網(wǎng)是網(wǎng)格。你無法使用相同的求解器來求解它。你必須使用類似SPICE 的電路模擬器。網(wǎng)絡(luò)很大。在一個有 500 億個晶體管的芯片上,你有 500 億個電源和接地點需要連接。這比整個美國的電網(wǎng)還要復(fù)雜。每一小段電線都必須建模為一個電阻器,所以有數(shù)千億個電阻器,必須減少數(shù)量才能模擬它。只有這樣才能準確判斷電流流向何處以及每個點的電壓。EM 分析是免費的——這是一個可靠性問題,但你需要知道流過所有電線的電流。這也與溫度有關(guān),因此需要了解全球溫度,而這取決于散熱器和環(huán)境。但是整個芯片的溫度各不相同。過去它被認為是整個芯片的單一溫度,但現(xiàn)在我們需要進行熱建模并包括焦耳自熱。”

減少供暖影響的最直接方法是減少活動。這通常被稱為暗硅。“高端服務(wù)器封裝每平方厘米可耗散約 50 瓦,”Moroz說。“關(guān)鍵是你在芯片上使用一小部分開關(guān),不要超過它。否則,它會過熱。如果你看看今天的技術(shù),你可以用大約 1% 的活動因子來實現(xiàn)這種功耗。這聽起來可能很糟糕,但它正在變得更糟,并且在一點一點地下降,每年下降 5% 或 10%。”

這一切都始于早期的系統(tǒng)分析。“了解你的功率預(yù)算始于復(fù)雜的芯片-封裝-電路板協(xié)同設(shè)計,”Zhang 說。“后期的熱問題會導(dǎo)致大的 ECO 循環(huán)、難以解決的問題,甚至是設(shè)計失敗。為了克服這個問題,應(yīng)在早期設(shè)計階段考慮熱效應(yīng),包括熱感知功能塊放置和熱熱點評估。這種考慮不僅有助于產(chǎn)生最佳設(shè)計,還有助于降低自熱影響并提高整體設(shè)計可靠性。”

散熱變得越來越困難,尤其是對于多芯片系統(tǒng)。“你有一些凸點將芯片連接到電路板,”Moroz說。“然后有一些散熱器可以幫助你散熱。中間有硅,它是一個很好的導(dǎo)熱體,所以各處的熱量會很均勻,你就等著封裝散熱。現(xiàn)在,如果拿起那塊芯片,開始在上面堆東西,這種材料的熱導(dǎo)率是多少?如果它是電介質(zhì),那就是個問題,因為它是熱逃逸的額外屏障,所以必須確保電介質(zhì)沒有那么糟糕。”

結(jié)論

自熱可能不是當今電路設(shè)計人員面臨的最大問題,但問題已經(jīng)增長到足以引起人們的關(guān)注,而且它們在未來只會變得更糟。新設(shè)備、新材料和新封裝技術(shù)都在加速這個問題,如果最大活性因子繼續(xù)下降,任何封裝中都會面臨這個問題。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論