封裝可靠性設(shè)計(jì)是指針對(duì)集成電路使用中可能出現(xiàn)的封裝失效模式,采取相應(yīng)的設(shè)計(jì)技術(shù),消除或控制失效模式,使集成電路滿足規(guī)定的可靠性要求所采取的技術(shù)活動(dòng)。封裝可靠性設(shè)計(jì)主要包括封裝可靠性結(jié)構(gòu)設(shè)計(jì)、熱設(shè)計(jì)、耐環(huán)境設(shè)計(jì)、可制造性設(shè)計(jì)等方面。???

1.封裝可靠性設(shè)計(jì)原則與方法

封裝可靠性設(shè)計(jì)應(yīng)遵循如下基本原則。

(1)可靠性設(shè)計(jì)應(yīng)有明確的封裝可靠性指標(biāo)和評(píng)估方案。 (2)可靠性設(shè)計(jì)應(yīng)貫穿于封裝結(jié)構(gòu)設(shè)計(jì)、熱設(shè)計(jì)、可制造性設(shè)計(jì)等各個(gè)環(huán)節(jié)。

(3) 最大限度地消除或控制可能出現(xiàn)的失效模式。

(4) 采用新結(jié)構(gòu)、新工藝、新材料前,嚴(yán)格論證其對(duì)封裝可靠性的影響。

(5)對(duì)性能、可靠性、成本、時(shí)間等各因素進(jìn)行權(quán)衡,制定出較優(yōu)的封裝設(shè)計(jì)方案

2.封裝可靠性設(shè)計(jì)方法

常用的封裝可靠性設(shè)計(jì)方法如下

(1)制定和貫徹可靠性設(shè)計(jì)原則.將封裝可靠性的共性內(nèi)容、成熟經(jīng)驗(yàn)和

失敗教訓(xùn)以淮則形式制定下來(lái),并貫街到封裝設(shè)計(jì)中。

(2)降額設(shè)計(jì)法:設(shè)計(jì)時(shí)降低集成電路工作時(shí)封裝所承受的熱、電、機(jī)械等各種應(yīng)力。

(3)元余設(shè)計(jì)法:如封裝中同一電源用多個(gè)引出端并聯(lián),或者合理地進(jìn)行電源冗余分布。

(4)健壯設(shè)計(jì)法:通過(guò)參數(shù)設(shè)計(jì)和容差設(shè)計(jì),使產(chǎn)品的性能對(duì)集成電路封裝過(guò)程中容許的參數(shù)波動(dòng)及使用環(huán)境容許的參數(shù)波動(dòng)不敏感

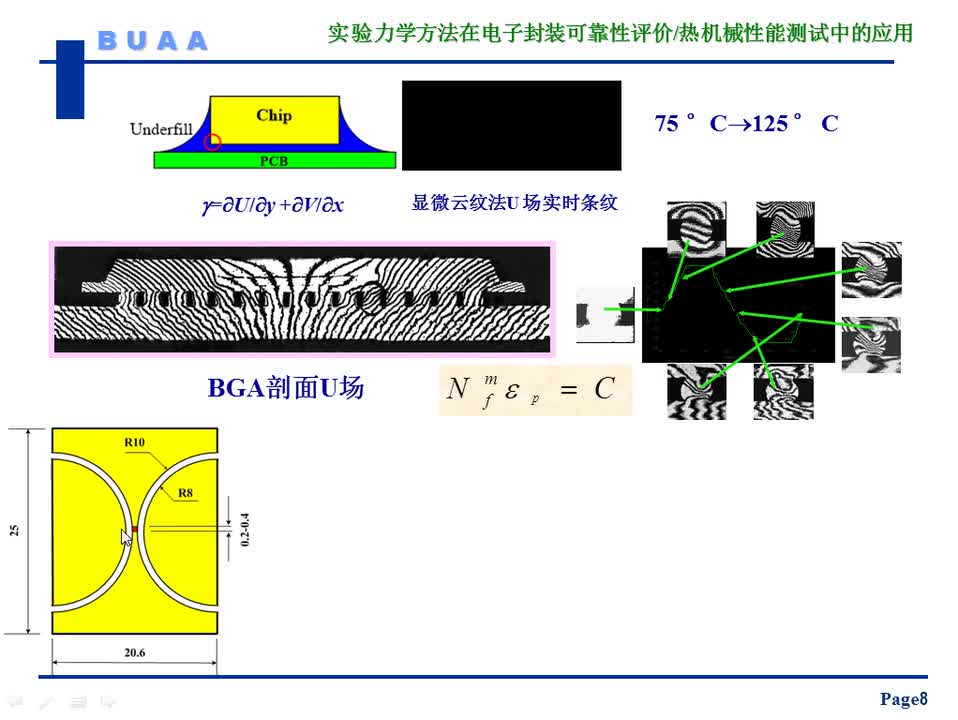

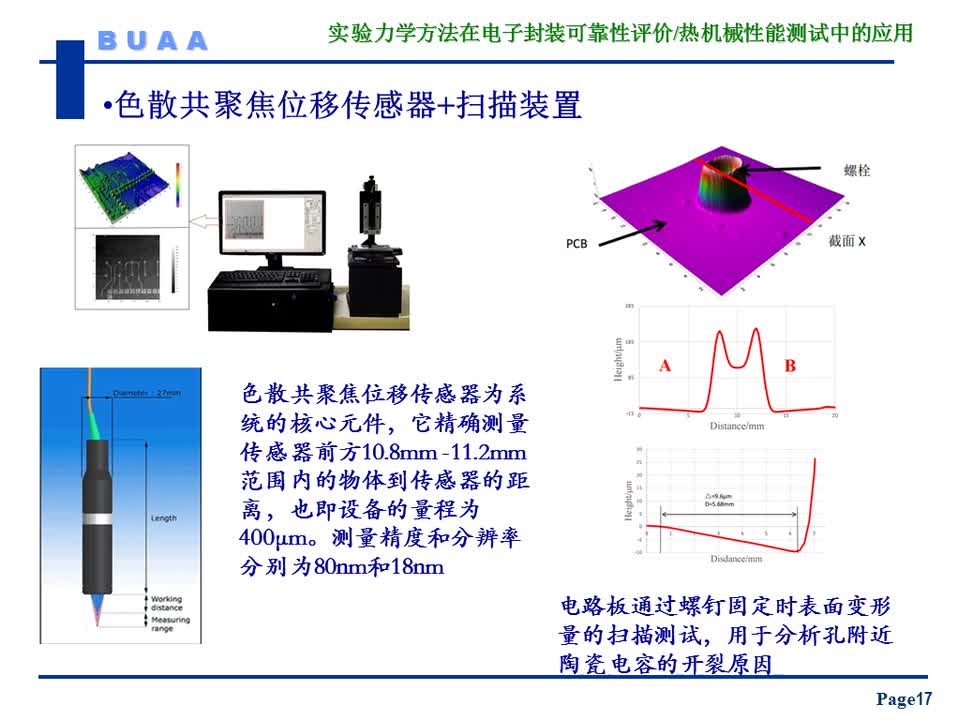

(5)模擬分析方法:如采用有限元法分析封裝結(jié)構(gòu)強(qiáng)度、熱性能等。

3. 封裝可靠性結(jié)構(gòu)設(shè)計(jì)

封裝可靠性結(jié)構(gòu)設(shè)計(jì)應(yīng)著重考慮如下 5項(xiàng)內(nèi)容。

(1)芯片在底座上的黏結(jié)強(qiáng)度,特別是工作溫度升高后,對(duì)芯片黏結(jié)強(qiáng)度有無(wú)影響。

(2)鍵合可靠性,包括子線承載電流的能力,抗沖擊、振動(dòng)等外界機(jī)械應(yīng)力的能力,鍵合焊點(diǎn)的牢固程度。

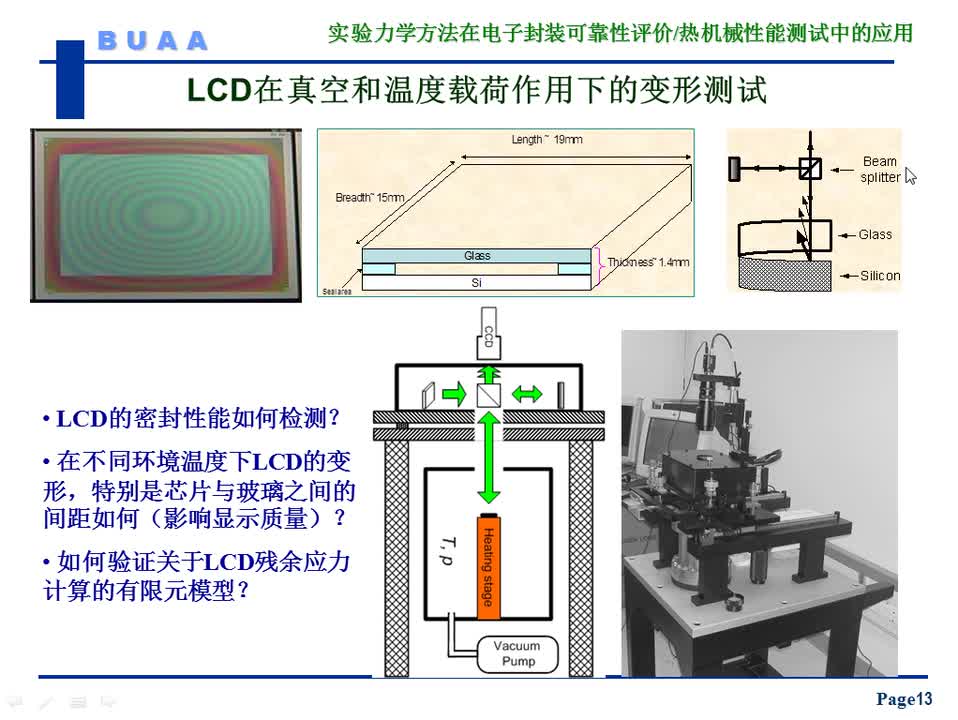

(3)封裝密封性,保護(hù)芯片不受外界惡劣環(huán)境影響。

(4)封裝引出端結(jié)構(gòu)及其強(qiáng)度設(shè)計(jì),消除或降低疲勞、磨損、斷裂等失效。

(5)封裝外引出端鍍層結(jié)構(gòu)及焊接可靠性。

4.封裝可靠性熱設(shè)計(jì)

可靠性熱設(shè)計(jì)是指根據(jù)集成電路的熱特性和傳熱學(xué) 原理,采取各種措施控制集成電路結(jié)溫,使其在容許的溫度范圍之內(nèi)。

可靠性熱設(shè)計(jì)常用的技術(shù)措施如下所述。

(1) 合理布局封裝器件(包括集成電路芯片)的位置,使高溫、低溫器件分布均衡,避免熱點(diǎn)集中。

(2) 盡可能縮短傳熱路徑,降低熱阻。

(3)在陶瓷外殼、各類基板設(shè)計(jì)中增加導(dǎo)熱孔結(jié)構(gòu),降低封裝熱阻。

(4)選用低熱阻材料,提高熱接觸表面的加工精度,或者在接觸面之間增加高導(dǎo)熱材料。

(5)增加表面黑度,提高輻射散熱效率

(6) 采取散熱片、熱管、風(fēng)扇等措施,增加熱傳導(dǎo)

5.封裝可靠性耐環(huán)境設(shè)計(jì)

在集成電路貯存、運(yùn)輸和工作過(guò)程中,會(huì)遇到各種外界環(huán)境,應(yīng)依據(jù)環(huán)境的性質(zhì)和特性,分析環(huán)境可能造成的各種影響,開(kāi)展封裝可靠性耐環(huán)境設(shè)計(jì)其中包括防潮濕設(shè)計(jì)、防鹽霧(腐蝕)設(shè)計(jì)、防霉菌設(shè)計(jì)、抗沖擊和振動(dòng)設(shè)計(jì)等。

(1)防潮濕設(shè)計(jì):采用吸濕性小且在濕熱環(huán)境中性能穩(wěn)定的材料,選擇電極電位接近的材料作為 直接接觸的金屬;對(duì)防潮性能要求較高的電路可采用氣密性封裝。

(2)防鹽霧(腐蝕)設(shè)計(jì):選擇耐鹽霧(腐蝕)材料,或者在表層進(jìn)行抗蝕涂覆處理。

(3)防霉菌設(shè)計(jì):選用防霉性能好的材料,一般要與防潮設(shè)計(jì)結(jié)合起來(lái)考慮。

(4)抗沖擊和振動(dòng)設(shè)計(jì):使集成電路的固有頻率移出振源和設(shè)備的振動(dòng)頻段,通常應(yīng)使其固有頻率達(dá)到設(shè)備固有頻率的2信以上。集成電路的固有頻率可以參照元器件的計(jì)算公式來(lái)估算,也可以用模擬試驗(yàn)方法來(lái)測(cè)定。電子產(chǎn)品受受振動(dòng)影響的頻率范圍通常為 20Hz~2kHz。

6.封裝可靠性可制造性設(shè)計(jì)

可制造性設(shè)計(jì) (Design for Manufacturability, DFM)的關(guān)鍵在于封裝設(shè)計(jì)時(shí)就考慮可制造性,其目的是便于制造和裝配,降低成本,縮短開(kāi)發(fā)周期。可制造性設(shè)計(jì)主要考慮以下三個(gè)方面。

(1)封裝用各類外殼、基板的設(shè)計(jì)需滿足材料要求、鍍層要求、最小線寬線距要求、最小板厚孔徑比要求、最小焊盤孔徑要求等;需滿足制造商的制造方法、制造工藝及工藝能力,盡量增加制造的工藝窗口,提高成品率。

(2)器件選擇:如器件耐溫性能、器件引出端鍍層材料和結(jié)構(gòu),器件與現(xiàn)有工藝的匹配性等。

(3)組裝工藝可裝配性:如焊盤結(jié)構(gòu)與尺寸,設(shè)備對(duì)設(shè)計(jì)的要求,回流焊和清洗對(duì)設(shè)計(jì)的要求,器件排布方向和間隔等。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論