半導體先進制程工藝逐步趨于極限,?繼續(xù)沿摩爾定律發(fā)展的腳步放緩,?而扇出型晶圓級封裝(?Fan-out Wafer Level Packaging,?FOWLP)通過晶圓重構的方式突破了傳統(tǒng)扇入封裝的?I/ O?引出端的數量限制,?并利用多層再 布線(Redistribution Layer,?RDL)等技術,?縮小引腳間距,?減薄封裝厚度,?降低高頻信號傳輸損耗,?從而進一步提升 芯片集成度。近年來已在消費電子、?高性能計算等領域逐漸發(fā)展成為具有代表性的先進封裝技術,?是接續(xù)摩爾定律 的關鍵技術。但?FOWLP?的可靠性問題隨著其結構精密和生產流程復雜而日益突出。結合?FOWLP?近期技術發(fā)展和 應用的現狀,?總結了發(fā)展趨勢;?從?FOWLP?結構的工藝缺陷和失效模式出發(fā),?闡述了?FOWLP?的工藝流程和重點工 藝環(huán)節(jié);?根據不同失效類型,?系統(tǒng)歸納了引發(fā)失效的物理效應和物理模型;?最后,?介紹了提升?FOWLP?結構可靠性 的工藝調整和優(yōu)化設計方法。

隨著先進納米制程已逼近物理極限,?在日益增長 的性能需求與摩爾定律逐漸失效的矛盾影響下,?Intel、?NVIDIA、?臺積電、?AMD?等老牌半導體企業(yè)紛紛加大 了疊層封裝(PoP)、?FOWLP、?硅通孔(TSV)等先進封 裝領域的投入,?要借助先進的封裝技術實現更高性能、?更低耗電量、?更小體積、?信號傳輸速度更快的產品。?

作為先進性封裝研究的重要成果之一,?FOWLP?在 移動及可穿戴設備中大獲成功,?在高性能及云計算、?自動駕駛和物聯(lián)網(?IoT)中也得到了應用。FOWLP?具 有異質集成、 3D?堆疊的潛力,?可以與多種先進封裝技 術相互組合,?是未來先進封裝技術演進的基石?。FOWLP?已在商用產品中有了扎實的使用基礎,?助力可 編程邏輯陣列?FPGA、?中央管理器?CPU、?數字信號處 理模塊?DSP?等關鍵元器件向高密度、?高性能和高可靠 性發(fā)展,?隨著軍事、?航空、?航天等領域逐漸向小體積、?輕質量、?高可靠性的方向發(fā)展,?FOWLP?將在軍用及航 空航天用器件的封裝變革中起到關鍵作用?。?

目前先進制程工藝的進步速度逐漸放緩,?且在當 前國際背景下,?受美、?日、?荷等國半導體相關行業(yè)的 出口限制,?國內先進制程工藝難以短時間內實現有效 突破。加強對以?FOWLP?為代表的先進封裝技術的發(fā) 展和應用,?可以有效促進集成電路在一定行業(yè)應用范 圍內向著更高集成度的方向繼續(xù)發(fā)展,?滿足相關應用需求。??

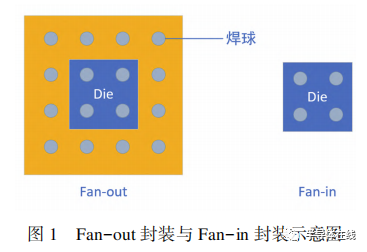

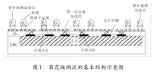

在?FOWLP?中存在兩個重要概念,?即扇出型封裝 和晶圓級封裝。如圖?1?所示,?扇出型封裝(Fan-out)是 與扇入型封裝(Fan-in)對立的概念,?傳統(tǒng)扇入型封裝 的?I/ O?接口均位于晶粒(Die)的下方,?I/ O?接口的數量 受限于芯片尺寸的大小,?隨著芯片技術的發(fā)展,?I/ O?接口的數量已經成為制約芯片性能發(fā)展的短板之一,?而扇出型封裝則可以利用重布線(RDL)技術和模塑化 合物提供的額外芯片面積,?將?I/ O?接口分布在晶粒之 外,?大大增加了芯片?I/ O?接口數量,?從而滿足芯片日 益增長的吞吐需求?。傳統(tǒng)封裝往往是將晶粒從晶圓?(Wafer)上切割下來,?再分別對晶粒進行封裝,?而晶 圓級封裝則另辟蹊徑,?先將晶圓進行整體封裝,?再進 行切割,?更適合集成電路的大規(guī)模批量生產。

縱觀集成電路封裝技術的發(fā)展歷程,?伴隨著封裝 結構的布線密度和?I/ O?接口數量的不斷上升,?封裝結 構和工藝流程日趨復雜,?引發(fā)的可靠性問題也逐漸增多?。本文第一章介紹了近幾年國內外?FOWLP?技術發(fā) 展和應用的現狀,?介紹了國內半導體廠商特色封裝技 術和先進封裝技術發(fā)展水平。第二章列舉了?FOWLP?的關鍵工藝和常用的可靠性測試方法。第三章介紹了 學術界對晶圓翹曲、?芯片偏移兩種工藝缺陷和重布線 層分層、?焊球開裂兩類失效模式的失效分析成果。第 四章介 紹 了 基 于 失 效 分 析 形 成 的 失 效 物 理 模 型 對?FOWLP?的工藝和設計進行可靠性優(yōu)化的部分典型案 例。最后展望了進一步提升?FOWLP?產品可靠性的研究方向。

1.?行業(yè)發(fā)展及應用現狀

2016?年,?臺積電(TSMC)經過在先進封裝技術上 近十年的布局和技術沉淀,?在?FOWLP?領域開發(fā)了集 成扇出型(Integrated Fan-out,?InFO)封裝技術[?,?并 成功應用于蘋果?iPhone7?系列手機的?A10?應用處理器?,?之后蘋果每一代手機應用處理器都采用臺積電 的集成扇出型封裝技術,?幫助臺積電拿下蘋果處理器 芯片制造和封裝訂單。?

在先進封裝領域,?AMD?公司將多項先進封裝技術 投入商用。Chiplet,?中文譯名芯粒或晶粒,?是近期集 成電路業(yè)界的熱點話題,?Chiplet?是指預先制造好、?具 有特定功能、?可組合集成的晶片,?該技術可以縮小單 顆芯片面積,?提高良品率,?有助于企業(yè)控制生產成本 和提高迭代速度。如何實現多芯粒之間的高速互聯(lián)是 實現?Chiplet?的技術難點,?而?FOWLP?技術的高密度重 布線工藝滿足多芯粒之間高速互聯(lián)的需求。FOWLP?技 術的發(fā)展是?Chiplet?技術走向商用的先決條件。AMD?公司在扇出型封裝技術上投入巨資,?并且在商業(yè)競爭 中率先使用先進的?FOWLP?技術,?該技術路線幫助?AMD?公司在?CPU?和?GPU?領域追趕行業(yè)先驅?Intel?和?NVIDIA。在?2019?年發(fā)布的?7?nm Zen2?架構銳龍?zhí)幚砥?中,?AMD?公司將?CPU?芯片拆分成?CCD?和?cIOD?兩部分,?其中僅有負責邏輯運算的?CCD?使用臺積電?7?nm?工藝,?對性能要求較低的?cIOD?部分使用了?12?nm?工 藝。Zen2?架構意義重大,?實現了對同期?Intel?產品的性 能追趕,?為提升?AMD?在德國等多國?CPU?市場占有率 奠定了基礎。?

在?CPU?領域通過先進封裝技術取得優(yōu)勢的?AMD?公司也試圖將?FOWLP?技術引入到?GPU?領域,?AMD?公司于?2022?年?12?月?13?日向市場推出了使用?RDNA?3?架構的?Radeon?7900XTX?顯卡,?AMD?將顯卡核心?Big Navi?3x?拆分為一個?GCD?和六個?MCD,?與?AMD?在?Zen?架構的做法相同,?負責邏輯計算的?GCD?使用了臺 積電?5?nm?工藝,?面積為?300?mm?2?,?MCD?使用了臺積 電?6?nm?工藝,?單顆面積為?37?mm2?。得益于更小的芯 片帶來更高的良率,?以及?MCD?芯片成熟工藝,?使得?AMD?的?Big Navi?3x?核心在性能對標競爭廠家?NVIDIA?的?AD102?核心的同時實現了較好的成本控制。?

Intel?公 司 結 合 自 身 在 基 板 領 域 的 積 累,?推 出?EMIB(Embedded Multi-Die Interconnect Bridge),?中文 譯名為嵌入式多核心互聯(lián)橋接。EMIB?工藝建立在標 準封裝構造流程的基礎上,?附加了創(chuàng)建?EMIB?腔的步 驟。連接橋位于空腔中,?并用粘合劑固定在適當的位 置。添加介電層和金屬堆積層,?然后進行通孔鉆孔和 電鍍。作為?CPU?行業(yè)的巨頭,?Intel?公司正試圖參與?GPU?市場競爭。在?2022?年?8?月的半導體行業(yè)會議?Hot Chips?34?上,?Intel?公司公開了一套名為?Ponte Vecchio?的服務器?GPU?架構。Intel?公司作為?GPU?行業(yè)的后來 者,?在最新推出的?GPU?產品中使用了比?AMD?公司更 先進的封裝技術。Intel?公司稱?Ponte Vecchio?內部同時 混用?Intel?7?和臺積電?N7?/ N5?等多個工藝節(jié)點,?并使用 了多達?11?處的?EMIB?結構以實現內部高速互聯(lián)。?

在超算領域,?特斯拉于?2021?年公布了?Dojo?芯片 的概念圖,?Dojo?是神經網絡訓練優(yōu)化超級計算機芯 片,?該芯片將首次使用臺積電?InFO_?SoW?(System-on?-Wafer)技術?,?Dojo?使用?6?層?RDL,?將整塊?12?英寸 重構晶圓安裝在散熱盤上,?散熱盤可以為芯片提供剛 度并將散熱能力從?7000?W?提升至?15000?W。2022 年,?FOWLP?技術在?GPU?領域得到了快速的 推廣應用, 2021?年底到?2022?年初,?馬斯克在推特上 發(fā)布多篇推文公布特斯拉自研超算?GPU?芯片,?以取代 特斯拉采購的?NVIDIA?芯片。?

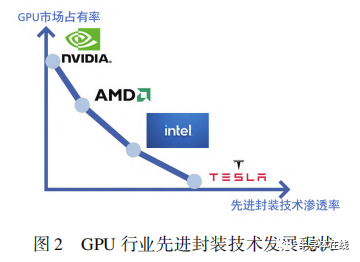

2022?年?8?月?Intel?公布全 新服 務 器?GPU?架 構, 12?月?AMD?發(fā) 售 消 費 級?GPU7900XTX,?這三家公司為了追趕行業(yè)先進水平,?使用的先 進 封 裝 技 術 越 發(fā) 激 進,?但 市 占 率 最 高 的?NVIDIA?公司仍采用了較保守的封裝方案。無論是?CPU、?GPU?還是其他集成電路產業(yè),?均呈現出越是行 業(yè)后發(fā)者,?使用的封裝技術越先進的趨勢。如圖?2?所 示,?這一趨勢在市場規(guī)模最大、?競爭最激烈的?GPU?市 場表現尤為明顯。并且,?各公司發(fā)展先進封裝技術的 戰(zhàn)略也取得了不錯的效果,?NVIDIA?公司各類?GPU?產 品線均受到巨大挑戰(zhàn)。觀察這種趨勢對國內半導體行 業(yè)的發(fā)展很有參考價值,?促進?FOWLP?等先進封裝技 術的發(fā)展和應用對于試圖參與?GPU?市場競爭的集成電 路企業(yè)是很有意義的。

在宇航領域,?NASA?在?2015?年公布的封裝技術路 線圖 中 將?2. 5D/?3D?-?TSV?技 術 納 入 封 裝 技 術 路 線, 2018?年啟動對?2. 5D?封裝產品的考核方案和路線圖。在美國國家航空航天局電子零件和包裝計劃(National Aeronautics and Space Administration Electronic Parts and Packaging,?NEPP)的贊助下,?美國加州理工學院噴氣 動 力 實 驗 室?(?California Institute of Technology Jet Propulsion Laboratory,?JPL)?的?Ghaffarian?通過一系列 的可靠性實驗系統(tǒng)論證了?2. 5D?封裝產品的可靠性,?他認為?FOWLP?產品擁有更小的體積重量、?更大的邏 輯運算和存儲能力,?而且其可靠性鑒定結果足以滿足?NASA?對空間飛行器電子元器件的可靠性要求,?并希 望他的研究成果可以促進?NASA?對?FOWLP?等先進封 裝技術的使用。?

我國半導體封裝企業(yè)也在?FOWLP?領域取得了一 系列創(chuàng)新成果。硅基扇出型晶圓級封裝?(?Embedded Silicon Fan-out,?eSiFO)?是?2015?年由華天科技于大全 教授提出。硅基扇出型封裝這一技術路線相比于樹脂 扇出型封裝,?具有成本低、?翹曲小、?布線密度高、?散 熱良好和制程簡單等優(yōu)勢,?更容易實現大芯片系統(tǒng)集 成。該工藝被使用于電源管理芯片、?射頻收發(fā)器芯片、基帶處理器和高端網絡系統(tǒng)等多種應用領域,?

廈門云天半導體開發(fā)了?eGFO?嵌入式玻璃封裝技 術。玻璃絕緣性好,?高溫下不易膨脹,?透光性強,?適 合高頻的射頻應用和光電應用。玻璃上可以直接做光 路,?滿足光電共封裝的需求,?光電射頻領域也是云天?eGFO?技術的主要應用領域。但是玻璃具有易開裂的 特性,?在玻璃上開孔和挖出嵌埋區(qū)域工藝難度高、?效 率低。產品良率是目前制約廈門云天使用玻璃作為載 體的最大因素。?

中電五十八所的晶圓級封裝工藝平臺是目前國內先進、?自主可控的高可靠?12?英寸(兼容?8?英寸)?晶圓級制造加工線,?同時也是國防科技工業(yè)認可的信息處 理微系統(tǒng)加工制造平臺。自?2017?年通線以來,?平臺已 經具備高可靠?12?英寸的晶圓級再布線制備、?晶圓級凸 點制備、?圓片重構等多項晶圓級扇出型集成技術。部 分工藝技術能力(晶圓級封裝尺寸、?凸點直徑等)達到國際領先水平。同時具備有鉛低輻射凸點(Bump)?制 備、?單芯片批量化凸點生長以及可重構三維封裝等特 色服務,?可滿足軍用及宇航長壽命使用要求,?已先后 為國內多家用戶單位提供了?GNC?飛行控制、?AD/ DA?集成、?信號截取處理模塊等數字信息處理微系統(tǒng)產品 的加工服務,?滿足了相關微系統(tǒng)產品小型化、?高性能、?高可靠的應用需求。?

航天?772?所通過近幾年技術攻關和自主研發(fā),?已 初步具備 小 尺 寸 多 芯 粒 硅 基 集 成 技 術 能 力。針 對?Chiplet?芯粒集成多級互連要求,?面向?40 μm?以下超微 凸點鍵合,?突破面陣列固態(tài)互連等關鍵技術,?實現了 低溫焊接、?高溫服役的全流程穩(wěn)定工藝;?并采用耐濕?“內防護”?結構以及改性耐高溫材料,?實現了節(jié)距小 于?100 μm,?凸點數大于?10000?個的均勻沉積和致密防 滲集成工藝。?

通富微電?2021?年披露其在高性能計算領域建成了 國內頂級?2. 5D/?3D?封裝平臺?(?VISions)?及超大尺寸?FCBGA?研發(fā)平臺,?且完成了高層數再布線技術的開 發(fā),?具備大規(guī)模生產?Chiplet?封裝能力,?目前在?CPU、?GPU、?服務器領域?5?nm?即將量產。其?Fan-out?技術已 經達到世界先進水平,?高密度扇出型封裝平臺完成?6?層?RDL?開發(fā)。?

XDFOI?是長電科技?2021?年推出全系列極高密度 扇出型封裝解決方案,?并于?2022?年下半年量產。該封 裝解決方案是新型無硅通孔晶圓級極高密度封裝技術,?相較于?2. 5D?硅通孔(TSV)?封裝技術,?具備更高性能、?更高可靠性以及更低成本等特性。該解決方案在線寬 或線距達到?2 μm?的同時,?可實現多層布線層,?另外,?采用了極窄節(jié)距凸塊互聯(lián)技術,?封裝尺寸大可集成多 顆芯片、?高帶寬內存和無源器件。XDFOI?主要集中于 對集成度和算力有較高要求的?FPGA、?CPU、?GPU、?AI?和?5G?網絡芯片等應用產品提供小芯片?(Chiplet)?和異 質封裝?(HiP)?的系統(tǒng)封裝解決方案。?2022?年?7?月?22?日,?長電科技發(fā)文稱,?公司在先進封測技術領域取得 新的突破,?實現?4?nm?工藝制程手機芯片的封裝以及?CPU、?GPU?和射頻芯片的集成封裝。?

我國?FOWLP?技術與國外先進水平相比差距較小,?且各企業(yè)均有自身的特色技術,?但在高密度重布線和 超大面積扇出型封裝技術等領域尚有差距。

2?關鍵工藝和可靠性評價

FOWLP?的工藝流程復雜,?包括晶圓重構、?塑封、?重布線等,?每一步關鍵工藝都會對封裝可靠性造成嚴 重影響。?

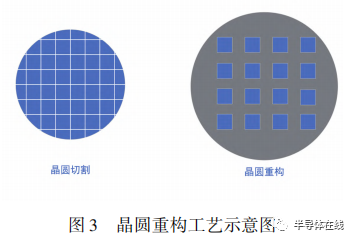

晶圓重構是指將從晶圓上分割下來的晶粒重新貼 裝在臨時載體上形成重構晶圓,?如圖?3?所示。晶圓重 構技術要求較好的定位精度,?既需要良好的粘貼強度,?也需要易于剝離,?否則會導致芯片偏移?。

塑封工藝可以保護芯片并擴展芯片面積,?環(huán)氧塑 封料會在受熱后液化,?包裹住晶粒,?并在冷卻后固化。環(huán)氧塑封料的熱膨脹系數與其他材料之間存在較大的 不匹配,?注塑時產生的液體流動也可能會改變晶粒位 置,?造成晶圓翹曲和芯片偏移。?

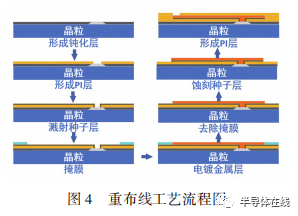

重布線技術是實現扇出效果的關鍵技術,?如圖?4?所示,?該技術首先在晶粒表面覆上鈍化層和?PI?層,?再 通過金屬濺射、?掩膜曝光的方法制造金屬層圖案,?并 使用電鍍法填充金屬層,?反復多次,?在晶粒和塑封料 表面交替制作金屬層和聚酰亞胺層,?最終形成多層重 布線層,?實現對?I/ O?接口的重新排布。由于金屬和聚酰亞胺熱膨脹系數不同,?在溫度變化時若重布線層 強度不足會引發(fā)重布線層開裂。

FOWLP?在應用過程中常見的失效模式包括重布 線層分層和焊球開裂。菊花鏈測試鏈路可以實時監(jiān)測 和定位?FOWLP?失效[9] ,?便于后續(xù)對失效封裝結構失 效分析。溫度循環(huán)試驗和沖擊試驗可以充分暴露潛在 失效。?

菊花鏈(Daisy Chain)測試鏈路是表征先進封裝結 構可靠性的常用方法,?它可以高效率地實時監(jiān)測封裝 結構是否在環(huán)境測試中發(fā)生失效,?并鎖定發(fā)生失效的 大概位置。菊花鏈測試鏈路可以在?I/ O?接口中建立多 條鏈路,?一旦封裝結構在某處發(fā)生失效,?就會改變該 處的橫截面積、?長度和電氣參數,?失效位置所在鏈路 的電流也會因為電阻值的改變而變化,?從而實現對封 裝結構失效狀態(tài)的監(jiān)控和失效位置的估計。?

在發(fā)現失效現象后可以使用超聲波掃描電子顯微 鏡?(SAM)、?掃描電子顯微鏡?(?SEM) 、?能量色散?X?射線光譜儀(EDX)、?X?射線能譜儀?(EDS)等工具和手 段對失效點位進行定位和失效分析。超聲波掃描電子 顯微鏡和能量色散?X?射線光譜儀可以精準定位失效位 置。掃描電子顯微鏡可以得到失效點位的清晰圖像,?有助于了解斷裂、?分層、?錯位等現象的具體原因。通 過能譜分析對失效點位附近材料的成分進行分析,?可 以追溯因工藝流程中原材料純度不足、?對上一工藝環(huán) 節(jié)殘余物清洗和剝離不夠充分或生產環(huán)境不夠純凈等 原因導致的失效。?

溫度循環(huán)試驗和沖擊試驗可以使?jié)撛诘牟季€層分 層和焊球開裂失效充分暴露。重布線層中的金屬層和 聚酰亞胺層在溫度循環(huán)測試時反復膨脹收縮,?二者熱 膨脹系數不同,?若重布線層強度不足則會開裂。沖擊 和溫度循環(huán)導致焊球處發(fā)生熱應力和機械應力集中,?若產品設計不合理或封裝工藝不達標,?則會導致焊球開裂。根據聯(lián)合電子器件工程委員會(?Joint Electron Device Engineering Council,?JEDEC)?發(fā)布的有關標準?JESD22-A104,?封裝可靠性測試中溫度循環(huán)試驗的 熱范圍為-40~ 125?℃,?循環(huán)測試的次數均為?1000?次,?沖擊測試的強度為?1500?g / ms。在實際工作中,?可靠 性環(huán)境試驗會根據集成電路產片生命周期中所經歷的 環(huán)境進行調整,?比如航空航天電子產品會對沖擊強度 測試進行加嚴,?汽車電子產品可能會擴大溫度循環(huán)范 圍或增加高溫存儲實驗(HTS)等項目。有些集成電路 產品在生產流程中會使用一些特殊工藝,?產品可能會 經歷極端環(huán)境變化,?這也需要調整測試環(huán)境。有針對 性的可靠性測試有助于精準的評價封裝結構的可靠性,?從而合理地對結構和工藝或劃定適應的產品貯存、?運 輸和工作環(huán)境范圍。?

3?主要工藝缺陷和失效模式

分析晶圓翹曲、?芯片偏移兩種工藝缺陷和重布線 層分層、?焊球開裂兩類失效模式的作用機理并建構物 理模型是進行工藝改進和可靠性優(yōu)化改進的基礎。?

3. 1?晶圓翹曲?

晶圓翹曲是指重構晶圓在加工過程因熱機械應力 的累積而在宏觀上產生翹曲。晶圓翹曲會降低后續(xù)掩 膜光刻的工藝精度,?限制再布線層密度的提升。翹 曲產生的應力易在中介層或焊點處集中,?造成焊球開 裂脫落和中介層分層。晶圓尺寸越大,?晶圓所受的熱 和機械應力越強,?局部曲率越高,?翹曲現象越嚴重。隨著大尺寸晶圓在晶圓級封裝的應用,?晶圓翹曲問題 已經成為制約?FOWLP?發(fā)展的突出問題。?

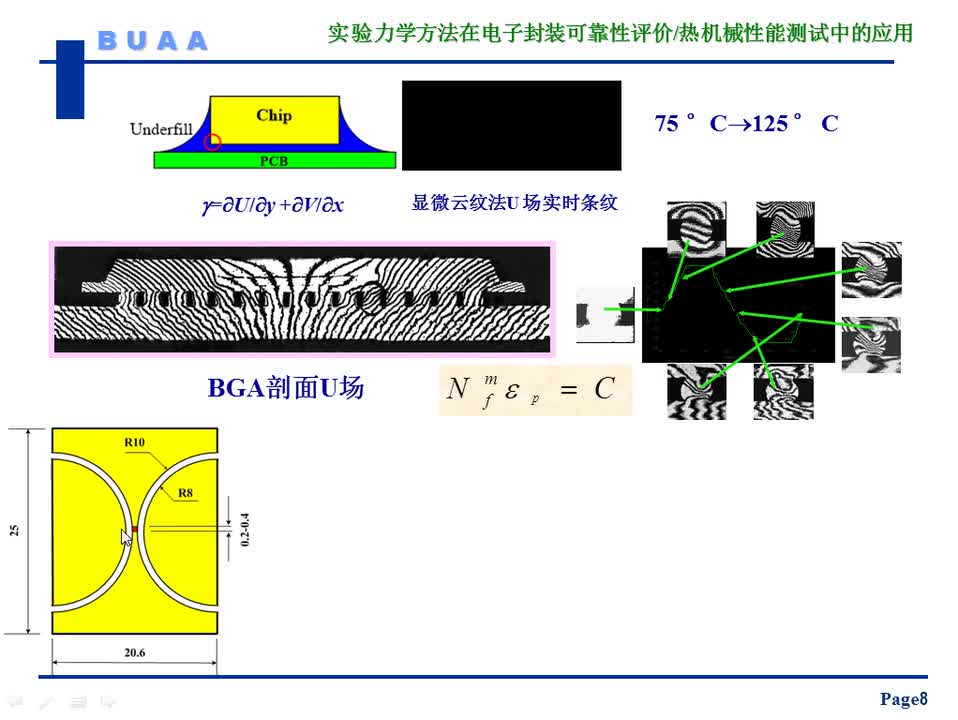

由于晶圓表面易被劃傷,?業(yè)界通常采用光學手段 對晶圓翹曲進行測量,?依據原理可以大致劃分為光學 干涉測量 和 激 光 掃 描 測 量,?前 者 包 括 影 子 云 紋 法?(Shadow Moire)、?投影云紋法(?Projection Moire)?和泰 曼-格林干涉法(Twyman-Green)等,?通過光柵干涉 圖像表征晶圓曲率,?后者則是通過激光對晶圓整體進 行掃描定位,?最后通過計算機擬合出晶圓翹曲的情況。?

采用合適的方法對重構晶圓所含材料進行測量和 表征是分析引發(fā)晶圓翹曲多種應力的前提。Cheng?等使 用 差 示 掃 描 量 熱 法?(?Differential Scanning Calorimetry,?DSC?)?和 動 態(tài) 力 學 分 析?(?Dynamic Mechanical Analysis,?DMA)評估固化狀態(tài),?使用熱機 械分析儀(?Thermomechanical Analyzer,?TMA)?表征了 環(huán)氧塑封料的楊氏模量和熱膨脹系數,?為分析各類應 力的強度和不同翹曲形態(tài)的成因提供了有力支持。

環(huán)氧塑封料固化引發(fā)的體積收縮和不同材料的熱 膨脹系數不匹配被公認為是造成晶圓翹曲的最主要原因,?但隨著研究的深入,?尤其是通過分析傳統(tǒng)理論 模型和實際結果之間的偏差,?近年來發(fā)現了更多影響 晶圓翹曲的因素。Dijk?等和?Chiu?等發(fā)現硅的各 向異性和環(huán)氧塑封料的粘彈性松弛效應對翹曲也有一 定影響,?固化工藝之后的工藝環(huán)節(jié),?尤其是再布線和 植球等存在劇烈溫度變化的工藝會對晶圓翹曲產生影 響。Chiu?還通過實驗和建模分析認為環(huán)氧塑封料的化 學收縮對翹曲的影響微不足道。Cheng?等通過分 析環(huán)氧塑封料的固化過程發(fā)現重力會對晶圓翹曲產生 影響。?

張振越等基于雙層圓形板彎曲理論與復合材料 等效方法,?提出?FOWLP?圓片翹曲理論解析表達式。實現對翹曲的快速預測。Chen?等使用頻域動態(tài)力 學分析表征了?EMC?和?PI?的線性粘彈性,?將粘彈性模 型用于對固化結構的有限元分析,?實現了對晶圓翹曲 的精準預測。Li?等結合材料微觀力學模型,?針對異 構集成結構建立物理模型,?通過建模調整參數使得?8?英寸晶圓翹曲控制在?2?mm?以內。

近幾年來,?業(yè)界深入分析了晶圓翹曲的成因,?表 征了翹曲程度和引發(fā)翹曲的應力,?支撐了業(yè)界工藝流 程參數優(yōu)化 。

3. 2?芯片偏移?

芯片偏移是指晶粒偏離應有位置。芯片偏移現象 可以通過高倍顯微鏡觀察發(fā)現,?這既可能是晶圓重構 精度不足造成的,?也有可能是后續(xù)工藝環(huán)節(jié)產生的應 力導致的。引發(fā)芯片偏移的應力主要包含兩種。主要 的一種是由固化成型期間環(huán)氧塑封料的流動誘導阻力 引起的流體流動(Fluid Flow,?FF)。另一個是由封裝的 熱膨脹/?收縮、?環(huán)氧塑封料的固化收縮和晶圓翹曲引起 的熱機械(Thermo-Mechanical,?TM)應力?。與晶圓 翹曲類似,?芯片偏移也會降低再布線工藝中光刻的工 藝精度,?并導致芯片鏈路產生開路。?

為了分析兩種應力對芯片偏移的影響,?業(yè)界通過 建模和試驗對兩種應力的強度和作用機制進行了分析。Cheng?等基于某種環(huán)氧塑封料建立了流體動力學 模型用以研究液體流動對芯片偏移的影響,?發(fā)現重構 晶圓邊緣處的晶粒芯片偏移最為嚴重,?分析認為熱機 械效應和誘導阻力造成的應力具有相似的作用機制,?都是越靠近邊緣應力越大。Wu?等通過建模比較了 熱機械應力和流體流動的強度,?認為熱機械效應對芯 片偏移產生更多影響。Ouyang?等根據目前已經發(fā) 現的影響芯片偏移的應力,?針對聚二甲基硅氧烷這一 特殊的塑封料建立流體動力學模型,?實現對塑封過程 中翹曲變化的預測。Shao?等[26]通過比對不同種類粘合 劑的粘附強度和使用不同粘合劑對芯片偏移產生的影 響,?發(fā)現晶圓重構工藝中臨時載體的黏附力不足是造 成芯片偏移問題最直接的原因。?

相較于晶圓翹曲,?引發(fā)芯片偏移的應力種類較少,?芯片偏移的失效機制較為清晰。?

3. 3?焊點開裂?

由于?FOWLP?的?I/ O?接口數量越來越多,?FOWLP?的尺寸和焊點密度均有所提升。在焊點的體積變小的 同時單個焊點所受應力越來越高,?所以焊點的可靠性 問題日益突出。?

對焊點進行建模有助于對焊點可靠性進行預計,?便于工藝改進和設計優(yōu)化,?Lau?等建立了非線性、?時間和溫度相關的三維有限元模型,?采用線性加速因 子將測試條件下的焊點可靠性映射到操作條件下的焊 接點可靠性,?得到了置信度為?90%的封裝特征壽命。Wang?等基于能量法描述和預測焊點形狀,?當液體 達到靜態(tài)平衡時,?其總能量趨于最低,?表面積趨于最 小。液體的能量主要包括表面張力能、?重力能和外能。根據總能量,?可以計算重力方向上的恢復力,?進而估 算焊球的形狀和高度,?并基于?Coffin-Manson?應變的 經驗模型估計焊點的疲勞壽命。Lee?等建立了一種 非線性模擬方法,?用于研究制造過程和熱循環(huán)實驗的 耦合效應。在有限元建模中分析了焊料凸臺的塑性和 蠕變行為,?研究了?SnAg?焊料凸臺中累積的非彈性應 變。還對相關幾何尺寸和底部填充材料進行了參數化分析。?

在不同環(huán)境壓力下,?焊球的失效模式表現不同。Cho?等[通過可靠性試驗發(fā)現在跌落試驗中,?焊球界 面斷裂和?PCB?焊盤出現凹坑是主要失效模式,?而在溫 度循環(huán)試驗中,?焊球界面斷裂和重布線層出現裂紋是 主要失效模式。?

除此之外,?在對焊球質量的批量化監(jiān)測方面,?Lu?等用掃描聲學顯微鏡對樣本進行測試,?并使用聚類 模糊?C?均值(FCM)算法對焊點進行識別。訓練所得學 習模型可應用于高密度焊點可靠性的快速檢測。業(yè)界對焊點可靠性的研究相對成熟,?對引發(fā)焊點 應力集中的作用機制已有充足的探索,?建立了可信度 較高的焊點物理模型。?

3. 4?重布線層分層?

重布線 層 中 最 常 用 的 有 機 材 料 包 括 聚 酰 亞 胺(Polyimide,?PI)、?聚苯并惡唑(Polybenzoxazole,?PBO)?和苯并環(huán)丁烯(Benzocyclobutene,?BCB),?除此之外還 有酚醛樹脂等材料,?其中?PBO?機械強度最高但是熱膨 脹系數過高,?BCB?勝在優(yōu)良的電學性能,?但是機械強 度最差。Gao?等[32]將酚醛樹脂等三種材料與?PI?進行比 較,?認為?PI?具有超過?30%的優(yōu)異伸長率和?52×10 -6?/ K?的熱膨脹系數,?是目前性能最均衡的?RDL?有機材料。PI?是目前重布線層中最常用的有機材料。但是?PI?固化 溫度過高,?普通的?PI?固化溫度超過?300?℃,?經過改良 的低溫固化?PI?的固化溫度也在?200?℃以上,?對工藝設 計的優(yōu)化要求較高。Okada?等[33]?通過試驗比較了兩種?PI、?PBO?和酚醛樹脂在銅表面的臨界能量釋放率,?并 根據實驗曲線建立了可以模擬任意溫度下分層可能性 的仿真模型。?

重布線層分層常發(fā)生在溫度循環(huán)測試之后,?重布 線層不同材料層經歷反復的熱脹冷縮,?材料間界面的 疲勞應力導致開裂。沖擊測試中也會發(fā)現重布線層分 層現象,?Lau?等通過試驗估算了重布線層的特征壽 命,?并發(fā)現封裝最大應力出現在受到沖擊后的?0. 0023?s,?位置在封裝四角,?最下層的重布線層所受應力最 大,?易發(fā)生開裂現象。?

重布線層分層是扇出型封裝中常見的失效模式,?但是重布線層結構和重布線工藝流程復雜,?結構和材 料個性化強,?重布線層仿真難度高,?需要針對不同的 封裝結構單獨進行分析。?

4?工藝改進和可靠性優(yōu)化設計?

通過實驗和仿真可以快速對工藝進行迭代,?優(yōu)化 工藝參數,?從而提升產品良率。依靠成熟的失效物理 模型對封裝結構進行優(yōu)化是改善產品可靠性的有效方法。

4. 1?工藝改進?

晶圓翹曲的曲率、?形狀和方向在制造工藝中經歷 了劇烈的變化,?其中最大翹曲并沒有發(fā)生在其工藝流 程結束時,?而是發(fā)生在去載流子環(huán)節(jié),?所以對于高產 率工藝操作,?應連續(xù)監(jiān)測和有效控制每個工藝步驟的 翹曲,?而不是僅進行末端監(jiān)控。Wu?等使用可調溫 度熱室模擬重構晶圓在后續(xù)工藝環(huán)節(jié)中經歷的溫度變 化,?并改進了一種干涉測量工具,?實現對晶圓翹曲的 全局熱變形分析,?從而改進工藝參數。Cheng?等通過實驗發(fā)現晶圓厚度與翹曲程度并非簡單的線性關 系,?當晶圓厚度低于?0. 6?mm?時,?晶圓越厚,?材料熱 失配導致的晶圓翹曲程度越高,?但是由于晶圓本身的 彎曲剛度與晶圓厚度的平方成正比,?所以當晶圓厚度 超過?0. 6?mm?時,?晶圓的彎曲剛度會隨厚度快速上升,?從而抑制晶圓翹曲。通過對生產工藝的觀察,?Cheng?等還注意到重構晶圓上晶粒間距越大,?晶粒邊長越長,?翹曲越小。?

引發(fā)芯片偏移的兩大要素分別是液體流動和熱機 械效應。通過降低塑封工藝速度和模具固化溫度、?縮 小晶粒間距和晶粒厚度以及增加環(huán)氧塑封料的厚度,?可以減少液體流動帶來的阻力,?從而減少芯片偏移。通過縮小環(huán)氧塑封料厚度,?使用低熱膨脹系數的臨時 載體,?增加晶粒的間距和厚度,?可以減少熱機械效應 引起的芯片偏移。可以看到減少液體流動阻力的措施 與減少熱機械效應的措施之間存在沖突,?所以需要對 工藝參數進行權衡。針對不同的封裝結構反復建模和 試驗,?才能使芯片偏移最小化?。?

Zhang?等通過大量的材料學試驗尋找植球工藝 的最佳參數,?在低焊接溫度和短焊接時間下,?焊點和 焊盤之間的冶金反應不足,?剪切力低。隨著焊接溫度 和時間的增加,?焊料球和焊盤之間的反應更完全,?機 械性能逐漸提高。然而,?隨著峰值溫度和持續(xù)時間的 增加,?焊料球的氧化程度增加,?導致焊點出現孔洞,?焊球下金屬間化合物厚度增加,?導致脆性增加,?剪切 力降低。經過權衡,?在?260?℃下, (Cu,?Ni)6Sn5?晶體 呈現規(guī)則的分布,?金屬間化合物達到一定的密度,?同 時也較少產生孔洞,?所以?260?℃?持續(xù)?10?s?是一個比較 優(yōu)秀的焊接參數。?

重布線工藝中生產環(huán)境潔凈度不足或對前一工藝 環(huán)節(jié)殘余物清洗不徹底,?導致重布線層內部出現沾污 是導致重布線層分層的原因之一。在工藝環(huán)節(jié)中應嚴 格監(jiān)控生產環(huán)境,?及時使用能譜分析技術分析重布線 層分層的封裝器件,?找出引發(fā)分層的有機化合物并追 溯來源,?并及時整改是十分有必要的。在重布線工藝 中選擇熱膨脹系數與金屬層匹配度較高、?分界層粘性 大的有機材料是減少分層的關鍵。減材制造是制備重 布線層的傳統(tǒng)方法,?Roshanghias?等[38]嘗試使用打印技 術實現重布線層的增材制造,?認為新的工藝方法在抵 抗重布線層分層問題上具有潛力,?并討論了增材制造 技術面臨的工藝難點。?

4. 2?可靠性優(yōu)化設計?

除了進行工藝參數的改進,?通過對封裝結構進行 可靠性優(yōu)化設計也能有效提升?FOWLP?的可靠性。?

Tsai?等發(fā)現,?在?FOWLP?上粘貼一個金屬框架 可以降低封裝翹曲和底部焊點所受應力。但是金屬框架的熱膨脹系數和金屬框架粘結劑的彈性模量會對效 果產生影響,?所以應根據情況謹慎選擇金屬框架材料,?粘合劑彈性模量應控制在?50?MPa?以下。?

晶圓翹曲和芯片偏移均與模塑化合物的性能相關,?C an?等分析了使用液體模塑化合物?(Liquid Molding ompound,?LMC)取代?EMC?的可能性,?LMC?流動性 強有助于抑制晶圓翹曲且成本更低,?但是對模塑工藝 的工藝控制要求更高。Andriani?等[通過在?EMC?中添 加六方氮化硼來改善?EMC?的熱力學性能,?并分析了 不同濃度的六方氮化硼對?EMC?熱力學性能的影響。?

Jung?等通過在環(huán)氧塑封料中嵌入不同形狀的銀 片有效降低翹曲,?改善芯片散熱。環(huán)氧塑封料導熱性 差,?在高溫固化時固化速度不均勻,?加入銀片可以使 固化速度更加均勻,?從而減輕翹曲。位于晶粒正上方 扇入區(qū)域的銀片還可以顯著改善散熱,?但在扇入區(qū)域 嵌入銀片也會增加封裝整體厚度。?

通常認為使用散熱器可以降低芯片的實際工作溫 度,?有助于緩解因熱機械效應導致的封裝失效。但是?Nayini?等將使用散熱器和不使用散熱器的封裝結構 進行了對照,?發(fā)現加裝散熱器可能會導致焊點壽命下 降,?因為散熱器會限制芯片變形,?將芯片內部因熱失 配產生的應力傳遞給焊點。雖然高溫會減少焊點壽命,?但是不合適的散熱方法可能會進一步加劇可靠性問題。?

Lee?等發(fā)現上、?下焊盤直徑和緩沖層厚度顯著 影響扇出型封裝焊點的可靠性壽命。當上焊盤大于下 焊盤時,?焊點的可靠性更高,?推薦的上下焊盤大小比 例為?1 ∶ 0. 72,?較厚的緩沖層分擔了焊點的應力集中,?從而對焊點的可靠性壽命產生了積極影響。較薄的芯 片厚度可以釋放焊點的應變芯片,?減小焊料凸塊的非 彈性應變增量,?低楊氏模量底部填充材料也可以起到 應力緩沖的作用。?

Lee?等提出了三種無直角轉彎的重布線層設計 方案,?并與含有直角轉彎布線的原始方案進行對比,?發(fā)現合理的重布線層設計方案可以避免局部積熱,?改 善重布線層的力學性能,?提升了在溫度循環(huán)測試中的可靠性。

5?總結與展望?

FOWLP?已在消費級和工業(yè)級半導體制造領域大 規(guī)模應用,?也在高可靠領域得到了初步應用,?是未來 商業(yè)競爭的重點方向。學術界和工業(yè)界已經針對不同 失效 現 象 建 立 了?FOWLP?的 可 靠 性 物 理 模 型,?對?FOWLP?的失效機理有了較為清晰的認識,?針對性地進 行了工藝改進和可靠性設計優(yōu)化。但是由于封裝結構 復雜度的提升以及多種應力耦合關系過于復雜,?僅靠 失效機理的相關研究已經難以指導工藝和設計的深化 改進。通過機器學習和深度學習將工藝過程、?設計參 數與產品良率、?可靠性參數之間建立數學關系和數學 模型,?可能是指導工藝和設計改進、?進一步提升產品 可靠性的可行之路。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論