隨著上游芯片產(chǎn)能不斷擴(kuò)產(chǎn),封裝行業(yè)已經(jīng)步入微利時(shí)代,許多企業(yè)為了搶奪客戶大打價(jià)格牌,激烈的價(jià)格競(jìng)爭(zhēng)和無(wú)序的業(yè)內(nèi)生態(tài)鏈促使行業(yè)開(kāi)始需求新的封裝工藝。而具有提升發(fā)光效率以及提高散熱能力等優(yōu)勢(shì)的倒裝LED芯片技術(shù)的革新與應(yīng)用正是當(dāng)今封裝企業(yè)專注研發(fā)的重點(diǎn)。

2014-05-17 10:12:16 2286

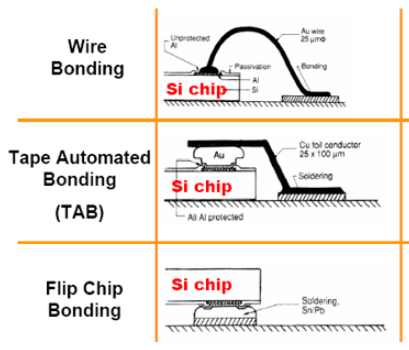

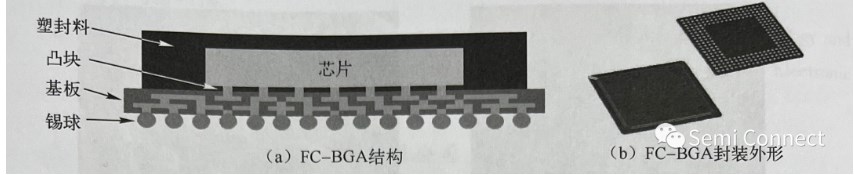

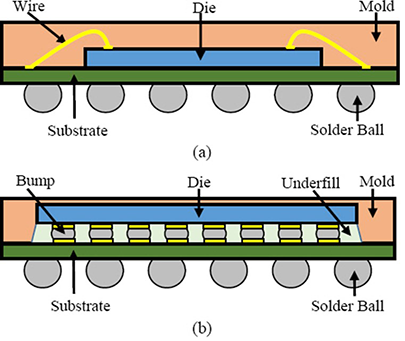

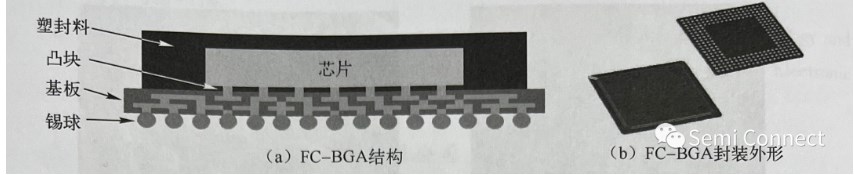

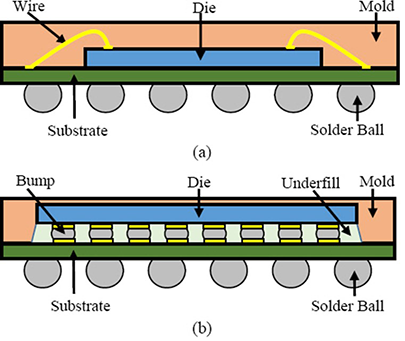

2286 倒裝芯片工藝是指通過(guò)在芯片的I/0 焊盤(pán)上直接沉積,或者通過(guò) RDL 布線后沉積凸塊(包括錫鉛球、無(wú)鉛錫球、銅桂凸點(diǎn)及金凸點(diǎn)等),然后將芯片翻轉(zhuǎn),進(jìn)行加熱,使熔融的焊料與基板或框架相結(jié)合,將芯片的 I/0 扇出成所需求的封裝過(guò)程。倒裝芯片封裝產(chǎn)品示意圖如圖所示。

2023-04-28 09:51:34 3701

3701

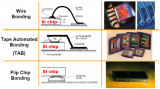

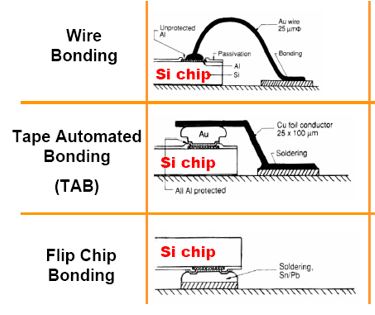

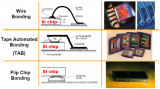

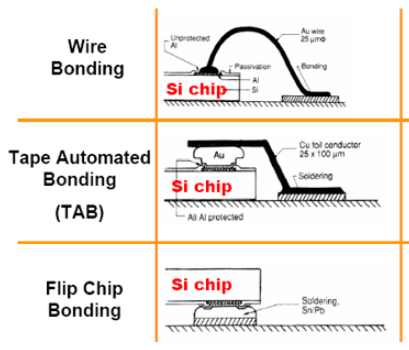

從事半導(dǎo)體行業(yè),尤其是半導(dǎo)體封裝行業(yè)的人,總繞不開(kāi)幾種封裝工藝,那就是芯片粘接、引線鍵合、倒裝連接技術(shù)。

2023-07-21 10:08:08 3128

3128

從事半導(dǎo)體行業(yè),尤其是半導(dǎo)體封裝行業(yè)的人,總繞不開(kāi)幾種封裝工藝,那就是芯片粘接、引線鍵合、倒裝連接技術(shù)。

2023-08-01 11:48:08 1174

1174

在半導(dǎo)體制造領(lǐng)域,芯片裝配(Chip Mounting)是一個(gè)至關(guān)重要的環(huán)節(jié)。特別是在LED產(chǎn)業(yè)中,正裝芯片和倒裝芯片的選擇會(huì)直接影響產(chǎn)品的性能、穩(wěn)定性和成本。本文將詳細(xì)對(duì)比正裝芯片與倒裝芯片的各方面區(qū)別,幫助您更準(zhǔn)確地選擇適合您需求的產(chǎn)品。

2023-09-04 09:33:05 2719

2719

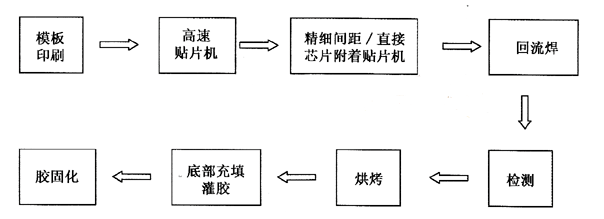

底部填充工藝就是將環(huán)氧樹(shù)脂膠水點(diǎn)涂在倒裝晶片邊緣,通過(guò)“毛細(xì)管效應(yīng)”,膠水被吸往元件的對(duì)側(cè)完成底 部充填過(guò)程,然后在加熱的情況下膠水固化。為了加快膠水填充的速度,往往還需要對(duì)基板進(jìn)行預(yù)熱。利用

2018-09-06 16:40:41

倒裝晶片元件損壞的原因是什么?

2021-04-25 06:27:25

要處理細(xì)小焊球間距的倒裝晶片的影像,需要百萬(wàn)像素的數(shù)碼相機(jī)。較高像素的數(shù)碼相機(jī)有較高的放大倍率, 但像素越高,視像區(qū)域(FOV)越小,這意味著大的元件可能需要多次影像。照相機(jī)的光源一般為

2018-11-27 10:53:33

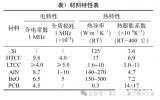

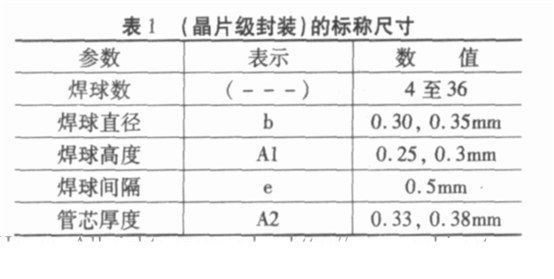

過(guò)程中分解進(jìn)入焊點(diǎn)。 了解造成各種缺陷的根本原因,有利于我們采取得當(dāng)?shù)拇胧﹣?lái)解決及預(yù)防各種可能出現(xiàn)的缺陷。表1列出 的是在倒裝晶片組裝工藝中常見(jiàn)的缺陷及原因分析,并針對(duì)各缺陷提出了改善措施,以方便工程技術(shù)人員在 工藝過(guò)程中快速有效地找出問(wèn)題的根本原因,幫助采取正確的解決或預(yù)防方法。表1常見(jiàn)缺陷及原因分析

2018-09-06 16:40:06

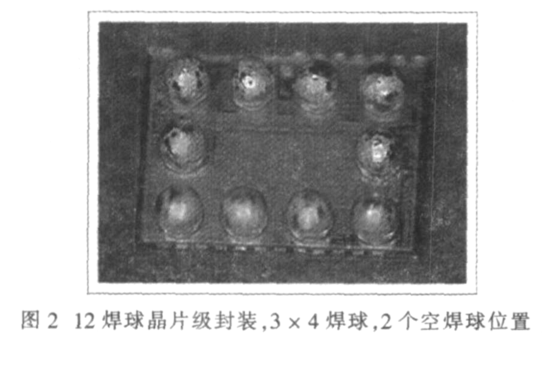

什么元件被稱為倒裝晶片(FC)?一般來(lái)說(shuō),這類元件具備以下特點(diǎn)。 ①基材是硅; ②電氣面及焊凸在元件下表面; ③球間距一股為0.1~0.3 mm,球徑為0.06~0,.15 mm,外形尺寸

2018-11-22 11:01:58

基板技術(shù)是倒裝晶片工藝需要應(yīng)對(duì)的最大挑戰(zhàn)。因?yàn)槌叽绾苄。ㄐ〉脑〉那驈剑〉那蜷g距,小的貼裝 目標(biāo)),基板的變動(dòng)可能對(duì)制程良率有很大影響: ·密間距貼裝良率極易受限于阻焊膜和焊盤(pán)的尺寸公差

2018-11-27 10:47:46

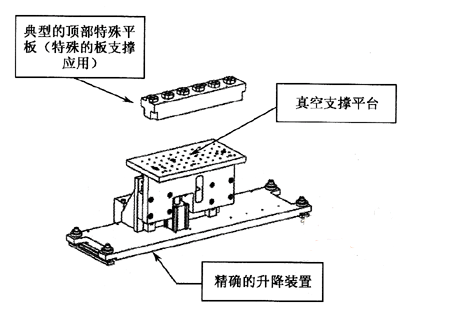

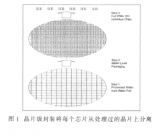

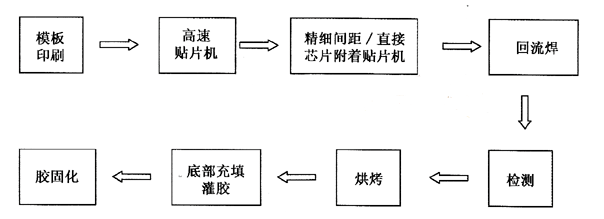

。然后再通過(guò)第二條生產(chǎn)線處理部分組裝的模 塊,該生產(chǎn)線由倒裝芯片貼片機(jī)和回流焊爐組成。底部填充工藝在專用底部填充生產(chǎn)線中完成,或與倒裝芯片生 產(chǎn)線結(jié)合完成。如圖1所示。圖1 倒裝晶片裝配的混合工藝流程

2018-11-23 16:00:22

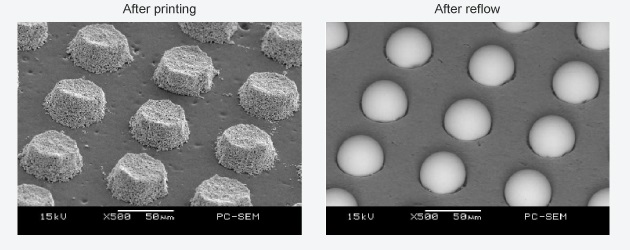

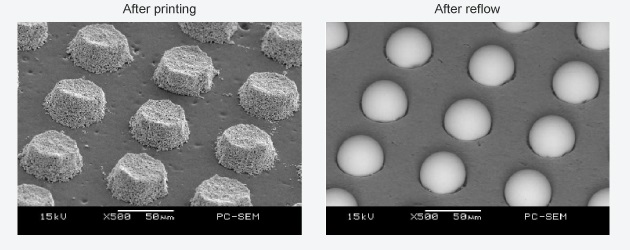

及老 化測(cè)試。 由于倒裝晶片焊點(diǎn)在元件的下面,直接檢查非常困難,利用X射線檢查儀能夠觀察到一些焊接缺陷: 可以觀察到焊接過(guò)程中倒裝晶片具有非常好的“自對(duì)中性”,在氮?dú)夂附迎h(huán)境中尤其突出。如圖1和圖2

2018-11-23 15:59:22

助焊劑工藝在倒裝晶片裝配工藝中非常重要。助焊劑不僅要在焊接過(guò)程中提供其化學(xué)性能以驅(qū)除氧化物和油污 ,潤(rùn)濕焊接面,提高可焊性,同時(shí)需要起到黏接劑的作用。在元件貼裝過(guò)程中和回流焊接之前黏住元件,使其

2018-11-23 15:44:25

在回流焊接爐中,倒裝晶片和其他元件要被焊接在基板上。在此過(guò)程中,如果加熱的溫度太高,或者時(shí)間太長(zhǎng) ,助焊劑便會(huì)在潤(rùn)濕整個(gè)焊接面之前揮發(fā)或分解完,造成潤(rùn)濕不良或其他焊接缺陷。另外,在復(fù)雜的混合裝配

2018-11-23 15:41:18

由于倒裝晶片韓球及球問(wèn)距非常小,相對(duì)于BGA的裝配,其需要更高的貼裝精度。同時(shí)也需要關(guān)注從晶片被吸 取到貼裝完成這一過(guò)程。在以下過(guò)程中,元件都有可能被損壞: ·拾取元件; ·影像處理

2018-11-22 11:02:17

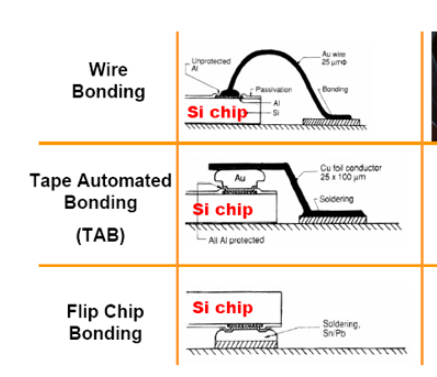

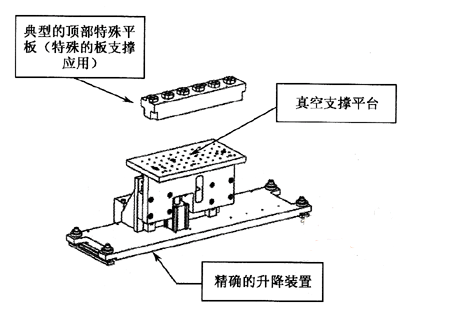

有些倒裝晶片應(yīng)用在柔性電路板或薄型電路板上,這時(shí)候?qū)宓钠秸畏浅jP(guān)鍵。解決方案往往會(huì)用到載 板和真空吸附系統(tǒng),以形成一個(gè)平整的支撐及精確的定位系統(tǒng),滿足以下要求: ①基板Z方向的精確支撐

2018-11-23 15:45:30

倒裝晶片(Flip Chip)貼裝屬于先進(jìn)半導(dǎo)體組裝(Advanced Semiconductor Assembly),常見(jiàn)的應(yīng)用有無(wú)線天線、藍(lán)牙、硬盤(pán)磁頭、元件封裝、智能傳感器和一些醫(yī)用高精密

2018-11-27 10:45:28

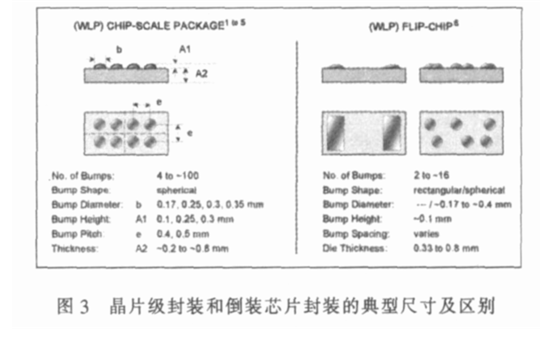

WLP的命名上還存在分歧。CSP晶片級(jí)技術(shù)非常獨(dú)特,封裝內(nèi)部并沒(méi)有采用鍵合方式。封裝芯片的命名也存在分歧。常用名稱有:倒裝芯片(STMicroelectronics和Dalias

2018-08-27 15:45:31

、高密度便攜式電子設(shè)備的制造所必須的一項(xiàng)技術(shù)。在低成本應(yīng)用中,倒裝芯片的成功是因?yàn)樗蛇_(dá)到相對(duì)于傳統(tǒng)表面貼裝元件包裝更大的成本效益。例如,一款新的尋呼機(jī)利用了倒裝芯片技術(shù)將微控制器裝配于PCB,因?yàn)?b class="flag-6" style="color: red">倒裝

2019-05-28 08:01:45

1.倒裝芯片焊接的概念 倒裝芯片焊接(Flip-chipBonding)技術(shù)是一種新興的微電子封裝技術(shù),它將工作面(有源區(qū)面)上制有凸點(diǎn)電極的芯片朝下,與基板布線層直接鍵合。 2.倒裝芯片

2020-07-06 17:53:32

本文作者:深圳大元倒裝COB顯示屏是真正的芯片級(jí)封裝,擺脫了物理空間尺寸的限制,使點(diǎn)間距有了更進(jìn)一步下鉆的能力。倒裝COB顯示屏廠家--深圳大元倒裝COB顯示屏與LED小間距相比:1、倒裝cob

2020-05-28 17:33:22

以來(lái)迅速發(fā)展的新型微電子封裝技術(shù),包括焊球陣列封裝(BGA)、芯片尺寸封裝(CSP)、圓片級(jí)封裝(WLP)、三維封裝(3D)和系統(tǒng)封裝(SIP)等項(xiàng)技術(shù)。介紹它們的發(fā)展?fàn)顩r和技術(shù)特點(diǎn)。同時(shí),敘述了微電子

2023-12-11 01:02:56

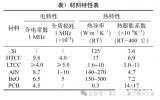

鮮 飛(烽火通信科技股份有限公司,湖北 武漢 430074)摘 要:微電子技術(shù)的飛速發(fā)展也同時(shí)推動(dòng)了新型芯片封裝技術(shù)的研究和開(kāi)發(fā)。本文主要介紹了幾種芯片封裝技術(shù)的特點(diǎn),并對(duì)未來(lái)的發(fā)展趨勢(shì)及方向進(jìn)行了

2018-11-23 16:59:52

降低印刷線路板的復(fù)雜度和成本。這種設(shè)計(jì)大大縮小了封裝尺寸,并擴(kuò)大了PCB基板面上每平方英尺的性能。 EI可使用其系統(tǒng)級(jí)封裝技術(shù),將PCB基板面積較原始PCB減少多達(dá)27倍。具體操作辦法是:以裸芯片

2018-08-27 15:24:28

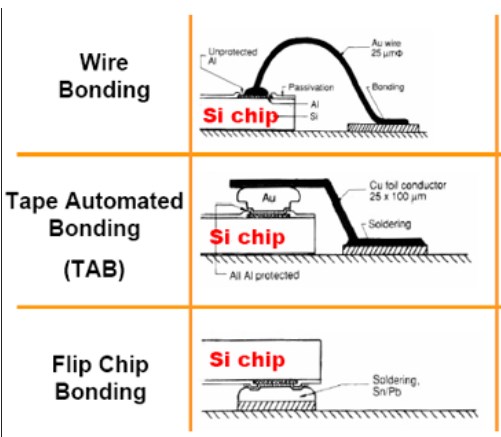

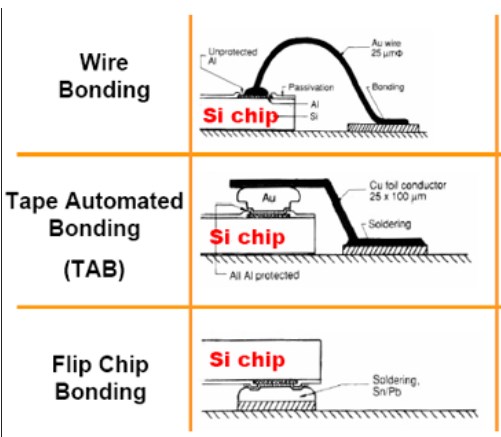

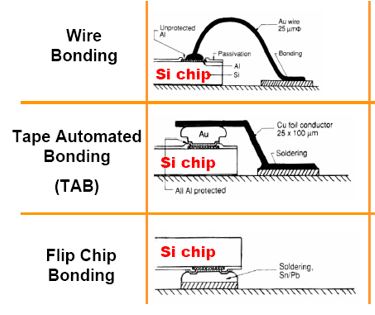

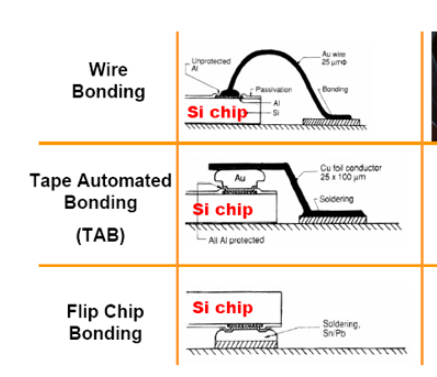

提供封裝,組裝及測(cè)試的可靠支持。以往的一級(jí)封閉技術(shù)都是將芯片的有源區(qū)面朝上,背對(duì)基板和貼后鍵合,如引線健合和載帶自動(dòng)健全(TAB)。FC則將芯片有源區(qū)面對(duì)基板,通過(guò)芯片上呈陣列排列的焊料凸點(diǎn)實(shí)現(xiàn)芯片

2018-09-11 15:20:04

MEMS器件有時(shí)也采用晶圓級(jí)封裝,并用保護(hù)帽把MEMS密封起來(lái),實(shí)現(xiàn)與外部環(huán)境的隔離或在下次封裝前對(duì)MEMS器件提供移動(dòng)保護(hù)。這項(xiàng)技術(shù)常常用于慣性芯片的封裝,如陀螺儀和加速度計(jì)。這樣的封裝步驟是在MEMS

2010-12-29 15:44:12

金鑒檢測(cè)在大量LED失效案例總結(jié)的基礎(chǔ)上,發(fā)現(xiàn)用硅膠封裝、銀膠粘結(jié)的垂直倒裝芯片易出現(xiàn)漏電現(xiàn)象。這是因?yàn)椋枘z具有吸水透氣的物理特性,易使導(dǎo)電銀膠受潮,水分子侵入后在含銀導(dǎo)體表面電解形成氫離子

2015-06-12 11:44:02

金鑒檢測(cè)在大量LED失效案例總結(jié)的基礎(chǔ)上,發(fā)現(xiàn)用硅膠封裝、銀膠粘結(jié)的垂直倒裝芯片易出現(xiàn)漏電現(xiàn)象。這是因?yàn)椋枘z具有吸水透氣的物理特性,易使導(dǎo)電銀膠受潮,水分子侵入后在含銀導(dǎo)體表面電解形成氫離子

2015-06-19 15:28:29

`晶圓級(jí)封裝(WLP)就是在其上已經(jīng)有某些電路微結(jié)構(gòu)(好比古董)的晶片(好比座墊)與另一塊經(jīng)腐蝕帶有空腔的晶片(好比玻璃罩)用化學(xué)鍵結(jié)合在一起。在這些電路微結(jié)構(gòu)體的上面就形成了一個(gè)帶有密閉空腔的保護(hù)

2011-12-01 13:58:36

在封裝技術(shù)卜的反映。提出了目前和可預(yù)見(jiàn)的將來(lái)引線鍵合作為半導(dǎo)體封裝內(nèi)部連接的主流方式與高性能儷成本的倒裝芯片長(zhǎng)期共存,共同和硅片鍵合應(yīng)用在SiP、MCM、3D等新型封裝當(dāng)中的預(yù)測(cè)。1 半導(dǎo)體封裝外部

2018-11-23 17:03:35

論述了微電子封裝技術(shù)的發(fā)展歷程 發(fā)展現(xiàn)狀及發(fā)展趨勢(shì) 主要介紹了微電子封裝技術(shù)中的芯片級(jí)互聯(lián)技術(shù)與微電子裝聯(lián)技術(shù) 芯片級(jí)互聯(lián)技術(shù)包括引線鍵合技術(shù) 載帶自動(dòng)焊技術(shù) 倒裝芯片技術(shù) 倒裝芯片技術(shù)是目前

2013-12-24 16:55:06

尊敬的先生/女士,我想找出所有VIRTEX-6的半導(dǎo)體安裝技術(shù),是倒裝芯片安裝技術(shù)的芯片嗎?謝謝問(wèn)候,缺口

2020-06-15 16:30:12

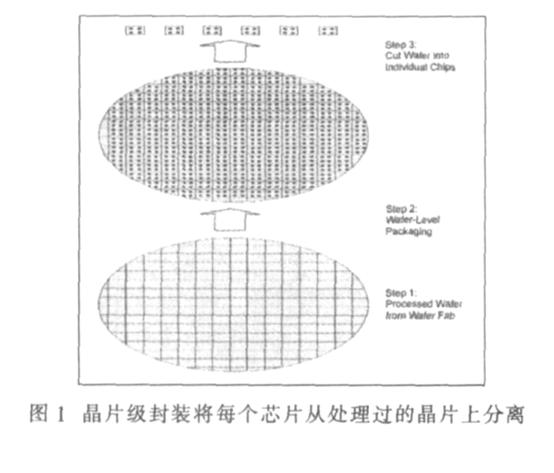

晶圓級(jí)封裝技術(shù)源自于倒裝芯片。晶圓級(jí)封裝的開(kāi)發(fā)主要是由集成器件制造廠家(IBM)率先啟動(dòng)。1964年,美國(guó)IBM公司在其M360計(jì)算器中最先采用了FCOB焊料凸點(diǎn)倒裝芯片器件。

2020-03-06 09:02:23

晶圓級(jí)芯片封裝技術(shù)是對(duì)整片晶圓進(jìn)行封裝測(cè)試后再切割得到單個(gè)成品芯片的技術(shù),封裝后的芯片尺寸與裸片一致。

2019-09-18 09:02:14

晶圓級(jí)CSP的裝配對(duì)貼裝壓力控制、貼裝精度及穩(wěn)定性、照相機(jī)和影像處理技術(shù)、吸嘴的選擇、助焊劑應(yīng) 用單元和供料器,以及板支撐及定位系統(tǒng)的要求類似倒裝晶片對(duì)設(shè)備的要求。WLCSP貼裝工藝的控制可以參

2018-09-06 16:32:18

先進(jìn)封裝發(fā)展背景晶圓級(jí)三維封裝技術(shù)發(fā)展

2020-12-28 07:15:50

封裝技術(shù)(倒裝芯片接合和柔性載板)正好適用于這個(gè)應(yīng)用。倒裝芯片接合技術(shù)已經(jīng)發(fā)展30多年了。此一技術(shù)的優(yōu)點(diǎn)是體積小、接線密度高,而且因?yàn)橐_短而電性得以改善4。倒裝芯片接合技術(shù)的另一個(gè)優(yōu)勢(shì),是能夠?qū)⒍鄠€(gè)

2018-09-11 16:05:39

隨著集成電路設(shè)計(jì)師將更復(fù)雜的功能嵌入更狹小的空間,異構(gòu)集成包括器件的3D堆疊已成為混合與連接各種功能技術(shù)的一種更為實(shí)用且經(jīng)濟(jì)的方式。作為異構(gòu)集成平臺(tái)之一,高密度扇出型晶圓級(jí)封裝技術(shù)正獲得越來(lái)越多

2020-07-07 11:04:42

金鑒檢測(cè)在大量LED失效案例總結(jié)的基礎(chǔ)上,發(fā)現(xiàn)用硅膠封裝、銀膠粘結(jié)的垂直倒裝芯片易出現(xiàn)漏電現(xiàn)象。這是因?yàn)椋枘z具有吸水透氣的物理特性,易使導(dǎo)電銀膠受潮,水分子侵入后在含銀導(dǎo)體表面電解形成氫離子

2015-05-13 11:23:43

的性能發(fā)展,縱觀近幾年的電子封裝產(chǎn)業(yè),其發(fā)展趨勢(shì)如下:●電子封裝技術(shù)繼續(xù)朝著超高密度的方向發(fā)展,出現(xiàn)了三維封裝、多芯片封裝(MCP)和系統(tǒng)級(jí)封裝(SIP)等超高密度的封裝形式。 ●電子封裝技術(shù)繼續(xù)

2018-08-23 12:47:17

在消費(fèi)類產(chǎn)品小型化和更輕、更薄發(fā)展趨勢(shì)的推動(dòng)下,廠商開(kāi)發(fā)了更小的封裝類型。實(shí)際上,封裝已經(jīng)成為新設(shè)計(jì)中選擇還是放棄某一器件的關(guān)鍵因素。本文首先定義了“倒裝芯片

2009-04-27 10:53:55 49

49 介紹了微機(jī)電(MEMS)封裝技術(shù),包括晶片級(jí)封裝、單芯片封裝和多芯片封裝、模塊式封裝與倒裝焊3種很有前景的封裝技術(shù)。指出了MEMS封裝的幾個(gè)可靠性問(wèn)題,最后,對(duì)MEMS封裝的發(fā)展趨勢(shì)

2009-12-29 23:58:16 42

42 隨著新型基底材料的出現(xiàn),倒裝芯片技術(shù)面臨著新的挑戰(zhàn),工程師們必須解決裸片

2006-04-16 21:05:16 2035

2035 摘要:晶片級(jí)封裝(WLP)允許集成電路(IC)面向下安裝在印刷電路板(PCB)上,芯片的焊盤(pán)通過(guò)單獨(dú)的焊點(diǎn)與PCB連接。本文討論了晶片級(jí)封裝技術(shù)及其優(yōu)勢(shì),描述了Maxim WLP的PCB布局和安裝流

2009-04-21 11:36:53 1566

1566 摘要:在消費(fèi)類產(chǎn)品小型化和更輕、更薄發(fā)展趨勢(shì)的推動(dòng)下,廠商開(kāi)發(fā)了更小的封裝類型。實(shí)際上,封裝已經(jīng)成為新設(shè)計(jì)中選擇還是放棄某一器件的關(guān)鍵因素。本文首先定義了“倒

2009-05-09 09:07:44 1373

1373 國(guó)際整流器公司的晶片級(jí)封裝(Wafer Level Package)器件將最近的芯片設(shè)計(jì)與最新的封裝技術(shù)結(jié)合使具有最可能小的體積。首先使用WLP 技術(shù)的產(chǎn)品是HEXFET 功率MOSFET 器件的FlipFET 系列,F(xiàn)lipFET

2011-05-19 18:18:46 0

0 倒裝芯片的成功實(shí)現(xiàn)與使用包含諸多設(shè)計(jì)、工藝、設(shè)備與材料因素。只有對(duì)每一個(gè)因素都加以認(rèn)真考慮和對(duì)待才能夠促進(jìn)工藝和技術(shù)的不斷完善和進(jìn)步,才能滿足應(yīng)用領(lǐng)域?qū)?b class="flag-6" style="color: red">倒裝芯片技

2011-07-05 11:56:17 1673

1673 隨著倒裝芯片封裝在成本和性能上的不斷改進(jìn), 倒裝芯片 技術(shù)正在逐步取代引線鍵合的位置。倒裝芯片的基本概念就是拿來(lái)一顆芯片,在連接點(diǎn)位置放上導(dǎo)電的凸點(diǎn),將該面翻轉(zhuǎn),有

2011-10-19 11:42:55 4889

4889 倒裝芯片互連技術(shù)有諸多優(yōu)點(diǎn),但是由于其成本高,不能夠用于大批量生產(chǎn)中,所以其應(yīng)用受到限制。而本文推薦使用的有機(jī)材料的方法能夠解決上述的問(wèn)題。晶圓植球工藝的誕對(duì)于降

2011-12-22 14:35:52 86

86 器件的小型化高密度封裝形式越來(lái)越多,如多模塊封裝(MCM)、系統(tǒng)封裝(SiP)、倒裝芯片(FC,F(xiàn)lip-Chip)等應(yīng)用得越來(lái)越多。這些技術(shù)的出現(xiàn)更加模糊了一級(jí)封裝與二級(jí)裝配之間的界

2012-01-09 16:07:47 46

46 芯片級(jí)封裝介紹本應(yīng)用筆記提供指引使用與PCB安裝設(shè)備相關(guān)的芯片級(jí)封裝。包括系統(tǒng)的PCB布局信息制造業(yè)工程師和制造工藝工藝工程師。 包概述 倒裝芯片CSP的包概述半導(dǎo)體封裝提供的芯片級(jí)封裝代表最小

2017-03-31 10:57:32 45

45 超級(jí)CSP——讓倒裝芯片獲得最大可靠性一種晶圓片級(jí)封裝

2017-09-14 11:31:37 22

22 芯片圖解 為了避免正裝芯片中因電極擠占發(fā)光面積從而影響發(fā)光效率,芯片研發(fā)人員設(shè)計(jì)了倒裝結(jié)構(gòu),即把正裝芯片倒置,使發(fā)光層激發(fā)出的光直接從電極的另一面發(fā)出(襯底最終被剝?nèi)ィ?b class="flag-6" style="color: red">芯片材料是透明的),同時(shí),針對(duì)倒裝設(shè)計(jì)出方便LED封裝廠焊線的結(jié)構(gòu)

2017-09-29 17:18:43 72

72 過(guò)來(lái),故稱其為倒裝晶片。 倒裝芯片的實(shí)質(zhì)是在傳統(tǒng)工藝的基礎(chǔ)上,將芯片的發(fā)光區(qū)與電極區(qū)不設(shè)計(jì)在同一個(gè)平面這時(shí)則由電極區(qū)面朝向燈杯底部進(jìn)行貼裝,可以省掉焊線這一工序,但是對(duì)固晶這段工藝的精度要求較高,一般很難達(dá)到較高的良率。 倒裝晶片

2017-10-24 10:12:25 8

8 于1月開(kāi)始進(jìn)入量產(chǎn)。這是克服現(xiàn)有倒裝芯片 LED 封裝的品質(zhì)極限,并能夠擴(kuò)大其應(yīng)用范圍的創(chuàng)新性產(chǎn)品。 LG Innotek 利用最尖端半導(dǎo)體技術(shù),開(kāi)發(fā)了巨大提升產(chǎn)品可靠性的高品質(zhì)倒裝芯片 LED 封裝。以此實(shí)現(xiàn)了中功率及高功率下的高光效、高光速高級(jí)照明的產(chǎn)品化。

2018-02-12 18:24:00 2904

2904

由于倒裝芯片的出光效率高、散熱條件好、單位面積的出光功率大、可靠性高、批量化制造成本低和能夠承受大電流驅(qū)動(dòng)等一系列優(yōu)點(diǎn),使得倒裝LED照明技術(shù)具有很高的性價(jià)比。

2019-08-30 11:02:34 3429

3429 倒裝芯片(Flip chip)是一種無(wú)引腳結(jié)構(gòu),一般含有電路單元。 設(shè)計(jì)用于通過(guò)適當(dāng)數(shù)量的位于其面上的錫球(導(dǎo)電性粘合劑所覆蓋),在電氣上和機(jī)械上連接于電路。

2019-10-22 14:21:06 11727

11727 、高密度便攜式電子設(shè)備的制造所必須的一項(xiàng)技術(shù)。在低成本應(yīng)用中,倒裝芯片的成功是因?yàn)樗蛇_(dá)到相對(duì)于傳統(tǒng)表面貼裝元件包裝更大的成本效益。例如,一款新的尋呼機(jī)利用了倒裝芯片技術(shù)將微控制器裝配于PCB,因?yàn)?b class="flag-6" style="color: red">倒裝芯片使用較少的電路板空間,比傳統(tǒng)的

2020-10-13 10:43:00 0

0 倒裝芯片FC、晶圓級(jí)CSP、晶圓級(jí)封裝WLP主要應(yīng)用在新一代手機(jī)、DVD、PDA、模塊等。 一、倒裝芯片FC 倒裝芯片定義為可能不進(jìn)行再分布的晶圓。通常,錫球小于150um,球間距小于350um

2020-09-28 14:31:30 5721

5721 倒裝晶片自60年代誕生后,這個(gè)技術(shù)已逐漸替換常規(guī)的打線接合,逐漸成為封裝潮流,為高端器件及高密度封裝領(lǐng)域中經(jīng)常采用的封裝形式。倒裝晶片主要應(yīng)用在無(wú)線局域網(wǎng)絡(luò)天線、系統(tǒng)封裝、多芯片模塊、圖像傳感器

2021-03-25 10:37:18 2837

2837 LED芯片也被稱為L(zhǎng)ED發(fā)光芯片,是LED燈的核心組件,其主要材料為單晶硅,也就是將單晶硅經(jīng)過(guò)切割而成的晶片附在一個(gè)支架上并封裝起來(lái)。其中晶片由兩部分組成,一部分是P型半導(dǎo)體,在它里面空穴占主導(dǎo)地位

2021-11-17 16:29:28 22216

22216 倒裝芯片 CSP 封裝

2022-11-14 21:07:58 19

19 替代引線鍵合最常用、先進(jìn)的互連技術(shù)是倒裝芯片技術(shù)稱為C4,即可控塌陷芯片連接(Controlled Collapse Chip Connection)或FC(Flip Chip,倒裝芯片)。這項(xiàng)技術(shù)

2023-01-12 17:48:05 3978

3978 Flip-Chip BGA (FC-BGA)是指將芯片利用倒裝(FC)技術(shù)焊接在線路基板上,并制成倒裝芯片 BGA 封裝形式。

2023-04-28 15:09:13 4514

4514

FC-CSP 是芯片級(jí)尺寸封裝(CSP)形式中的一種。根據(jù)J-STD-012 標(biāo)準(zhǔn)的定義口,CSP 是指封裝體尺寸不超過(guò)裸芯片 1.2倍的一種封裝形式,它通過(guò)凸塊與基板倒裝焊方式實(shí)現(xiàn)芯片與基板的電氣

2023-05-04 16:19:13 2513

2513

正在開(kāi)發(fā)新的凸點(diǎn)結(jié)構(gòu)以在倒裝芯片封裝中實(shí)現(xiàn)更高的互連密度,但它們復(fù)雜、昂貴且越來(lái)越難以制造。

2023-05-22 09:46:51 578

578

漢思新材料研發(fā)生產(chǎn)半導(dǎo)體(Flipchip)倒裝芯片封裝用底部填充材料為了解決一些與更薄的倒裝芯片封裝相關(guān)的問(wèn)題,漢思化學(xué)研發(fā)了一種底部填充材料,作用在于通過(guò)控制芯片和基板的翹曲來(lái)降低封裝產(chǎn)品的應(yīng)力

2023-03-01 05:00:00 536

536

本文要點(diǎn)將引線鍵合連接到半導(dǎo)體的過(guò)程可以根據(jù)力、超聲波能量和溫度的應(yīng)用進(jìn)行分類。倒裝芯片技術(shù)使用稱為凸塊的小金屬球進(jìn)行連接。在倒裝芯片QFN封裝中,倒裝芯片互連集成在QFN主體中。基于倒裝芯片QFN

2023-03-31 10:31:57 1313

1313

燈COB燈等。NU520倒裝LED恒流驅(qū)動(dòng)器芯片片來(lái)自數(shù)能Numen研發(fā)的倒裝COB恒流燈帶無(wú)焊線封裝工藝,恒流裸片(NU520)直接與PCB板一體化,整個(gè)流程更簡(jiǎn)潔化,封裝層無(wú)焊線空間,封裝層更輕薄,降低熱阻,提升光品質(zhì).產(chǎn)品性能更穩(wěn)定節(jié)能舒適等優(yōu)勢(shì)。1:LED倒裝芯片最佳伴侶2:倒裝一

2023-06-20 16:17:03 0

0 底部填充膠被填充在芯片與基板之間的間隙,來(lái)降低芯片與基板熱膨脹系數(shù)不匹配產(chǎn)生的應(yīng)力,提高封裝的穩(wěn)定性。

2023-07-31 10:53:43 387

387

先進(jìn)的倒裝芯片封裝技術(shù)由于具有較高的單位面積內(nèi) I/O 數(shù)量、短的信號(hào)路徑、高的散熱性、良好的電學(xué)和熱力學(xué)性能,在電子封裝中被廣泛關(guān)注。

2023-08-01 10:08:25 260

260

從事半導(dǎo)體行業(yè),尤其是半導(dǎo)體封裝行業(yè)的人,總繞不開(kāi)幾種封裝工藝,那就是芯片粘接、引線鍵合、倒裝連接技術(shù)。

2023-08-18 09:55:04 1632

1632

華為技術(shù)有限公司日前公開(kāi)了一項(xiàng)名為“具有改進(jìn)的熱性能的倒裝芯片封裝”專利,申請(qǐng)公布號(hào)為CN116601748A。

2023-08-18 11:14:43 1037

1037 從國(guó)家知識(shí)產(chǎn)權(quán)局官網(wǎng)獲悉,華為技術(shù)有限公司日前公開(kāi)了一項(xiàng)名為“具有改進(jìn)的熱性能的倒裝芯片封裝”專利,申請(qǐng)公布號(hào)為CN116601748A。

2023-08-18 15:19:06 528

528

從事半導(dǎo)體行業(yè),尤其是半導(dǎo)體封裝行業(yè)的人,總繞不開(kāi)幾種封裝工藝,那就是芯片粘接、引線鍵合、倒裝連接技術(shù)。

2023-08-21 11:05:14 524

524

倒裝芯片技術(shù)是通過(guò)芯片上的凸點(diǎn)直接將元器件朝下互連到基板、載體或者電路板上。引線鍵合的連接方式是將芯片的正面朝上,通過(guò)引線(通常是金線)將芯片與線路板連接。

2023-08-22 10:08:28 2166

2166

有些倒裝晶片應(yīng)用在柔性電路板或薄型電路板上,這時(shí)候?qū)宓钠秸畏浅jP(guān)鍵。解決方案往往會(huì)用到載 板和真空吸附系統(tǒng),以形成一個(gè)平整的支撐及的定位系統(tǒng),滿足以下要求:

2023-09-21 15:26:17 126

126

要滿足批量高速高良率的生產(chǎn),供料技術(shù)也相當(dāng)關(guān)鍵。倒裝晶片的包裝方式主要有2×2和4×4 in JEDEC盤(pán), 20O mm或300 mm晶圓盤(pán)(Wafer),還有卷帶料盤(pán)(Reel)。對(duì)應(yīng)的供料

2023-09-21 15:31:54 216

216

相對(duì)于其他的IC元件,如BGA和CSP等,倒裝晶片裝配工藝有其特殊性,該工藝引入了助焊劑工藝和底部填充工 藝。因?yàn)橹竸埩粑铮▽?duì)可靠性的影響)及橋連的危險(xiǎn),將倒裝芯片貼裝于錫膏上不是一種可采用的裝配方法 。

2023-09-22 15:13:10 352

352

倒裝晶片(Flip Chip)貼裝屬于先進(jìn)半導(dǎo)體組裝(Advanced Semiconductor Assembly),常見(jiàn)的應(yīng)用有無(wú)線天線、藍(lán)牙、硬盤(pán)磁頭、元件封裝、智能傳感器和一些醫(yī)用高精密設(shè)備等。

2023-09-26 15:47:45 335

335

簡(jiǎn)單介紹倒裝芯片封裝工藝過(guò)程中選擇錫膏的基本知識(shí)

2023-09-27 08:59:00 320

320

Flip chip又稱倒裝片,是在I/O pad上沉積錫鉛球,然后將芯片翻轉(zhuǎn)佳熱利用熔融的錫鉛球與陶瓷機(jī)板相結(jié)合此技術(shù)替換常規(guī)打線接合,逐漸成為未來(lái)的封裝主流,當(dāng)前主要應(yīng)用于高時(shí)脈的CPU、GPU(GraphicProcessor Unit)及Chipset 等產(chǎn)品為主。

2023-10-08 15:01:37 232

232 了晶圓級(jí)封裝(WLP)技術(shù)的發(fā)展。接下來(lái)討論了使用晶圓級(jí)封裝器件的實(shí)際方面。討論的主題包括:確定給定器件的倒裝芯片/UCSP封裝的可用性;通過(guò)其標(biāo)記識(shí)別倒裝芯片/UCSP;圓片級(jí)封裝件的可靠性;尋找適用的可靠性信息。

2023-10-16 15:02:47 420

420 電阻器是電子電路中常見(jiàn)的被動(dòng)元件,用于限制電流、調(diào)整電壓和執(zhí)行其他電阻性功能。在電阻器的制造中,有兩種常見(jiàn)的類型:厚膜晶片電阻和薄膜晶片電阻。這兩種類型的電阻器在結(jié)構(gòu)、性能和應(yīng)用方面都有一些顯著的區(qū)別。本文將介紹厚膜晶片電阻和薄膜晶片電阻的區(qū)別,以幫助讀者更好地理解它們的特性和用途。

2023-10-23 09:00:17 840

840

介紹倒裝芯片封裝選擇什么樣的錫膏?

2023-10-31 13:16:13 308

308

?詳細(xì)介紹了FC技術(shù),bumping技術(shù),underfill技術(shù)和substrate技術(shù),以及倒裝封裝芯片的熱設(shè)計(jì),機(jī)械應(yīng)力等可靠性設(shè)計(jì)。

2023-11-01 15:25:51 3

3 半導(dǎo)體技術(shù)的進(jìn)步大大提高了芯片晶體管數(shù)量和功能, 這一集成規(guī)模在幾年前是無(wú)法想象的。

2023-12-11 18:15:23 486

486

歡迎了解 1 引言 半導(dǎo)體技術(shù)的進(jìn)步大大提高了芯片晶體管數(shù)量和功能, 這一集成規(guī)模在幾年前是無(wú)法想象的。因此, 如果沒(méi)有 IC 封裝技術(shù)快速的發(fā)展, 不可能實(shí)現(xiàn)便攜式電子產(chǎn)品的設(shè)計(jì)。在消費(fèi)類

2023-12-14 17:03:21 201

201

共讀好書(shū) 敖國(guó)軍 張國(guó)華 蔣長(zhǎng)順 張嘉欣 (無(wú)錫中微高科電子有限公司) 摘要: 倒裝焊是今后高集成度半導(dǎo)體的主要發(fā)展方向之一。倒裝焊器件封裝結(jié)構(gòu)主要由外殼、芯片、引腳(焊球、焊柱、針)、蓋板(氣密性

2024-02-21 16:48:10 132

132

倒裝芯片技術(shù),也被稱為FC封裝技術(shù),是一種先進(jìn)的集成電路封裝技術(shù)。在傳統(tǒng)封裝技術(shù)中,芯片被封裝在底部,并通過(guò)金線連接到封裝基板上。而倒裝芯片技術(shù)則將芯片直接翻轉(zhuǎn)并安裝在封裝基板上,然后使用微小的焊點(diǎn)

2024-02-19 12:29:08 480

480

Flip Chip封裝工藝,也稱為芯片倒裝封裝技術(shù),是一種將集成電路芯片倒裝在載板或基板上的封裝方式。Flip Chip的英文名稱直譯為“翻轉(zhuǎn)芯片”,其思想源自于50年代的熱電偶焊接技術(shù),而真正

2024-02-20 14:48:01 241

241 不斷增加封裝中的輸入/輸出(I/O)數(shù)量,封裝解決方案正從傳統(tǒng)的線鍵封裝向倒裝芯片互連遷移,以滿足這些要求。對(duì)于具有多種功能和異構(gòu)移動(dòng)應(yīng)用的復(fù)雜和高度集成的系統(tǒng)而言,倒裝芯片封裝(FCCSP)被認(rèn)為一種有效的解決方案。

2024-03-04 10:06:21 176

176

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論