摘要:一種利用Verilog HDL設(shè)計(jì)CAM的方案,該方案以移位寄存器為核心,所實(shí)現(xiàn)的CAN具有可重新配置改變字長(zhǎng)、易于擴(kuò)展、匹配查找速度等特點(diǎn),并在網(wǎng)絡(luò)協(xié)處理器仿真中得到了應(yīng)用。

CAM(Content Addressable Memory,內(nèi)容可尋址存儲(chǔ)器)是一種特殊的存儲(chǔ)陣列。它通過(guò)將輸入數(shù)據(jù)與CAM中存儲(chǔ)的所有數(shù)據(jù)項(xiàng)同時(shí)進(jìn)行比較,迅速判斷出輸入數(shù)據(jù)是否與CAM中的存儲(chǔ)數(shù)據(jù)項(xiàng)相匹配,并給出匹配數(shù)據(jù)項(xiàng)的對(duì)應(yīng)地址和匹配信息。CAM以其高速查找、大容量等特點(diǎn)而被廣泛地應(yīng)用于電訊、網(wǎng)絡(luò)等領(lǐng)域。

本文介紹一種用Verilog HDL設(shè)計(jì)CAM的方案。該方案以移位寄存器為核心,具有可重新置改變字長(zhǎng)、易于擴(kuò)展、匹配查找速度快等特點(diǎn)。

1 CAM功能描述

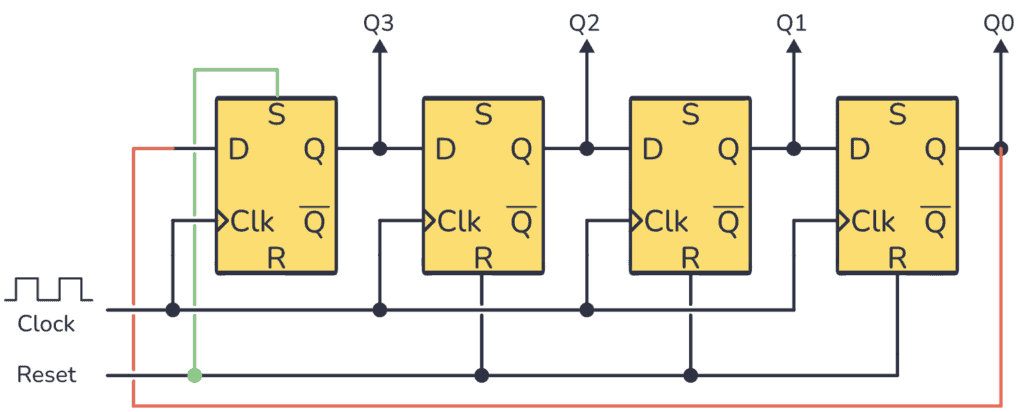

CAM的基本框圖如圖1所示。

與RAM相似,CAM是將數(shù)據(jù)項(xiàng)存儲(chǔ)在一個(gè)陣列中。每個(gè)數(shù)據(jù)項(xiàng)的位數(shù)叫做字寬,CAM中所有數(shù)據(jù)項(xiàng)的條數(shù)叫做CAM的深度。通過(guò)字寬和深度可以表征CAM中容量。

在寫(xiě)CAM模式(配置)時(shí),WRITE_E信號(hào)有效,MATCH_E信號(hào)無(wú)效,此時(shí)通過(guò)地址線ADDR選擇DATA_IN輸入的數(shù)據(jù)將要被寫(xiě)放哪一個(gè)單元;在讀CAM模式(查找匹配)時(shí),WRITE_E信號(hào)無(wú)效,MATCH_E信號(hào)有效,CAM將不使用地址線,而是直接將DATA_IN讀入的數(shù)據(jù)與CAM中存儲(chǔ)的各條數(shù)據(jù)項(xiàng)進(jìn)行并行比較。如果CAM中含有與此時(shí)輸入數(shù)據(jù)相匹配的存儲(chǔ)數(shù)據(jù)項(xiàng),CAM將從MATCH_ADDR輸出此存儲(chǔ)數(shù)據(jù)項(xiàng)的地址,并且通過(guò)MATH_OK輸出匹配成功的信息。在查找匹配模式時(shí),由于CAM是將輸入數(shù)據(jù)與存儲(chǔ)數(shù)據(jù)項(xiàng)并行比較,所以速度極快。同時(shí),由于不需要通過(guò)地址線來(lái)尋址數(shù)據(jù)項(xiàng),CAM將不受地址線寬度的限制,容易擴(kuò)展。

2 基于移位寄存器的CAM的設(shè)計(jì)

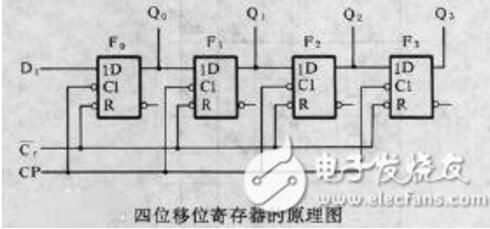

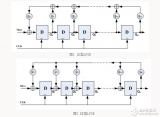

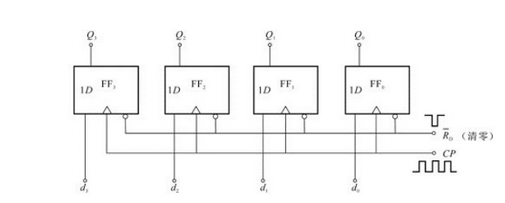

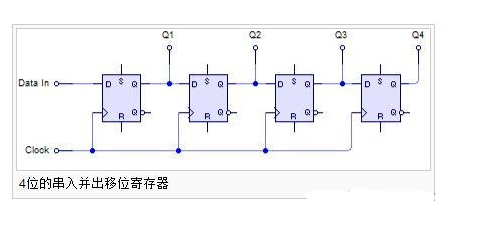

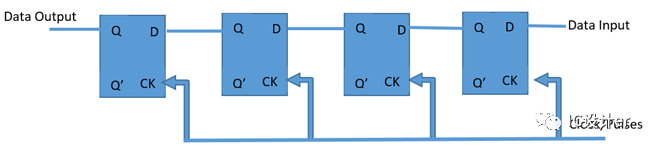

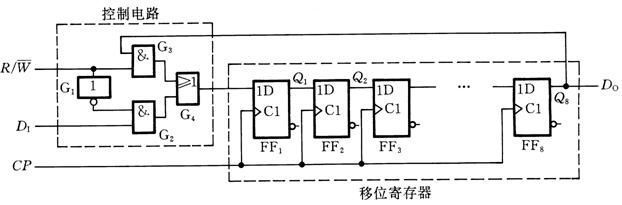

為了說(shuō)明設(shè)計(jì)方案,以一個(gè)寬度為4位、深度為1的基本CAM存儲(chǔ)單元為例。利用這樣一個(gè)基本存儲(chǔ)單元,通過(guò)適當(dāng)級(jí)聯(lián),可以構(gòu)成任意字寬和深度的CAM。該基本單元采用一個(gè)16位的移位寄存器、一個(gè)4位的比較器,外加16位的計(jì)數(shù)器和一個(gè)"二選一"的選擇器構(gòu)成。如圖2所示。

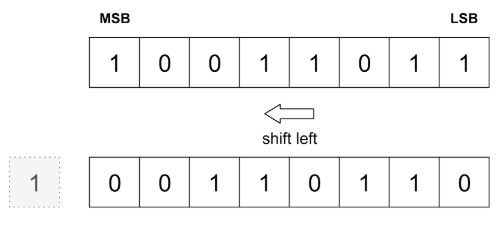

在寫(xiě)CAM模式時(shí),WRITE_E信號(hào)有效,DATA_IN輸入的是將要寫(xiě)入數(shù)據(jù)存儲(chǔ)項(xiàng)的4位數(shù)據(jù)。計(jì)數(shù)器進(jìn)行從"1111"到"0000"的減計(jì)數(shù),并將計(jì)數(shù)輸出值與DATA_IN輸入值進(jìn)行比較。若二者相同,比較器輸出"1"到移位寄存器中;不同則輸出"0"到移位寄存器中。在16個(gè)時(shí)鐘周期之后,將完成DATA_IN輸入數(shù)據(jù)與計(jì)數(shù)器輸出的所有情況的比較。這樣,移位寄存器中將存入15個(gè)"0"和一個(gè)"1"。

在讀CAM模式時(shí),MATCH_IN為"1",此時(shí),DATA_IN輸入的數(shù)據(jù)直接送到移位寄存器的地址端,它將決定移位寄存器輸出其16個(gè)位中的哪一位。如果該位輸出"1",則表示此時(shí)DATA_IN與原來(lái)寫(xiě)入該單元的數(shù)據(jù)相同,即發(fā)生匹配;反之則輸出"0",表示無(wú)匹配項(xiàng)。

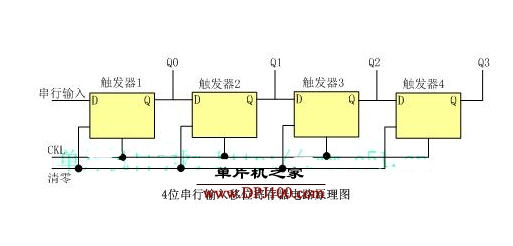

以上討論只是針對(duì)4位字寬的數(shù)據(jù)項(xiàng)的讀寫(xiě),而對(duì)于更長(zhǎng)字寬的數(shù)據(jù)項(xiàng),必須進(jìn)行字寬擴(kuò)展。可用多個(gè)比較器和移位寄存器組成的存儲(chǔ)數(shù)據(jù)項(xiàng)并聯(lián)在一起,組成一個(gè)字結(jié)構(gòu),即把輸入的數(shù)據(jù)按每4位分為一組,每組對(duì)應(yīng)一套比較器和移位寄存器,每組只產(chǎn)生一個(gè)最終的MTACH_OUT信號(hào)。例如,對(duì)于16位的數(shù)據(jù)項(xiàng),就需要4組這樣的結(jié)構(gòu)。這4組基本結(jié)構(gòu)中的讀和寫(xiě)可以同時(shí)完成。只有4組都產(chǎn)生匹配信號(hào),最終的MATCH_OUT輸出才有"1",表明讀入的16位DATA_IN數(shù)據(jù)與存儲(chǔ)的數(shù)據(jù)項(xiàng)匹配。

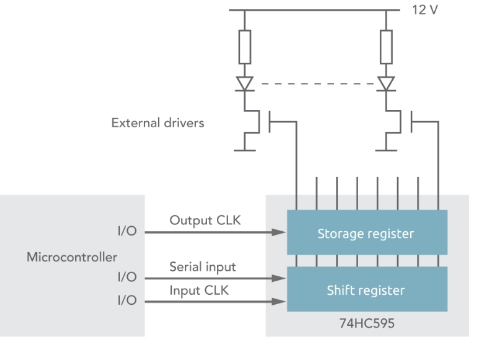

CAM只需要存儲(chǔ)多個(gè)數(shù)據(jù)項(xiàng),因此需要多個(gè)字結(jié)構(gòu)的深度擴(kuò)展。將這些字結(jié)構(gòu)中的比較器和移位寄存器分別組合在一起,構(gòu)成比較器陣列和移位寄存器陣列。為了在寫(xiě)CAM時(shí)進(jìn)行寫(xiě)入數(shù)據(jù)的定位,還需要一個(gè)地址譯碼模塊來(lái)指出是對(duì)哪一個(gè)數(shù)據(jù)項(xiàng)進(jìn)行寫(xiě)操作。在讀CAM時(shí),得到輸入數(shù)據(jù)與各個(gè)存儲(chǔ)數(shù)據(jù)項(xiàng)的匹配信息之后,還要對(duì)這些匹配信息進(jìn)行編碼,得到最后要輸出的相匹配的存儲(chǔ)數(shù)據(jù)項(xiàng)的地址MATCH_ADDR和是否發(fā)生匹配的信息MATCH_OK。

完整的CAM結(jié)構(gòu)框圖見(jiàn)圖3。

3 基于移位寄存器的CAM的Verilog HDL實(shí)現(xiàn)

硬件描述語(yǔ)言VerilogHDL是一種應(yīng)用于電路設(shè)計(jì)的描述語(yǔ)言,具有行為級(jí)、寄存器傳輸級(jí)、邏輯門(mén)級(jí)和開(kāi)關(guān)級(jí)等多層次描述。它簡(jiǎn)單易讀,描述與工藝無(wú)關(guān),并且得到許多EDA工具的支持。利用Verilog HDL語(yǔ)言進(jìn)行電路設(shè)計(jì)可以大大節(jié)省設(shè)計(jì)時(shí)間和成本。

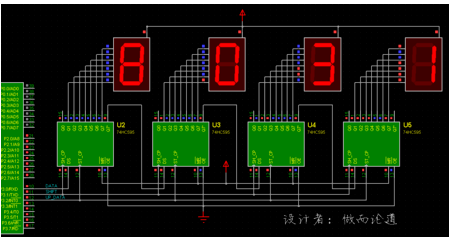

本設(shè)計(jì)以一個(gè)數(shù)據(jù)項(xiàng)字寬為16位、深度為8的CAM為例,進(jìn)行Verilog HDL設(shè)計(jì),并利用Xilinx Virtex系列中XCV1000器件進(jìn)行綜合。綜合后的仿真分析表明,該方案是合理可行的。

圖4為匹配查找的時(shí)序仿真結(jié)果,CAM中預(yù)先放入了0019H,001AH,…,001DH五個(gè)數(shù)據(jù)。CLK為系統(tǒng)時(shí)鐘,DATA_IN為數(shù)據(jù)輸入,MATCH_ENABLE為讀CAM(查找)允許信號(hào),GLOBAL_RST為全局清零信號(hào),R_MATCH_ADDR為匹配地址輸出信號(hào),R_MATCH_OK為是否發(fā)生匹配信號(hào)。從仿真波形可以看出,輸入數(shù)據(jù)經(jīng)過(guò)兩個(gè)時(shí)鐘周期,輸出匹配信息,包括是否匹配和相匹配的存儲(chǔ)數(shù)據(jù)項(xiàng)的地址。如果不匹配,是否匹配的信號(hào)為0,而輸出地址線不變。

本方案以移位寄存器設(shè)計(jì)CAM,在寫(xiě)模式下需要16個(gè)時(shí)鐘周期完成一個(gè)數(shù)據(jù)項(xiàng)的寫(xiě)入;讀模式僅需一個(gè)時(shí)鐘周期。它具有速度快、易于重新配置、易于擴(kuò)展等特點(diǎn)。本方案中的CAM利用Xilinx Virtex系列器件實(shí)現(xiàn),時(shí)鐘最高頻率可達(dá)80MHz以上。以本方案為基礎(chǔ),擴(kuò)展到32位、36位的實(shí)用化CAM已運(yùn)用于網(wǎng)絡(luò)協(xié)處理器的仿真測(cè)試中,并取得了較好的效果。

- DL實(shí)現(xiàn)(4803)

相關(guān)推薦

一文解析Matlab如何實(shí)現(xiàn)移位寄存器

15788

15788

verilog設(shè)計(jì)移位寄存器(4級(jí)串行什么意思?)

寄存器電路及應(yīng)用

移位寄存器原理

移位寄存器及其應(yīng)用 精選資料分享

移位寄存器的工作原理是什么?具有哪些功能應(yīng)用?

移位寄存器的特點(diǎn)和工作原理

移位寄存器的問(wèn)題

移位寄存器賦不同的初值

移位寄存器:串行輸入,串行輸出

FPGA的移位寄存器

LabVIEW移位寄存器怎么清空??

LabVIEW的移位寄存器

Matlab移位寄存器的實(shí)現(xiàn)

for循環(huán)中移位寄存器&索引隧道

串行輸入,串行輸出的移位寄存器

如何用Verilog HDL設(shè)計(jì)CAM?

怎樣去設(shè)計(jì)一種自動(dòng)加載移位寄存器?

求大蝦指導(dǎo)如何使用移位寄存器

四位雙向移位寄存器實(shí)驗(yàn)

0

0集成移位寄存器

19

19基于流密碼的可適配反饋移位寄存器指令

17

17移位寄存器及其應(yīng)用

72

72寄存器與移位寄存器

59

59第二十六講 寄存器和移位寄存器

8922

8922

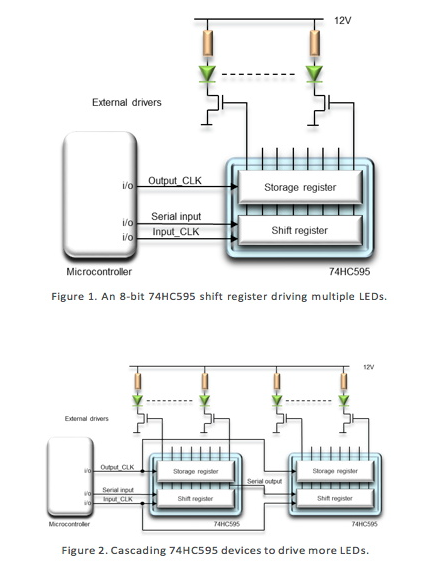

增強(qiáng)型并行端口EPP擴(kuò)展移位寄存器輸出接口的方法

1215

1215

一種基于移位寄存器的CAM的Verilog HDL實(shí)現(xiàn)

1307

1307

線性移位寄存器

1740

1740

移位寄存器的工作原理是什么?

1625

1625移位寄存器的工作原理是什么?

44087

44087基于FPGA的可變長(zhǎng)度移位寄存器優(yōu)化設(shè)計(jì)

4985

4985

8位移位寄存器行選電路圖

6191

6191

移位寄存器及其應(yīng)用實(shí)驗(yàn)

22

2274HC595D_3態(tài)8位移位寄存器

14

14賽靈思FPGA的SRL16移位寄存器原理與使用

6869

6869

移位寄存器工作原理_4位移位寄存器工作原理_4位雙向移位寄存器74LS194邏輯電路和圖形符號(hào)

162375

162375線性反饋移位寄存器原理與實(shí)現(xiàn)

46605

46605

基于matlab的移位寄存器法m序列的產(chǎn)生

8560

8560

移位寄存器實(shí)驗(yàn)報(bào)告_移位寄存器原理

27206

27206

移位寄存器具有什么特點(diǎn)及作用?

82198

82198

移位寄存器的特點(diǎn)_移位寄存器工作原理

46140

46140

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

19126

19126移位寄存器74ls194應(yīng)用電路圖大全(雙向移位寄存器/74HC93/環(huán)形計(jì)數(shù)器)

79692

79692

分享SNx4HC164八位移位寄存器引腳配置和功能

6033

6033

移位寄存器的原理

71381

71381

移位寄存器的種類(lèi)與作用

14506

14506

移位寄存器串入并出與并入串出

30504

30504

移位寄存器的工作原理

41305

41305

74HC595和74HCT595移位寄存器的數(shù)據(jù)手冊(cè)免費(fèi)下載

20

20labview移位寄存器的用法及作用

50448

50448移位寄存器在LED應(yīng)用設(shè)計(jì)中的特點(diǎn)分析

5890

5890

擴(kuò)展 IO 口:移位寄存器 74HC595(含電路和程序)

22

22線性反饋移位寄存器原理

2789

2789Xilinx SRL16E如何實(shí)現(xiàn)16移位寄存器

916

916移位寄存器的設(shè)計(jì)與實(shí)現(xiàn)

2983

2983在線學(xué)習(xí)SystemVerilog:移位寄存器

1446

1446使用庫(kù)來(lái)管理和控制級(jí)聯(lián)中的移位寄存器

0

0在LED設(shè)計(jì)中使用Nexperia移位寄存器以減小尺寸和BOM

617

617

AiP74HC/HCT595輸出移位寄存器手冊(cè)

0

0什么是移位寄存器?移位寄存器的用途是什么?

4416

4416

使用移位寄存器構(gòu)建一個(gè)環(huán)形計(jì)數(shù)器電路

757

757

移位寄存器連接方法及類(lèi)型

1548

1548使用移位寄存器構(gòu)建環(huán)形計(jì)數(shù)器電路

2147

2147什么是移位寄存器?數(shù)字電路中的寄存器類(lèi)型有哪些呢?

2473

2473

labview移位寄存器如何清零

438

438移位寄存器的工作原理 移位寄存器左移和右移怎么算

639

639移位寄存器可降低LED設(shè)計(jì)的尺寸和成本

88

88

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論