來源:《Verilog數(shù)字系統(tǒng)設(shè)計(jì)(夏宇聞)》 阻塞和非阻塞賦值的語言結(jié)構(gòu)是Verilog 語言中最難理解概念之一。甚至有些很有經(jīng)驗(yàn)的Verilog 設(shè)計(jì)工程師也不能完全正確地理解:何時(shí)使用非阻塞

2021-08-17 16:18:17 6000

6000 本帖最后由 huangshun2016 于 2017-4-14 13:57 編輯

Verilog HDL 華為入門教程

2015-08-21 17:19:22

本帖最后由 lee_st 于 2017-10-31 08:47 編輯

Verilog HDL 華為入門教程

2017-10-21 20:50:36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.3 三種建模方式

2017-12-08 14:39:50

本帖最后由 IC那些事兒 于 2020-11-30 19:05 編輯

Verilog HDL是一種硬件描述語言,用于從算法級(jí)、門級(jí)到開關(guān)級(jí)的多種抽象設(shè)計(jì)層次的數(shù)字系統(tǒng)建模。被建模的數(shù)字系統(tǒng)對(duì)象

2020-11-30 19:03:38

Verilog HDL語言有什么優(yōu)越性Verilog HDL語言在FPGA/CPLD開發(fā)中的應(yīng)用

2021-04-23 07:02:03

嵌入式開發(fā)Verilog教程(二)——Verilog HDL設(shè)計(jì)方法概述前言一、Verilog HDL語言簡(jiǎn)介1.1 Verilog HDL語言是什么1.2前言在數(shù)字邏輯設(shè)計(jì)領(lǐng)域,迫切需要一種共同

2021-11-08 09:30:31

是時(shí)序邏輯原語。 ? 開關(guān)級(jí)基本結(jié)構(gòu)模型,例如p m o s 和n m o s等也被內(nèi)置在語言中。 ? 提供顯式語言結(jié)構(gòu)指定設(shè)計(jì)中的端口到端口的時(shí)延及路徑時(shí)延和設(shè)計(jì)的時(shí)序檢查。 ? 可采用三種不同方式或

2018-07-03 05:19:30

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述

2019-09-06 09:14:16

本文中凡提到計(jì)算這個(gè)詞處,指的就是上面一段中Computing所包含的意思。由傳統(tǒng)的觀點(diǎn)出發(fā),我們可以從三個(gè)不同的方面來研究計(jì)算,即從數(shù)學(xué)、科學(xué)和工程的不同角度。 由比較現(xiàn)代的觀點(diǎn)出發(fā),我們可以從

2018-12-10 15:31:15

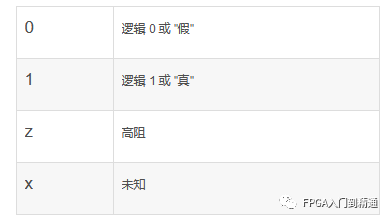

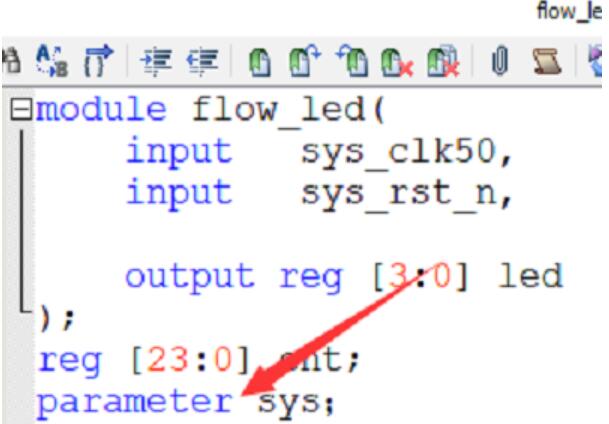

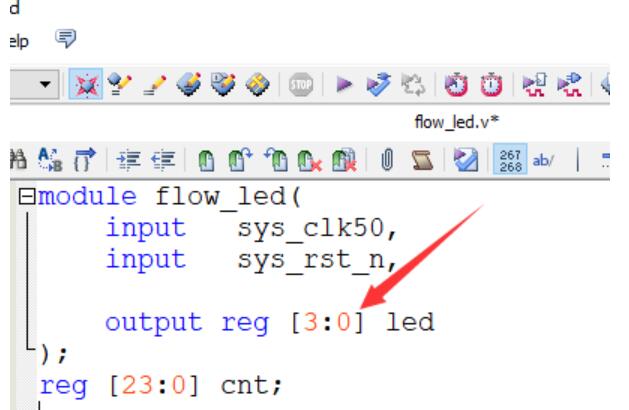

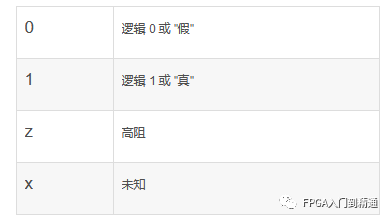

Verilog 變量聲明與數(shù)據(jù)類型一Verilog語法中最基本的數(shù)據(jù)類型有 線網(wǎng)(wire),寄存器(reg)和整數(shù)(integer)三種類型,這三種數(shù)據(jù)類型是可綜合的數(shù)據(jù)類型,在Verilog

2021-08-10 14:01:06

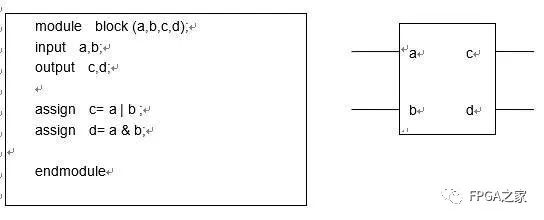

,我們專門安排一節(jié)內(nèi)容討論。見 FPGA中雙向端口的使用 。可見:Verilog module給我們引入了另一種數(shù)字電路的設(shè)計(jì)方法。

2021-07-23 23:08:49

結(jié)構(gòu)化描述形式82.6混合設(shè)計(jì)描述方式92.7設(shè)計(jì)模擬10第3章Verilog語言要素143.1標(biāo)識(shí)符143.2注釋143.3格式143.4系統(tǒng)任務(wù)和函數(shù)153.5編譯指令153.5.1`define

2012-06-21 20:27:11

本帖最后由 lee_st 于 2017-10-31 08:45 編輯

Verilog語言入門

2017-10-21 20:57:28

在Verilog語言中向量表示為【high#:low#】,方括號(hào)中左邊的數(shù)總是代表向量的最高有效位。請(qǐng)問,最高有效位有什么作用呢???

2013-07-18 21:43:12

在看FPGA的資料,有一個(gè)關(guān)于Verilog語言的問題突然想不明白~{:16:}關(guān)于時(shí)序的,Verilog中,判斷if成立的條件是當(dāng)前值(感覺是電平式),還是過去值(感覺是時(shí)序)?例如:if(a==2) out

2013-03-25 21:31:58

求,verilog語言1,4,15 位二進(jìn)制加減法器設(shè)計(jì)的代碼急用,謝謝:)

2011-04-03 21:52:44

generate語句有generate_for、generate_if、generate_case三種語句。2. generate for語句必須有g(shù)envar關(guān)鍵字定義for的變量3. for 的內(nèi)容必須

2020-12-23 16:59:15

級(jí)的夠了,好吧,牛逼的板子都太貴了,***一枚。下面開始說手

verilog學(xué)習(xí)過程。首先是

語言學(xué)習(xí)嘍,

verilog和c

語言很像,眾所周知,

入門容易,但是,不要小瞧

語言的學(xué)習(xí),一定要踏踏實(shí)實(shí),因?yàn)?/div>

2015-02-05 17:29:41

verilog除了input和output的端口類型,還有inout雙向端口,比如在IIC協(xié)議中sda為雙向信號(hào)。若sda在sda_out_en為1時(shí)輸出sda_out的數(shù)值,在sda_out_en為0時(shí)sda為輸入狀態(tài),如何使用三目運(yùn)算符實(shí)現(xiàn)此功能

2023-08-03 16:24:02

Verilog HDL 的特點(diǎn)Verilog HDL 語言不僅定義了語法,而且對(duì)每個(gè)語法結(jié)構(gòu)都定義了清晰的模擬、仿真語義。使用這種語言編寫的模型可以方便地使用 Verilog 仿真器進(jìn)行驗(yàn)證

2018-09-18 09:33:31

設(shè)計(jì)③ 如何給端口選擇正確的數(shù)據(jù)類型④ Verilog語言中l(wèi)atch的產(chǎn)生⑤ 組合邏輯反饋環(huán)⑥ 阻塞賦值與非阻塞賦值的不同⑦ FPGA的靈魂?duì)顟B(tài)機(jī)⑧ 代碼風(fēng)格的重要性[hide][/hide]

2016-08-17 05:56:55

常用的FBAR模型有哪三種?

2021-03-11 06:16:18

[tr=transparent]當(dāng)前最流行的硬件設(shè)計(jì)語言有兩種,即 VHDL 與 Verilog HDL,兩者各有優(yōu)劣,也各有相當(dāng)多的擁護(hù)者。VHDL 語言由美國(guó)軍方所推出,最早通過國(guó)際電機(jī)工程

2018-06-07 18:11:03

Verilog HDL與VHDL是當(dāng)前最流行的兩種硬件設(shè)計(jì)語言,兩者各有優(yōu)劣,也各有相當(dāng)多的擁護(hù)者,都通過了IEEE 標(biāo)準(zhǔn)。VHDL在北美及歐洲應(yīng)用很普遍,Verilog HDL 語言在中國(guó)、日本

2021-07-26 06:39:56

編譯的三種類型是什么?ARM_Linux制作嵌入式遠(yuǎn)程調(diào)試工具

2021-12-24 06:42:58

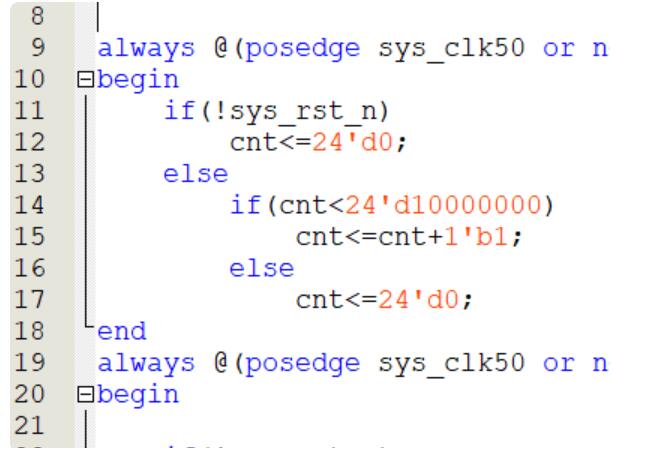

是在描述硬件,即用代碼畫圖。在 Verilog 語言中,always 塊是一種常用的功能模塊,也是結(jié)構(gòu)最復(fù)雜的部分。筆者初學(xué)時(shí)經(jīng)常為 always 語句的編寫而苦惱.

2021-07-29 07:42:25

VHDL語言和verilog語言有何區(qū)別

2019-03-28 06:52:52

VHDL語言和verilog語言有何區(qū)別

2019-03-29 07:55:09

進(jìn)程類型進(jìn)程的三種狀態(tài)

2021-04-02 07:06:39

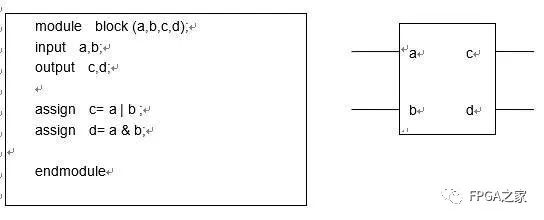

0,再接端口名;關(guān)于內(nèi)部信號(hào)說明要用到和端口有關(guān)的wire和reg類型變量的聲明。模板和上面類似,關(guān)于reg和wire變量后面再說。關(guān)于功能定義是模塊中最重要的部分,有三種方法可在模塊中產(chǎn)生邏輯(1

2015-04-07 17:44:42

X-HDL:軟件簡(jiǎn)介—SoftWare Description: X-HDL v3.2.55 VHDL/Verilog語言翻譯器

一款VHDL/Verilog語言翻譯器。可實(shí)現(xiàn)VHDL和Verilog語言的相互智能化轉(zhuǎn)化。這分別是windows、linux、solaris版本。

2006-03-25 12:00:47 355

355 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

69 Verilog HDL 華為入門教程

本文主要介紹了Verilog HDL 語言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語言的基本要素,能

2010-02-11 08:35:38 140

140 Verilog HDL入門教程(華為絕密資料)

本文主要介紹了Verilog HDL 語言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語言的

2010-04-02 11:52:21 0

0 摘 要:通過設(shè)計(jì)實(shí)例詳細(xì)介紹了用Verilog HDL語言開發(fā)FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優(yōu)越性。

2009-06-20 11:51:28 1857

1857

Verilog HDL程序基本結(jié)構(gòu)與程序入門

Verilog HDL程序基本結(jié)構(gòu)

Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的

2010-02-08 11:43:30 2185

2185 Verilog HDL語言簡(jiǎn)介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數(shù)

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL語言對(duì)比

Verilog HDL和VHDL都是用于邏輯設(shè)計(jì)的硬件描述語言,并且都已成為IEEE標(biāo)準(zhǔn)。VHDL是在1987年成為IEEE標(biāo)準(zhǔn),Verilog HDL

2010-02-09 09:01:17 10317

10317 Verilog 黃金參考指南是Verilog 硬件描述語言及其語法語義合并以及將它應(yīng)用到硬件設(shè)計(jì)的一個(gè)簡(jiǎn)明的快速參考指南 Verilog 黃金參考指南并不是要代替IEEE 的標(biāo)準(zhǔn)Verilog 語言參考手冊(cè)它不像

2011-12-26 15:03:06 0

0 本文簡(jiǎn)單討論并總結(jié)了VHDL、Verilog,System verilog 這三中語言的各自特點(diǎn)和區(qū)別 As the number of enhancements

2012-01-17 11:32:02 0

0 verilog硬件描述語言課程講義

2012-05-21 15:01:29 33

33 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數(shù)字邏輯電路設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結(jié)

2012-10-08 14:48:31 0

0 Verilog HDL程序設(shè)計(jì)與實(shí)踐著重介紹了Verilog HDL語言

2015-10-29 14:45:47 21

21 verilog語言經(jīng)典教材,本書講解了verilog的基本語法和經(jīng)典例子等等。

2015-11-10 11:44:20 23

23 Verilog硬件描述語言參考手冊(cè),Verilog語法內(nèi)容介紹

2015-11-12 17:20:37 0

0 基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)基于verilog語言的數(shù)字頻率計(jì)設(shè)計(jì)

2015-12-08 15:57:23 0

0 Verilog HDL硬件描述語言

有需要的下來看看

2015-12-29 15:31:27 0

0 很好的C語言入門教程,可以肯定的說這個(gè)教程只是為初學(xué)或入門者準(zhǔn)備的

2016-01-22 14:46:52 7

7 本章介紹Verilog HDL語言的發(fā)展歷史和它的主要能力。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 14

14 本章介紹Verilog HDL的基本要素,包括標(biāo)識(shí)符、注釋、數(shù)值、編譯程序指令、系統(tǒng)任務(wù)和系統(tǒng)函數(shù)。另外,本章還介紹了Verilog硬件描述語言中的兩種數(shù)據(jù)類型。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)。

2016-04-25 16:09:32 16

16 本章描述Verilog HDL中的第三種建模方式,即行為建模方式。為充分使用Verilog HDL,一個(gè)模型可以包含所有上述三種建模方式。verilog相關(guān)教程材料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-25 16:09:32 14

14 Verilog 入門的實(shí)例代碼,有需要的下來看看

2016-05-24 10:03:05 19

19 Verilog HDL 華為入門教程

2016-06-03 16:57:53 45

45 本文主要介紹了Verilog HDL 語言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL設(shè)計(jì)方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2016-07-15 15:27:00 0

0 51單片機(jī)c51語言入門教程,C語言入門教程

2016-08-29 15:02:03 30

30 VHDL語言編程學(xué)習(xí)Verilog硬件描述語言

2016-09-01 15:27:27 0

0 Verilog HDL設(shè)計(jì)(入門),感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 23

23 Verilog語言練習(xí)與講解2,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 1

1 Verilog語言練習(xí)與講解1,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 2

2 Verilog語言入門,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 15:29:36 5

5 本章介紹Verilog HDL的基本要素,包括標(biāo)識(shí)符、注釋、數(shù)值、編譯程序指令、系統(tǒng)任務(wù)和系統(tǒng)函數(shù)。另外,本章還介紹了Verilog硬件描述語言中的兩種數(shù)據(jù)類型。

3.1 標(biāo)識(shí)符

2017-02-11 17:01:07 1713

1713

基于FPGA Verilog-HDL語言的串口設(shè)計(jì)

2017-02-16 00:08:59 35

35 詳細(xì)介紹了verilog語言,很容易看懂,并配有示例

2017-05-03 09:09:57 0

0 關(guān)于Verilog語言的官方標(biāo)準(zhǔn)全稱是《IEEE Std 1364-2001:IEEE Standard Verilog? Hardware Description Language》。其中包括27章以及8個(gè)附錄,真正對(duì)于電路設(shè)計(jì)有用的內(nèi)容大約1/3的樣子。

2018-07-06 09:59:00 4748

4748

本文首先介紹了verilog的概念和發(fā)展歷史,其次介紹了verilog的特征與Verilog的邏輯門級(jí)描述,最后介紹了Verilog晶體管級(jí)描述與verilog的用途。

2018-05-14 14:22:44 43436

43436

本文檔的主要內(nèi)容詳細(xì)介紹的是Verilog HDL入門教程之Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程。

2018-09-20 15:51:26 80

80 本文主要介紹了Verilog HDL 語言的一些基本知識(shí),目的是使初學(xué)者能夠迅速掌握HDL 設(shè)計(jì)方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡(jiǎn)單的設(shè)計(jì)代碼并能夠進(jìn)行一些簡(jiǎn)單設(shè)計(jì)的Verilog HDL建模。

2019-02-11 08:00:00 95

95 Verilog HDL作為現(xiàn)在最流行的FPGA開發(fā)語言,當(dāng)然是入門基礎(chǔ)。

2019-02-18 14:47:00 10320

10320 Verilog HDL是一種用于數(shù)字系統(tǒng)設(shè)計(jì)的語言。用Verilog HDL描述的電路設(shè)計(jì)就是該電路的Verilog HDL模型也稱為模塊。Verilog HDL既是一種行為描述的語言也是一種結(jié)構(gòu)描述的語言。

2019-03-08 14:29:12 12094

12094 即使Verilog成功,許多經(jīng)驗(yàn)豐富的Verilog用戶仍然認(rèn)為其編程語言界面( PLI)作為“軟件任務(wù)”。一步一步的方法可以幫助您在編寫PLI函數(shù)時(shí)“打破僵局”。通過學(xué)習(xí)PLI設(shè)計(jì)的基本知識(shí)而不會(huì)被太多細(xì)節(jié)困擾,您將獲得可以立即使用的PLI基礎(chǔ)知識(shí)。

2019-08-13 17:31:43 5443

5443 Verilog HDL簡(jiǎn)稱Verilog,它是使用最廣泛的硬件描述語言。

2020-03-22 17:29:00 4356

4356 的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標(biāo)準(zhǔn)。Verilog HDL具有C語言基礎(chǔ)就很容易上手,而VHDL語言則需要Ada編程基礎(chǔ)。另外Verilog

2020-09-01 11:47:09 4002

4002

簡(jiǎn)單介紹Verilog HDL語言和仿真工具。

2021-05-06 16:17:10 617

617 基于Linux的C語言編程入門教程

2021-06-15 10:56:44 18

18 Verilog入門教程,介紹Verilog的語法知識(shí),基本程序編寫。

2021-08-13 10:56:40 2

2 知乎上刷到一個(gè)問題,問性能最強(qiáng)的編程語言是什么?看到高贊回答到是Verilog,然后在評(píng)論區(qū)就引發(fā)了一場(chǎng)Verilog到底算不算編程語言的爭(zhēng)論,我覺得比較有意思,所以就也打算嘮嘮這個(gè)事情。 趁著最近

2021-08-23 14:30:49 5558

5558 Verilog HDL入門教程.pdf

2021-11-02 16:27:14 108

108 Verilog HDL與VHDL是當(dāng)前最流行的兩種硬件設(shè)計(jì)語言,兩者各有優(yōu)劣,也各有相當(dāng)多的擁護(hù)者,都通過了IEEE 標(biāo)準(zhǔn)。VHDL在北美及歐洲應(yīng)用很普遍,Verilog HDL 語言在中國(guó)、日本

2021-11-06 09:05:57 15

15 Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 159

159 要想深入理解Verilog就必須正視Verilog語言同時(shí)具備硬件特性和軟件特性。

2022-07-07 09:54:48 1124

1124 Verilog HDL 入門教程

2022-08-08 14:36:22 5

5 本文將討論 verilog 中常用的數(shù)據(jù)類型,包括對(duì)數(shù)據(jù)表示、線網(wǎng)類型、變量類型和數(shù)組,分享一下使用方法和注意事項(xiàng)。

2023-05-12 17:43:13 3845

3845

描述的語言。這也就是說,無論描述電路功能行為的模塊或描述元器件或較大部件互連的模塊都可以用Verilog語言來建立電路模型。如果按照一定的規(guī)矩編寫,功能行為模塊可以通過工具自動(dòng)地轉(zhuǎn)換為門級(jí)互連模塊。Verilog模型可以是實(shí)際電路的不同級(jí)別的抽象。這些抽象的級(jí)別和它們對(duì)應(yīng)的模型類型共有以下五種

2023-05-22 15:52:42 557

557

描述的語言。這也就是說,無論描述電路功能行為的模塊或描述元器件或較大部件互連的模塊都可以用Verilog語言來建立電路模型。如果按照一定的規(guī)矩編寫,功能行為模塊可以通過工具自動(dòng)地轉(zhuǎn)換為門級(jí)互連模塊。Verilog模型可以是實(shí)際電路的不同級(jí)別的抽象。這些抽象的級(jí)別和它們對(duì)應(yīng)的模型類型共有以下五種

2023-05-22 15:53:23 531

531

要想深入理解Verilog就必須正視Verilog語言同時(shí)具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強(qiáng)調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級(jí)語法

2023-05-25 15:10:21 642

642

要想深入理解Verilog就必須正視Verilog語言同時(shí)具備硬件特性和軟件特性。在當(dāng)下的教學(xué)過程中,教師和教材都過于強(qiáng)調(diào)Verilog語言的硬件特性和可綜合特性。將Verilog語言的行為級(jí)語法

2023-05-25 15:10:44 576

576

Verilog大量例程(簡(jiǎn)單入門到提高)

2023-08-16 11:49:31 0

0 在Verilog硬件描述語言中,端口是指連接模塊(Module)與其他模塊、寄存器或是物理設(shè)備的輸入或輸出接口。單向端口可以作為輸入或輸出使用,而雙向端口具有雙重作用,既可以接收輸入信號(hào),又可以輸出

2024-02-23 10:18:54 156

156 Verilog是一種硬件描述語言(HDL),廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)和硬件驗(yàn)證。在Verilog中,模塊是構(gòu)建電路的基本單元,而模塊端口對(duì)應(yīng)方式則用于描述模塊之間信號(hào)傳遞的方式。本文將介紹

2024-02-23 10:20:32 190

190 語言的接口機(jī)制,并深入探討其原理和應(yīng)用。 Verilog語言概述 Verilog是由美國(guó)專業(yè)電子設(shè)計(jì)自動(dòng)化公司Cadence設(shè)計(jì)系統(tǒng)有限公司(前身是Gateway Design Automation公司)開發(fā)的一種硬件描述語言。它是一種結(jié)構(gòu)化,靜態(tài)和類型安全的編程語言,具有強(qiáng)大的硬件描述能力。

2024-02-23 10:22:37 145

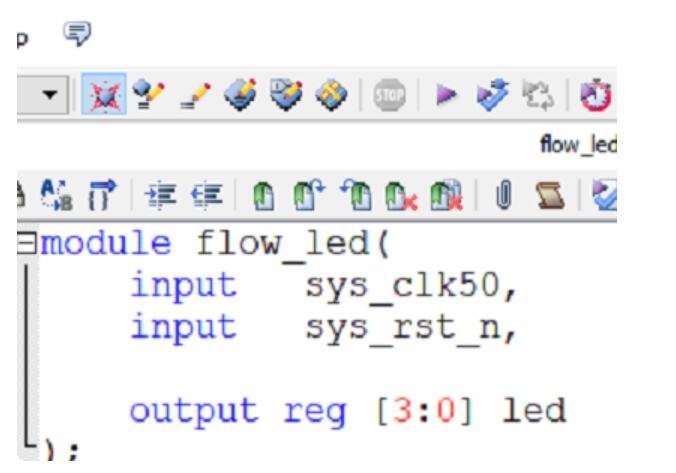

145 在 Verilog 中,端口類型有三種:輸入端口(input)、輸出端口(output)和雙向端口(inout)。 輸入端口(input)用于接收來自其他模塊的信號(hào)。在一個(gè)模塊中,輸入端口是被調(diào)用

2024-02-23 10:28:08 215

215

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論