創(chuàng)建真正的 3D 設(shè)計被證明比 2.5D 復(fù)雜和困難得多,需要在技術(shù)和工具方面進(jìn)行重大創(chuàng)新。

雖然已經(jīng)有很多關(guān)于 3D 設(shè)計的討論,但對于 3D 的含義有多種解釋。然而,這不僅僅是語義,因為每個封裝選項都需要不同的設(shè)計方法和技術(shù)。隨著芯片進(jìn)入真正的3D-IC領(lǐng)域,在邏輯之上堆疊邏輯或存儲器,它們的設(shè)計、制造以及最終的成品率和測試變得更具挑戰(zhàn)性。

“一開始,代工廠開始提供多芯片封裝,他們開始使用 3D-IC 這個術(shù)語,”Cadence 定制 IC 和 PCB 部門產(chǎn)品管理組總監(jiān) John Park說。“但它指的不僅僅是硅堆疊和中介層。它還包括高密度 RDL 扇出。這是一個術(shù)語,用于對許多芯片、主要是基于代工廠的封裝技術(shù)進(jìn)行分組。”

已經(jīng)有幾次嘗試來整理這個術(shù)語。“我們正在與 imec 保持一致,后者將 3D 分為四個部分,”EV Group 業(yè)務(wù)發(fā)展總監(jiān) Thomas Uhrmann 說。“真正的 3D 是晶圓以高度集成的方式堆疊在一起。第二組是 3D 片上系統(tǒng) (SoC) 集成,其中您可能有一個背面配電層,或一個晶圓到晶圓的存儲器堆棧。第三組包括 2.5D 和硅中介層。最后一個是 3D 系統(tǒng)級封裝 (SiP),其中接觸間距約為 700 微米,包括扇出晶圓級封裝。差異化很有趣,因為他們定義了觸點間距或集成密度的差異化。”

這提供了物理差異,但差異也可以從其他方面來看。“有趣的 3D 類型要么是邏輯對邏輯,要么是顯著的內(nèi)存對邏輯,” Synopsys研究員 Rob Aitken 說。“這兩個都是起點,但是你可以開始堆疊其他隨機(jī)的東西。我會說 HBM 是 3D 堆棧,但它們是非常具體的 3D 堆棧。”

這些封裝方法中的每一種的流程都是不同的。“多年來,2.5D 和 3D 一直被用于支持傳感器應(yīng)用之類的東西,”西門子 EDA 高級封裝解決方案總監(jiān) Tony Mastroianni說。“但他們不使用自動布局布線流程,這就是為什么我喜歡使用‘真正的 3D’這個詞。” 今天的堆疊芯片技術(shù)依賴于人們手動進(jìn)行規(guī)劃。您正在設(shè)計每個芯片,以便它們對接在一起,但工具并沒有這樣做。分區(qū)和詳細(xì)的引腳規(guī)劃是手動過程。”

真正的 3D 需要重新考慮整個流程。“為了將 SoC 有效地實現(xiàn)為 2.5D 系統(tǒng),例如避免良率問題或?qū)崿F(xiàn)具有更多晶體管的更大系統(tǒng),可以使用現(xiàn)有架構(gòu),” Fraunhofer IIS 工程高效電子部門負(fù)責(zé)人 Andy Heinig 說。“只需要實現(xiàn)一個芯片到芯片的接口。但只有使用新概念和架構(gòu),才能發(fā)揮真正 3D 集成的優(yōu)勢。”

為什么選擇 3D

3D的最大好處之一是縮短了距離。Synopsys 的 Aitken 說:“你可以證明存在二的平方根效應(yīng)。” “對于這個堆疊物體中的所有距離,它們變成了 2D 變體中的 0.7。結(jié)果,它們在布線部分消耗的功率現(xiàn)在是以前的 0.7 左右,因為電容減小了。”

影響可能比這更大。“信號傳輸過程中會產(chǎn)生大量熱量,”EV Group 的 Uhrmann 說。“對于 CMOS,你對某些東西進(jìn)行充電和放電以存儲然后傳遞信息。縮小和堆疊die將使您能夠使其更小,因此可以在三維空間中傳遞信息。但在 3D 中,它們之間可能只有一個緩沖區(qū),而不是大型 PHY 和通信協(xié)議。”

尺寸有兩個優(yōu)勢——良率和占地面積。“假設(shè)類似數(shù)量的邏輯分布在多個芯片上,較小對象的連V領(lǐng)將高于一個較大對象的良率,”Aitken 說。“因此,您可以降低一定程度的成本。當(dāng)然,你正在增加其他成本,但這些成本會隨著時間的推移而下降。”

從 2D 封裝的角度來看,堆疊芯片可以顯著減少面積。“通過堆疊,我可以在同一區(qū)域獲得三倍的邏輯數(shù)量,”西門子的 Mastroianni 說。“你最終會得到更小的足跡和更多的邏輯。所以你可以在那個區(qū)域安裝更多的馬力,如果你有區(qū)域限制,它可能會降低系統(tǒng)成本。”

異構(gòu)性可能是另一個好處。“3D 集成的異構(gòu)技術(shù)架構(gòu)已經(jīng)成熟,”Lightelligence 工程副總裁 Maurice Steinman 說。“考慮混合技術(shù)組件,例如光子 IC 及其配套電子 IC。對于其中一些集成,沒有其他方法可以在不犧牲大量功率或性能的情況下提供所需的數(shù)千個芯片到芯片互連。”

混合技術(shù)仍然主要是未知領(lǐng)域。“如果您的設(shè)計不適合reticle尺寸,那么為了能夠構(gòu)建更多的門,您需要使用真正的 3D,而這可能會保留在相同的技術(shù)中,”Mastroianni 說。“但在某些情況下,你可能想要混合搭配。也許你有一個你真正想要的前沿技術(shù)計算引擎,但其余的東西有很多控制,你可以在一個不那么激進(jìn)的制程節(jié)點上做。”

這變成了一個集成挑戰(zhàn)。Cadence 數(shù)字與簽核部產(chǎn)品管理組總監(jiān) Vinay Patwardhan 表示:“我們最近發(fā)現(xiàn),純邏輯內(nèi)存配置適用于某些類型的客戶,他們正試圖解決片上內(nèi)存墻問題。” “但是很多客戶希望在兩層都有邏輯。例如,即使頂層芯片上只有內(nèi)存,內(nèi)存 BiST 邏輯或與內(nèi)存一起使用的測試邏輯也需要位于該芯片上。頂層裸片需要一些邏輯。”

物理層次結(jié)構(gòu)

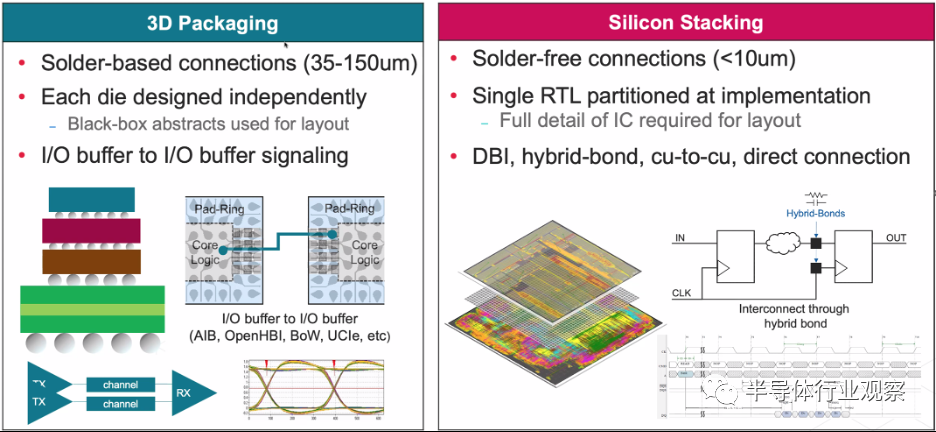

將芯片集成到 3D 堆棧中以及對該堆棧進(jìn)行封裝涉及多種技術(shù),如圖 1 所示。

物理尺寸很重要。“對于最終的 3D 集成,你談?wù)摰氖?14 納米間距,基本上就是今天的晶體管,”Uhrmann 說。“如果你談?wù)摰氖切⌒酒鼈兪枪δ苄?IP 塊,那么你就在微米間距的范圍內(nèi)。晶體管堆疊和小芯片集成之間存在接近一個數(shù)量級。當(dāng)您使用 3D 小芯片、高度集成的具有微米間距的裸片形成 3D 封裝時,您無法將微米間距連接到外部世界。你仍然需要擁有封裝技術(shù)才能使布線越來越粗,所以你最終會在板級上達(dá)到 400 多微米。”

間距(pitch)定義了集成過程。“當(dāng)我們封裝多個芯片或多個小芯片時,封裝存在一些很大的差異,”Cadence 的 Park 說。“小芯片通常使用所謂的基于焊料的連接。它們與微凸塊和 C4 連接,我們使用通常約 45 微米或更大的連接來連接它們。這也創(chuàng)建了一個封裝層次結(jié)構(gòu),因為我們經(jīng)常使用黑盒、每個芯片或小芯片的抽象表示,而封裝設(shè)計師負(fù)責(zé)將它們正確連接起來。”

這通常需要不同的工具。“這是一個多尺度問題,也意味著多物理問題,” Ansys產(chǎn)品營銷總監(jiān) Marc Swinnen 說。“當(dāng)你從芯片上的納米到封裝上的毫米再到 3D-IC 內(nèi)插器(interposer)上的厘米時,你跨越了六個數(shù)量級。傳統(tǒng)上,這些由三組不同的工具處理。現(xiàn)在對于 3D-IC,這些都需要整合成一個。”

團(tuán)隊分裂也會導(dǎo)致問題。“大多數(shù)公司都有 ASIC 設(shè)計的設(shè)計團(tuán)隊,以及獨立的內(nèi)部封裝設(shè)計團(tuán)隊,”Park 補(bǔ)充道。“硅堆疊和 3D 模糊了封裝工程師負(fù)責(zé)的工作與芯片設(shè)計團(tuán)隊之間的界限。我們比以往任何時候都更多地看到,兩個團(tuán)隊在一個房間里從早期階段就開始規(guī)劃項目。封裝和芯片領(lǐng)域之間的協(xié)同設(shè)計有很多要求。”

在一些公司中,內(nèi)插器也被視為封裝內(nèi)的 PCB,并由另一個團(tuán)隊處理。“3D 芯片將執(zhí)行一些非常先進(jìn)的類型功能,但您不一定能夠通過堆疊芯片來構(gòu)建整個系統(tǒng)和封裝,”Mastroianni 說。“你將把它與中介層上的其他裸片結(jié)合起來。也許那里會有一個標(biāo)準(zhǔn)處理器,或者可能有多個 3D-IC 集成在一個中介層上。我認(rèn)為 3D 不會取代 2.5D。它們將是互補(bǔ)的。一些應(yīng)用程序?qū)⑹钦嬲?3D,但最終會有一些小芯片的生態(tài)系統(tǒng),你將能夠混合和匹配,并在 2.5D 封裝中做到這一點。”

只要存在層次結(jié)構(gòu),就可以將事物分開,只要存在覆蓋邊界的工具。“我們必須以層次結(jié)構(gòu)形式表示事物,因為您不再設(shè)計單個單片芯片,”Park 說。“你正在設(shè)計一個系統(tǒng),所以有一些新的東西開始發(fā)揮作用,比如系統(tǒng) LVS(layout versus schematic)。hybrid bonds是否全部對齊?從頂部裸片到底部裸片的連接是否如您所愿?有一個層次結(jié)構(gòu)只是因為你有一個層次結(jié)構(gòu)代表芯片,你有一個層次結(jié)構(gòu)代表系統(tǒng)級設(shè)計。設(shè)計本質(zhì)上是分層的,因為它是一個系統(tǒng)級設(shè)計,其中嵌入了芯片級設(shè)計。”

邏輯層次

層次結(jié)構(gòu)在任何復(fù)雜的設(shè)計中都是必不可少的,但 3D 為其添加了一個有趣的轉(zhuǎn)折。

“當(dāng)您為大型設(shè)計進(jìn)行傳統(tǒng)的布局布線時,您使用的是分層設(shè)計方法,”Mastroianni 說。“你將設(shè)計分解成塊,這些塊通過布局布線,然后你進(jìn)行頂層集成。對于 3D,我們基本上可以使用相同的過程,但我們要添加另一個層次結(jié)構(gòu)。考慮一個 90 億門的設(shè)計,我們將其分成三個芯片,每個芯片有 30 億個門。本質(zhì)上,您只需要指定哪些塊將放在芯片 1 上,哪些塊將放在芯片 2 上,以及哪些塊將放在芯片 3 上。至少在短期內(nèi),工具無法自動找出將哪個邏輯放在哪里,并在該級別進(jìn)行真正的 3D 全局布局布線。

需要一些新工具來驗證芯片到芯片的連接性。“我們通常會使用標(biāo)準(zhǔn)的觸發(fā)器到觸發(fā)器連接,”Park 說。“所以我們需要 STA 工具、時序驅(qū)動的布線、時序驅(qū)動的布局,而不是分隔設(shè)備的緩沖區(qū),它只是一個 hybrid bond。這只是一個小的寄生值發(fā)揮作用。為此,我們不能像傳統(tǒng)封裝那樣在抽象層面上工作,將它們視為黑盒。我們必須在完整的細(xì)節(jié)級別表示每個芯片或小芯片——如果是模擬設(shè)計,則為完整的晶體管級別,如果是數(shù)字設(shè)計,則為標(biāo)準(zhǔn)單元宏級別——因為我們必須能夠?qū)λ袃?nèi)容進(jìn)行建模。不是從 2D 角度對所有事物進(jìn)行建模,而是必須通過這種新的垂直方向整合來完成。”

這可能需要妥協(xié)。“您可以對邏輯堆疊對象進(jìn)行真正的 3D 簽核,或者您可以直接說,我將只運(yùn)行芯片之間兩個反相器長度的路徑,”Aitken 說。“然后無論他們在哪個角落,他們都會排成一行,我不必?fù)?dān)心。”

人們普遍認(rèn)為,扁平化不是一種選擇。“就數(shù)據(jù)量而言,這對任何 EDA 工具來說都是一個重大挑戰(zhàn),”Cadence 的 Patwardhan 說。“需要一些有效的抽象技術(shù),而層次結(jié)構(gòu)定義是第一個流行且有效的東西。我們已經(jīng)弄清楚,使用設(shè)計層次結(jié)構(gòu)以及對設(shè)計進(jìn)行分區(qū),如何在分區(qū)設(shè)計上運(yùn)行分析。可以做出哪些假設(shè)并且仍然具有與簽核一樣好的準(zhǔn)確性。它會發(fā)生,就像在 2D SoC 中發(fā)生的那樣。較小的設(shè)計將首先建立完整的平坦運(yùn)行和所需的精度水平(測量與建模)。隨著我們的前進(jìn),隨著更大的芯片以硅堆棧格式完成,EDA、OSAT、代工廠必須在分層方法和扁平方法之間進(jìn)行驗證,以保持一定的裕度。如果可用,那么您可以輕松地說您的完整平坦跑步看起來是一樣的。這是 3D-IC 設(shè)計中非常重要的方法,它不會一成不變。”

當(dāng)全 3D 布局布線成為可能時,這會變得更加困難。“今天最安全的回答是,‘我們不要分塊(block)。讓我們將每個塊保留在一個die上,我們將跨越die邊界與他們交談。這樣做,你仍然有一個必須解決的 3D 布局分區(qū)問題,但你的簽核問題更簡單,因為至少你的塊簽核被限制在 2D 空間內(nèi),”Aitken 說。“學(xué)術(shù)著作表明,移動方塊并將它們散布在邊界上可以為您帶來額外的好處。但在大多數(shù)情況下,這些論文都忽略了諸如時鐘同步、芯片匹配以及當(dāng)您嘗試執(zhí)行此類操作時會出現(xiàn)的其他問題。如果你把單獨的塊放在一個芯片上,你仍然有很多問題要解決,但與允許塊在die上遷移相比,它的問題數(shù)量要少。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論