晶體管尺寸縮小速度減慢,成本卻依然在快速飆升,盡管如此,業(yè)界仍在尋找5到10年之后的新型晶體管——尤其是對(duì)于2nm和1nm節(jié)點(diǎn)。

具體來(lái)說(shuō),業(yè)界正在為3nm的下一個(gè)主要節(jié)點(diǎn)確定和縮小晶體管選項(xiàng)。根據(jù)國(guó)際半導(dǎo)體技術(shù)路線圖(ITRS)2.0版,2.5nm和1.5nm這兩個(gè)工藝節(jié)點(diǎn),預(yù)計(jì)將分別在2027年和2030年出現(xiàn)。

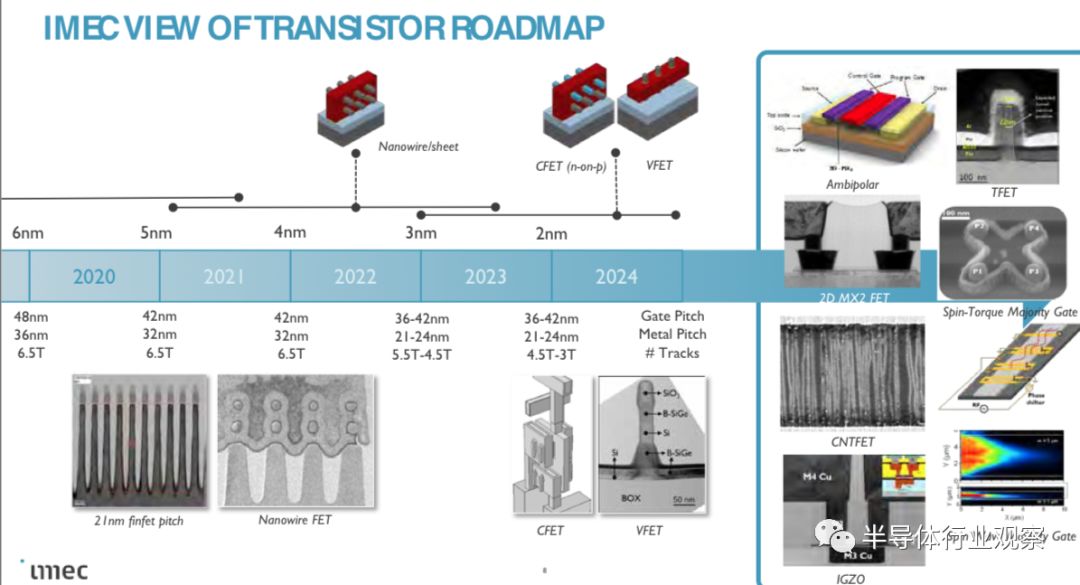

另一個(gè)機(jī)構(gòu)微電子研究中心(Imec)在時(shí)間方面更加積極,稱將在2024年實(shí)現(xiàn)2.5nm左右的工藝節(jié)點(diǎn)。

很難預(yù)測(cè)3nm以下會(huì)發(fā)生什么。實(shí)際上,由于此領(lǐng)域存在眾多未知和挑戰(zhàn),3nm及以下的工藝可能永遠(yuǎn)不會(huì)實(shí)現(xiàn)。到那時(shí)芯片尺寸縮小最終可能失去動(dòng)力。

目前及以后的幾代技術(shù)可能在5nm以下提供足夠的性能。當(dāng)今領(lǐng)先的晶體管類型finFET可能會(huì)發(fā)展到5nm或3nm(取決于節(jié)點(diǎn)的定義方式),之后,在4nm/3nm,一些正邁向下一代GAA(GAA:gate-all-around)晶體管,finFET放置在一側(cè),柵繞在其周圍。

但業(yè)界仍有可能需要GAA之外的新的更快的器件。在高性能計(jì)算、人工智能和機(jī)器學(xué)習(xí)復(fù)興之際,許多人認(rèn)為很有必要盡可能地推動(dòng)技術(shù)的發(fā)展。在未來(lái),自動(dòng)駕駛、5G、移動(dòng)和服務(wù)器也需要更多的動(dòng)力。所以在研發(fā)方面,業(yè)界正在研究2.5nm和1.5nm下的多種技術(shù)。在這些節(jié)點(diǎn)上,此行業(yè)可能會(huì)向以下這些方向發(fā)展:

O發(fā)展GAA 晶體管或開發(fā)更復(fù)雜的技術(shù),如互補(bǔ)場(chǎng)效應(yīng)晶體管(CFET)和垂直納米線晶體管。

O使用新材料調(diào)整現(xiàn)有的finFET,創(chuàng)建負(fù)電容場(chǎng)效應(yīng)晶體管(negative-capacitance FET :NC-FET)。

o將器件集成到高級(jí)封裝中。

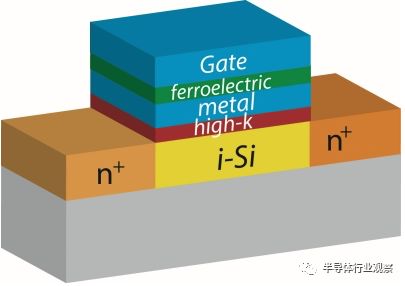

圖1:下一代晶體管架構(gòu)。來(lái)源:Imec / ISS

當(dāng)然還有其他的選擇,但預(yù)測(cè)哪個(gè)會(huì)脫穎而出還為時(shí)過早。Intel高級(jí)研究員兼工藝結(jié)構(gòu)與集成主管Mark Bohr說(shuō):「finFET是一個(gè)成功的創(chuàng)新。他們至少還可以發(fā)展一兩代。除此之外,我們還可以將材料換為鍺或III-V溝道。可能會(huì)有GAA,但目前還不清楚最終哪個(gè)會(huì)取代finFET。」

Bohr說(shuō):「無(wú)論是負(fù)電容場(chǎng)效應(yīng)晶體管、GAA還是III-V溝道,你都必須認(rèn)識(shí)到現(xiàn)代的邏輯產(chǎn)品要求非常苛刻。高的遷移率固然很好,但漏電流也必須很小,必須有低的亞閾值電壓和電源電壓。所以現(xiàn)在,我不確定在全面考慮目前CMOS可以實(shí)現(xiàn)的性能后,誰(shuí)會(huì)是真正的贏家。在選出最后的贏家之前,我們還有其他

為什么要縮小?

多年來(lái),集成電路增長(zhǎng)引擎一直圍繞著摩爾定律,摩爾定律指出,每18個(gè)月晶體管密度翻一番。根據(jù)摩爾定律,為了降低每個(gè)晶體管的成本,每18個(gè)月,芯片制造商推出一個(gè)新工藝。

摩爾定律是可行的,但同時(shí)它也在發(fā)展。在每個(gè)節(jié)點(diǎn)上,工藝成本和復(fù)雜性都在飛漲,所以一個(gè)完全按比例縮小的節(jié)點(diǎn)的改變節(jié)奏從18個(gè)月延長(zhǎng)到2.5年或更長(zhǎng)。另外,大多代工廠客戶承擔(dān)不了遷移至更先進(jìn)節(jié)點(diǎn)的費(fèi)用。

并非所有人都在轉(zhuǎn)向領(lǐng)先的節(jié)點(diǎn)。28nm及以上的工藝仍有很大的需求。令人驚訝的是,200nm晶圓廠需求仍然強(qiáng)勁。聯(lián)電(UMC)的聯(lián)席總裁Jason Wang在最近的一次電話會(huì)議上表示:「2018年各個(gè)應(yīng)用對(duì)8英寸的需求仍很強(qiáng)勁,包括RF開關(guān)的移動(dòng)領(lǐng)域、微控制單元(MCU)、嵌入式領(lǐng)域及顯示領(lǐng)域。現(xiàn)在最具挑戰(zhàn)性的事情是實(shí)際管理客戶,因?yàn)楝F(xiàn)在的需求勢(shì)不可擋。」

不過,也有一些應(yīng)用需要最新的工藝,例如機(jī)器學(xué)習(xí)、服務(wù)器和智能手機(jī)。

又如,D2S銷售基于圖形處理器的專用高端系統(tǒng)。該系統(tǒng)用于各種半導(dǎo)體制造應(yīng)用。 D2S首席執(zhí)行官Aki Fujimura說(shuō):「所以我們總是位于利用可用計(jì)算能力的邊緣,我可以非常有信心地說(shuō),我們還有很多通過計(jì)算能力來(lái)改進(jìn)半導(dǎo)體制造的方式。我確信所有其它用于高性能計(jì)算的應(yīng)用領(lǐng)域都有類似的情況。特別是隨著深度學(xué)習(xí)的興起,我預(yù)測(cè)7nm以下對(duì)更高性能計(jì)算的渴望將繼續(xù)增長(zhǎng)。」

有些應(yīng)用需要成熟和先進(jìn)的工藝,例如,汽車尤其是自動(dòng)汽車。TEL的高級(jí)技術(shù)人員Ben Rathsack說(shuō):「有兩種不同的生態(tài)系統(tǒng)。AI計(jì)算、車內(nèi)的傳感器和控制器,對(duì)那些較老的節(jié)點(diǎn)技術(shù)的需求正在增加。然后是英偉達(dá)的處理器,它們可以做AI處理,當(dāng)然,它們正在推動(dòng)高端發(fā)展。」

同時(shí),用于目前器件的制造工具已經(jīng)準(zhǔn)備好。但對(duì)于2.5nm和1.5nm來(lái)說(shuō),仍有一些差距。為了實(shí)現(xiàn)這些節(jié)點(diǎn),行業(yè)需要以下新技術(shù):

o新的光刻。7nm / 5nm需要極紫外(EUV)光刻技術(shù)。 然而, 3nm以下可能需要下一代EUV技術(shù),稱為高數(shù)值孔徑(NA)EUV。

o選擇工藝。芯片制造商還需要更廣泛的選擇性沉積和蝕刻技術(shù),使供應(yīng)商能夠在精確的位置沉積和刻蝕材料。

o新的互連方案。 芯片的布線方案過于擁擠,需要新材料。

而且,在每個(gè)節(jié)點(diǎn),缺陷越來(lái)越小,也更難找到。KLA-Tencor營(yíng)銷與應(yīng)用副總裁Mark Shirey說(shuō):「橫向縮放,即更密集的晶體管布局,需要檢測(cè)較小缺陷,也需要設(shè)計(jì)感知檢查和審查。垂直縮放推動(dòng)了檢測(cè)和驗(yàn)證隱藏缺陷的需求。」

Lam Research高級(jí)副總裁兼技術(shù)研究員David Hemker在最近的一次活動(dòng)中說(shuō):「問題變得越來(lái)越困難和復(fù)雜。但這個(gè)行業(yè)普遍的一個(gè)現(xiàn)象是,復(fù)雜和困難也意味著機(jī)會(huì)。」

在談到摩爾定律和其它相關(guān)話題時(shí),Hemker補(bǔ)充道:「我們非常看好摩爾定律可以繼續(xù)用在任何器件。我們希望達(dá)到3nm甚至更低,因此有很多選擇。」

正在進(jìn)化的finFET

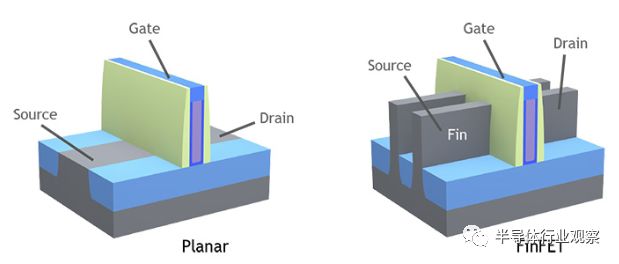

與此同時(shí),今天,芯片制造商正在增加10nm / 7nm的 finFET。 在finFET中,電流的控制是通過在鰭三個(gè)側(cè)面的每一面加一個(gè)柵極來(lái)完成的。

圖2:FinFET與平面晶體管。 來(lái)源:Lam Research

根據(jù)ITRS路線圖,在7nm之后,之后的技術(shù)節(jié)點(diǎn)為5nm,3nm,2.5nm和1.5nm。但是,這些節(jié)點(diǎn)出現(xiàn)的順序不定,節(jié)點(diǎn)任意命名的,并不反映晶體管的規(guī)格。

那么finFET會(huì)持續(xù)多久? IMEC半導(dǎo)體技術(shù)和系統(tǒng)執(zhí)行副總裁An Steegen表示:「我們相信finFET會(huì)持續(xù)到5nm節(jié)點(diǎn),當(dāng)然,這取決于縮小柵間距的困難程度。如果稍稍放寬柵間距,finFET將持續(xù)更長(zhǎng)時(shí)間。finFET之后,納米片——拉長(zhǎng)的納米線,是很好的候選者。」

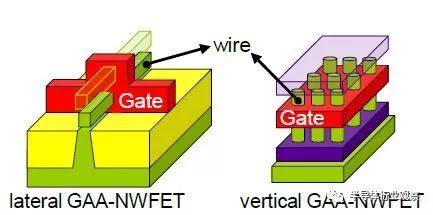

一些人認(rèn)為,finFET的繼任者是下一代稱為橫向GAA晶體管技術(shù)。在2020年左右預(yù)計(jì)會(huì)發(fā)展到4nm和/或3nm,GAA是finFET進(jìn)化的下一步。

兩種主要類型的全柵FET是納米線FET和納米片F(xiàn)ET。在納米線FET中,細(xì)線用作通道,納米片F(xiàn)ET則將片狀材料用作通道。

圖3:(a)finFET,(b)納米線和(c)納米片的橫截面模擬。來(lái)源:IBM

GAA對(duì)門有更好地控制,提高了性能,減小了泄露。應(yīng)用材料公司(Applied Materials)技術(shù)項(xiàng)目總經(jīng)理Mike Chudzik說(shuō):「這種改進(jìn)的門控制可以繼續(xù)使門長(zhǎng)度得以縮小。」

使用現(xiàn)在的晶圓廠工具和設(shè)計(jì)技術(shù)可以發(fā)展GAA器件。例如,芯片制造商可以利用設(shè)計(jì)技術(shù)協(xié)同優(yōu)化這種成熟技術(shù)。

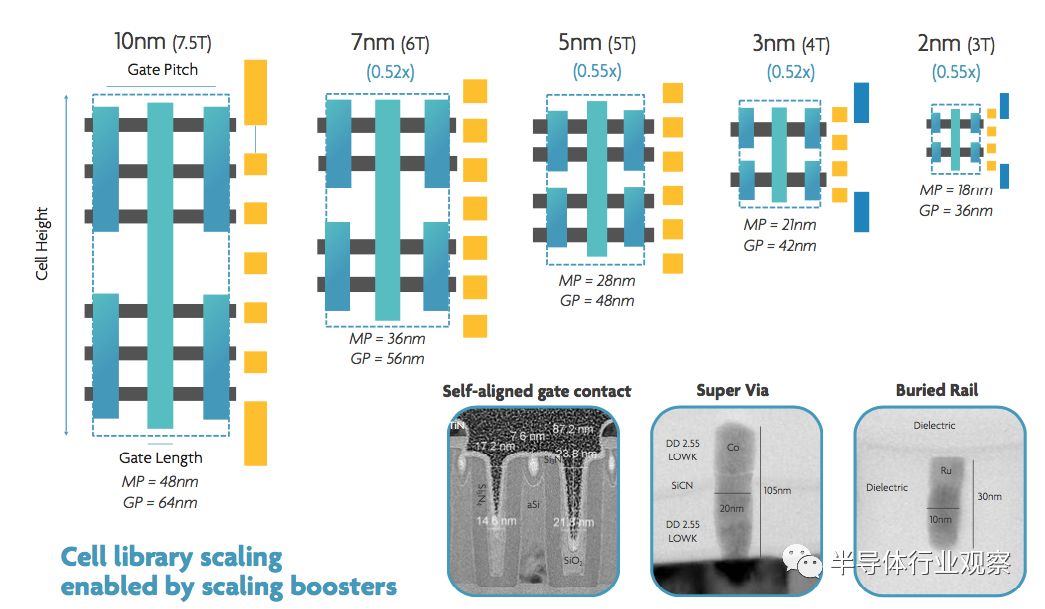

這里的想法是每個(gè)節(jié)點(diǎn)下減少標(biāo)準(zhǔn)單元layout的軌道高度和單元大小。標(biāo)準(zhǔn)單元是設(shè)計(jì)中的預(yù)定義邏輯單元。這些單元放置在一個(gè)網(wǎng)格中。軌道定義了標(biāo)準(zhǔn)單元layout的高度。例如,根據(jù)Imec的說(shuō)法,7nm下可能有6軌道高度的單元,使器件的柵間距為56nm,金屬間距為36nm。

根據(jù)Imec的說(shuō)法,4nm / 3nm下涉及5.5-4.5軌道高度的layout,使柵極間距從36nm到42nm,金屬間距從21nm到24nm的器件成為可能。

圖4:縮放增強(qiáng)器(scaling boosters)下的單元庫(kù)縮放。 來(lái)源:Imec

基于路線圖,橫向納米線/納米片F(xiàn)ET可以從4nm / 3nm發(fā)展到約2nm,這意味著該技術(shù)可能僅持續(xù)一或兩個(gè)節(jié)點(diǎn)。

在2nm下,該行業(yè)面臨一些障礙。理論上說(shuō),2nm器件將由3軌高度layout構(gòu)成,但至少現(xiàn)在這種類型的方案很難想象。Imec的項(xiàng)目總監(jiān)Diederik Verkest說(shuō):「制造一個(gè)標(biāo)準(zhǔn)的單元至少需要3軌道高度。使用這種架構(gòu),會(huì)非常有挑戰(zhàn)性。」

總而言之,這個(gè)行業(yè)可能需要一個(gè)新的解決方案。 但芯片制造商不想從頭開始。 而傾向于基于現(xiàn)有的工作和制造技術(shù)進(jìn)行改進(jìn)。

圖5:Imec對(duì)晶體管路線圖的看法。

Imec提出了兩種選擇——互補(bǔ)場(chǎng)效應(yīng)晶體管(CFET)和垂直納米線。 針對(duì)2.5nm及以下的工藝,CFET是一種更復(fù)雜的全柵型器件。傳統(tǒng)的全柵場(chǎng)效應(yīng)晶體管將多條p型導(dǎo)線堆疊在一起。在單獨(dú)的器件中,晶體管彼此堆疊n型導(dǎo)線。

在CFET中,是將nFET和pFET導(dǎo)線相互堆疊在一起。CFET可以將一個(gè)nFET堆疊在pFET導(dǎo)線的頂部,或者將兩個(gè)nFET堆疊在兩個(gè)pFET導(dǎo)線的頂部。

由于CFET將n型和p型器件疊放在一起,這樣晶體管有一些優(yōu)點(diǎn)。Verkest說(shuō):「主要好處是面積,面積縮放帶來(lái)了功率和性能上的優(yōu)勢(shì)。就靜電控制而言,CFET與一般的納米線相同,它們都是GAA結(jié)構(gòu)。」

其它的好處還不清楚。CFET可以使面積縮的更小,但它樣與傳統(tǒng)GAA晶體管的規(guī)格大致相同。

CFET更難制造,可能需要更高的結(jié)構(gòu)。這反過來(lái)可能意味著更高的電容。

另一種解決方案是垂直納米線FET(VFET)。橫向GAA晶體管將導(dǎo)線水平堆疊。 相反,VFET垂直地堆疊導(dǎo)線。 源極,柵極和漏極堆疊在一起。這意味著面積會(huì)有所增加。

圖6:橫向納米線FET與垂直納米線。 FET來(lái)源:Imec

VFET有一些缺點(diǎn)。VFET是縮放SRAM的有效器件,但它不是一個(gè)縮小邏輯單元的器件。

VFET也很難在晶圓廠制造,但該技術(shù)已在實(shí)驗(yàn)室中得到證明。在IEDM上,Imec、Lam Research和KU Leuven提交了一篇關(guān)于垂直納米片和III-V材料的VFET論文。 在該工藝中,圖案通過電子束光刻在結(jié)構(gòu)上形成。 根據(jù)此論文,通過蝕刻表面,形成直徑范圍從25nm到75nm,陣列為1到100的垂直納米線。

什么是負(fù)電容場(chǎng)效應(yīng)晶體管?

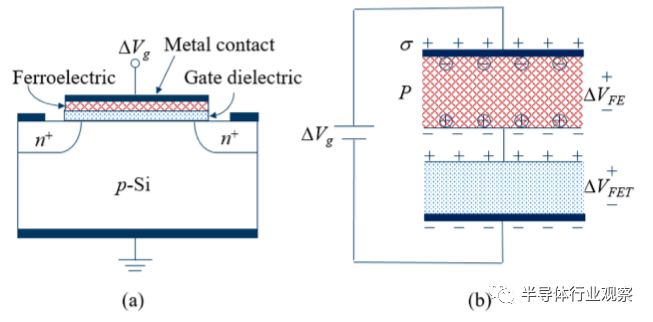

還有其他選擇。 2008年,普渡大學(xué)(Purdue University)的研究人員提出了負(fù)電容FET(NC-FET)的想法。

針對(duì)3nm及以下工藝,NC-FET不是新器件。一個(gè)NC-FET采用現(xiàn)有的晶體管和基于氧化鉿的高k /金屬柵疊層,然后,柵極疊層被修改為鐵電性質(zhì),產(chǎn)生遠(yuǎn)低于60mV/decade極限的陡峭的亞閾值斜率器件。

圖7:負(fù)電容FET。 資料來(lái)源:PeterGrünberg半導(dǎo)體納米電子學(xué)研究所

平面器件、finFET甚至GAA器件都可以使用鐵電性質(zhì)進(jìn)行改進(jìn),只要它包含氧化鉿。 Applied的Chudzik說(shuō):「基本上,鐵電體就像電壓放大器。你輸入一個(gè)電壓,由于它相互作用的方式,會(huì)放大電壓。這就是得到增強(qiáng)的亞閾值斜率的原因。」

圖8:NC-FET原理圖。 來(lái)源:SRC,內(nèi)布拉斯加大學(xué)林肯分校

NC-FET與隧道FET(TFET)屬于同一類別,都可用作未來(lái)陡峭的亞閾值晶體管。雖然,TFET與NC-FET不同,TFET需要一個(gè)全新的結(jié)構(gòu)。

NC-FET與一種稱為鐵電FET(FeFET)的技術(shù)有關(guān)。 NC-FET和FeFET都利用氧化鉿中的鐵電特性。

FeFET和NC-FET不同。正在開發(fā)FeFET的公司Ferroelectric Memory Co.(FMC)的首席執(zhí)行官StefanMüller說(shuō):「最重要的區(qū)別是,NC-FET用于邏輯,而FeFET用于存儲(chǔ)。一般而言,NC-FET是沒有非易失性存儲(chǔ)性質(zhì)的邏輯器件,F(xiàn)eFET是一種非易失性存儲(chǔ)器件。」

在這兩種情況下,將鐵電材料夾在兩種其它材料之前并通過沉積將其沉積到基于鉿的柵極疊層中。Müller說(shuō):「在 FeFET中,希望使鐵電體和硅體材料之間的緩沖區(qū)盡可能薄,這與數(shù)據(jù)保留有關(guān)。緩沖層越薄,數(shù)據(jù)保留越好。NC-FET不同,NC-FET晶體管不用保留數(shù)據(jù)。也就是說(shuō),鐵電體和硅體之間的緩沖層的要求不同。」

舉例來(lái)說(shuō),GlobalFoundries最近發(fā)表了一篇關(guān)于14nm finFET測(cè)試的論文,該論文在柵堆疊中結(jié)合了摻雜的二氧化鉿鐵電層。 GlobalFoundries將其稱為14nm鐵電finFET,可以歸類為具有負(fù)電容的finFET或NC-FET。

在14nm finFET中,GlobalFoundries測(cè)試厚度為3nm,5nm和8nm的鐵電層。他們還測(cè)試了1.5nm的未摻雜層。GlobalFoundries高級(jí)技術(shù)人員Zoran Krivokapic說(shuō)在論文中說(shuō):「我們發(fā)現(xiàn)8nm薄膜仍可以產(chǎn)出功能器件(functional device)。 鐵電器件顯示改進(jìn)的亞閾值斜率低至54mV / dec。這是我們第一次展示帶有鐵電器件的環(huán)形振蕩器可以在類似于常規(guī)電介質(zhì)的頻率下工作,而改善的亞閾值斜率降低了它們的有功功率(active power)。」

雖然NC-FET面臨一些挑戰(zhàn),但Applied的Chudzik說(shuō):「有很多的希望和興趣,也有很多未解決的問題。有了柵,放置鐵電材料的體積有限。鐵電材料很厚,50到80埃。這將使現(xiàn)代finFET與它的差距減小。該行業(yè)已經(jīng)處于7nm,所以他們需要不改變其鐵電性質(zhì)的前提下縮小這種材料。可靠性是一個(gè)挑戰(zhàn)。由于一些寄生效應(yīng),也可能會(huì)有一些獨(dú)特的器件設(shè)計(jì)限制。」

其他解決方案

IC制造商也在尋求芯片縮小的替代方案。其中一個(gè)想法是將多個(gè)器件放在一個(gè)高級(jí)封裝中,這樣可以在較低的成本下提供與縮放器件相同的功能。

有人稱此為混合縮放或異構(gòu)集成。Imec的Steegen說(shuō):「我不認(rèn)為人們會(huì)說(shuō),‘現(xiàn)在我們將停止器件縮放,切換到混合縮放,想一下現(xiàn)在的封裝,不同的堆疊方式用于一種封裝,你可以看到這已經(jīng)成為混合縮放的一種形式。你可以說(shuō)它現(xiàn)在已經(jīng)開始,也可以繼續(xù)在這條道路上前進(jìn)。

下一步是什么? 超過1.5nm,路線圖將看不到“陽(yáng)光”。在Imec的路線圖上,有幾種未來(lái)科技,如TFET和自旋波器件,也可能是3D納米結(jié)構(gòu)(3D NAND的邏輯版本)。

這些未來(lái)器件將需要新的工具和材料,也需要資金。

很明顯,比5nm以下出現(xiàn)的問題還要多。也許GAA是答案,也許研究人員會(huì)偶然發(fā)現(xiàn)一種新技術(shù)。當(dāng)然,今天的技術(shù)可能會(huì)持續(xù)更長(zhǎng)時(shí)間,推開這些新型晶體管的需求。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28723瀏覽量

234592 -

電容

+關(guān)注

關(guān)注

100文章

6241瀏覽量

153601 -

晶體管

+關(guān)注

關(guān)注

77文章

9995瀏覽量

141028

發(fā)布評(píng)論請(qǐng)先 登錄

臺(tái)積電3nm工藝計(jì)劃每平方毫米集成2.5億晶體管 2022年大規(guī)模量產(chǎn)

10nm、7nm等制程到底是指什么?宏旺半導(dǎo)體和你聊聊

我國(guó)首次實(shí)現(xiàn)3nm晶體管技術(shù) 技術(shù)具體如何

新型垂直納米環(huán)柵晶體管,或是2nm及以下工藝的備選

臺(tái)積電3nm晶體管密度達(dá)到2.5億/mm2

臺(tái)積電正式披露3nm工藝最新細(xì)節(jié) 晶體管密度達(dá)到2.5億/mm2

揭秘3nm GAE MBCFET 芯片的制造細(xì)節(jié)

臺(tái)積電3nm工藝進(jìn)度超前 EUV工藝獲突破:直奔1nm

晶體管在3nm達(dá)到臨界點(diǎn)

三星電子3nm良品率才10%-20%,大大低于預(yù)期

三星3nm芯片開始量產(chǎn),采用GAA晶體管,提升巨大

3nm芯片什么時(shí)候出 3nm芯片有多少個(gè)晶體管

全球首顆3nm電腦來(lái)了!蘋果Mac電腦正式進(jìn)入3nm時(shí)代

分享3nm以后的晶體管的選擇分析

分享3nm以后的晶體管的選擇分析

評(píng)論