SCAN技術(shù),也就是ATPG技術(shù)-- 測(cè)試std-logic, 主要實(shí)現(xiàn)工具是:

產(chǎn)生ATPG使用Mentor的 TestKompress和synopsys TetraMAX;

插入scan chain主要使用synopsys 的DFT compiler。

通常,我們所說(shuō)的DCSCAN就是normal scan test 即慢速測(cè)試,測(cè)試頻率是10M-30M

AC SCAN 也就是at-speed scan 即實(shí)速測(cè)試,測(cè)試頻率與芯片真實(shí)工作頻率是一樣的。

70年代到1995年這段時(shí)間里,由于芯片的工作頻率很低只有20-100M,scan測(cè)試只有DC SCAN,我們就能捕捉到所有std-logic的制造缺陷。但是1995年以后,測(cè)試科學(xué)家和工程師發(fā)現(xiàn)通過(guò)DC SCAN測(cè)試沒(méi)有缺陷的芯片在高工作頻率下使用會(huì)有問(wèn)題。其根本原因是隨著制造工藝向深亞微米邁進(jìn),芯片的工作頻率也提高到200M-1G,原來(lái)的SCAN測(cè)試方法和模型不再能捕捉到所有的std-logic的制造缺陷。大家的一致想法就是-“奔跑吧,SCAN” ,把SCAN的頻率增加到與芯片的真實(shí)工作頻率一致,同時(shí)使用新的Transition atpg model來(lái)產(chǎn)生測(cè)試pattern.

下面我們介紹DC SCAN與AC SCAN的異同

現(xiàn)在的工業(yè)量產(chǎn)的高速芯片都會(huì)要求能做DC SCAN測(cè)試和AC SCAN測(cè)試,所以DFT工程師也要同時(shí)插入兩種測(cè)試電路,產(chǎn)生兩套測(cè)試patterns。

具體實(shí)現(xiàn)流程如下

1 讀入沒(méi)有插入scan的網(wǎng)表

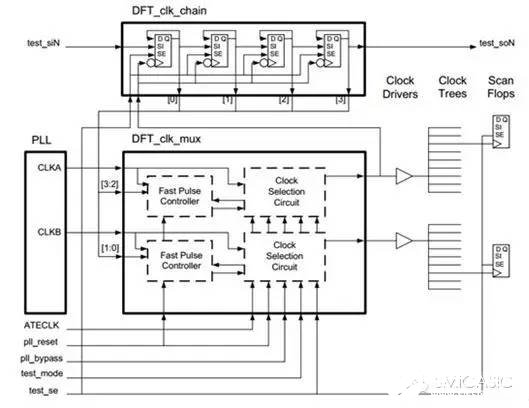

2 使用Design compiler 插入scan chain和OCC (on chipclocking)模塊,同時(shí)插入mux, fix DRC

3 使用Testcompress 實(shí)現(xiàn)EDT壓縮scan chain

4 使用Testcompress 產(chǎn)生測(cè)試DC/ACpattern,同時(shí)產(chǎn)生測(cè)試驗(yàn)證的Testbench

5 驗(yàn)證DC/AC patterns的正確性和電路的正確性

6 使用SDF,驗(yàn)證DC/ACpatterns相關(guān)電路的時(shí)序是否滿(mǎn)足要求

7 使用DC/AC patterns (wgl文件)轉(zhuǎn)換成ATE所需格式,在ATE上調(diào)試和使用

所以,OCC電路實(shí)現(xiàn)了在shift階段和capture階段對(duì)時(shí)鐘(PLL/ATE)進(jìn)行選擇的功能。有兩種方式可以插入OCC電路:

1. DFT Compiler自動(dòng)插入。2. 手動(dòng)編寫(xiě)OCC 的verilog 電路,在dft_insert階段。

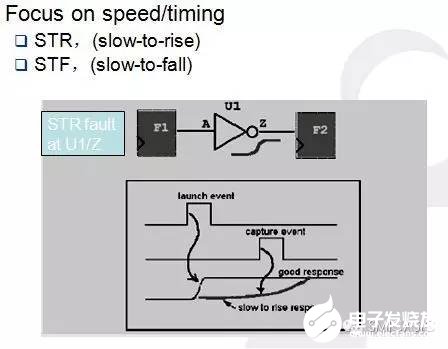

ATPG工具使用的Transition faultmodel如下圖

OCC :On Chip Clock

OPCG :On-Product Clock Gating

SCM:scan clock mux

上面三種是同一東西的不同叫法,就是為了at-speed ATPG測(cè)試時(shí)在function clock和shift clock之間切換的控制邏輯。不同人設(shè)計(jì)的電路不一樣,它就是一個(gè)2選一的clock mux,設(shè)計(jì)時(shí)注意處理一下cdc的path,不要產(chǎn)生glitch就行了。

何為全速測(cè)試(at speed test):在工藝節(jié)點(diǎn)在130nm以下的時(shí)候,很多情形下的物理缺陷都是由于延時(shí)來(lái)引起的。因此在對(duì)這種類(lèi)型的chip做dft的時(shí)候,需要建立一個(gè)新的故障模型,業(yè)內(nèi)稱(chēng)之為延時(shí)故障模型(time delay model)。解決的方法就是全速測(cè)試,所謂的全速測(cè)試就是讓芯片工作在自己高倍時(shí)鐘頻率上,這個(gè)頻率往往是要高過(guò)ATE的時(shí)鐘的。這樣對(duì)掃描模型的建立就提出了新的要求。即至少要保證芯片的latch clock和capture clock為芯片內(nèi)部的高倍時(shí)鐘。synopsys對(duì)此種問(wèn)題的解決方法就是OCC(on chip clocking)。OCC/OPCG的基本原理是在 scan shift 模式下, 選通慢速的ATE 時(shí)鐘,load 或 unload 掃描鏈; 在 capture 模式下,對(duì) free-running PLL clock 過(guò)濾篩選出 lauch 和 capture clock 進(jìn)行at-speed 測(cè)試

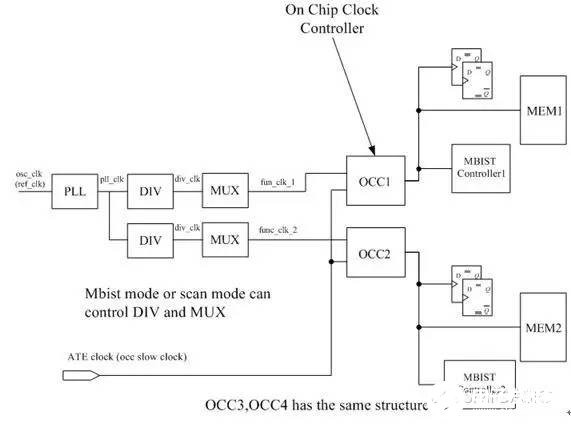

常用的OCC電路結(jié)構(gòu)如下

在做SCAN的時(shí)候,由于ATE時(shí)鐘速度和芯片port的傳輸速度的限制,導(dǎo)致ATE無(wú)法向片傳輸高速時(shí)鐘。但是,芯片內(nèi)部需要 進(jìn)行At Speed 測(cè)試的時(shí)候,用到和system mode一致的時(shí)鐘頻率進(jìn)行測(cè)試。此時(shí),需要由芯片內(nèi)部自己產(chǎn)生測(cè)試時(shí)鐘。在capture的時(shí)候,對(duì)于內(nèi)部寄存器來(lái)說(shuō),到達(dá)clock pin上的時(shí)鐘波形如intclk 所示。Launche clock和capture clock為PLL產(chǎn)生的脈沖。Shift clock為ATE產(chǎn)生的時(shí)鐘。PLL時(shí)鐘和ATE時(shí)鐘的切換電路是由OCC (On-Chip Clocking) 電路實(shí)現(xiàn)的。

我們典型的插入OCC以后的電路如下圖

-

制造工藝

+關(guān)注

關(guān)注

2文章

203瀏覽量

20305 -

控制邏輯

+關(guān)注

關(guān)注

0文章

14瀏覽量

2458

發(fā)布評(píng)論請(qǐng)先 登錄

使用DLP_LightCrafter_6500_3D_Scan_Application.exe時(shí)出現(xiàn)界面的閃退的原因?怎么解決?

請(qǐng)問(wèn)DLP_LightCrafter_4500_3D_Scan_Application.exe可以使用灰點(diǎn)的網(wǎng)口相機(jī)測(cè)試嗎?

按照dlpu042.pdf的流程生成的DLP_LightCrafter_4500_3D_Scan_Application.exe運(yùn)行時(shí)會(huì)報(bào)錯(cuò)怎么解決?

DLP_LightCrafter_4500_3D_Scan_Application軟件進(jìn)行相機(jī)和投影儀標(biāo)定時(shí),進(jìn)入相機(jī)拍照界面后程序未響應(yīng)然后退出怎么解決?

DLPNIRSCANEVM掃描時(shí)出現(xiàn)‘scan failed\'.如何解決?

ADS1258在Auto-scan mode Pulse converting時(shí)么連續(xù)采集0,1,2通道數(shù)據(jù)?

ac耦合和dc耦合波形的區(qū)別是什么

示波器ac耦合和dc耦合的區(qū)別

如何不用wifi_station_scan() 取得當(dāng)前已經(jīng)連線(xiàn)AP的BSSID?

Curl命令來(lái)scan沒(méi)有結(jié)果的原因?

SCAN90004 4通道LVDS緩沖器/中繼器數(shù)據(jù)表

在Nucleo-H743ZI2板上運(yùn)行wifi_scan示例,啟用FreeRTOS時(shí)堆部分被禁用,為什么?

使用psoc62+CYW43012掃描信標(biāo)時(shí),wiced_bt_ble_scan返回WICED_BT_NO_RESOURCES如何解決?

SCAN15MB200雙通道1.5 Gbps 2:1/1:2 LVDS多路復(fù)用器/緩沖器數(shù)據(jù)表

DC SCAN與AC SCAN的異同 常用的OCC電路結(jié)構(gòu)分析

DC SCAN與AC SCAN的異同 常用的OCC電路結(jié)構(gòu)分析

評(píng)論