本文簡要描述基于FPGA和萬兆網(wǎng)的GigE Vison IP設計方案。

一、GigE Vsion協(xié)議要點

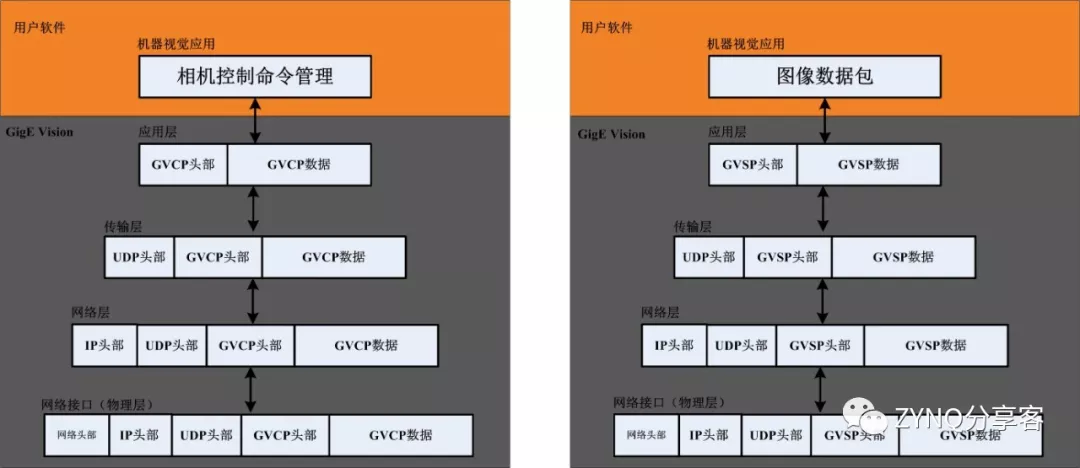

GigE Vison協(xié)議基于普通的以太網(wǎng)物理鏈路,運行在UDP協(xié)議層之上,包含控制協(xié)議GVCP和數(shù)據(jù)流協(xié)議GVSP兩大部分,整個層次結構如下圖1所示。

圖1 GigeVison協(xié)議層次結構圖

GigE Vison協(xié)議的要點如下:

(1)上電或復位完成后必須先進行IP配置和設備枚舉,必須支持DHCP和LLA(Auto IP)兩種IP配置方式;

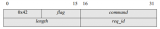

(2)在UDP層上建立應答握手機制以保證傳輸,GVCP采用3956端口,數(shù)據(jù)長度必須以32bit為邊界,數(shù)據(jù)不可分包傳輸;

(3)設備必須支持心跳功能以確認處于連接狀態(tài);

(4)支持控制(1個)、數(shù)據(jù)流(1~512個)和消息(0~1個)三種通道,每個通道分配不同的UDP端口,控制通道支持三種不同的訪問權限;

(5)必須支持最小規(guī)模的ICMP(GigeVsion要求必須支持Ping命令);

(6)GVSP的數(shù)據(jù)包以字節(jié)為邊界,數(shù)據(jù)包的大小由第一個有效的test packets決定,支持錯誤恢復和流控制;

(7)GVSP數(shù)據(jù)傳輸?shù)膯挝粸锽lock,一個完整的Block由Data Leader、Data Payload和Data Trailer構成;

(8)所有的Gige Vison相機都必須在他們的XML描述文件中強制制定相機的參數(shù)信息。

(9)bootstrap寄存器及XML文件需要非易失Flash硬件支持。

二、IP功能設計方案要點描述

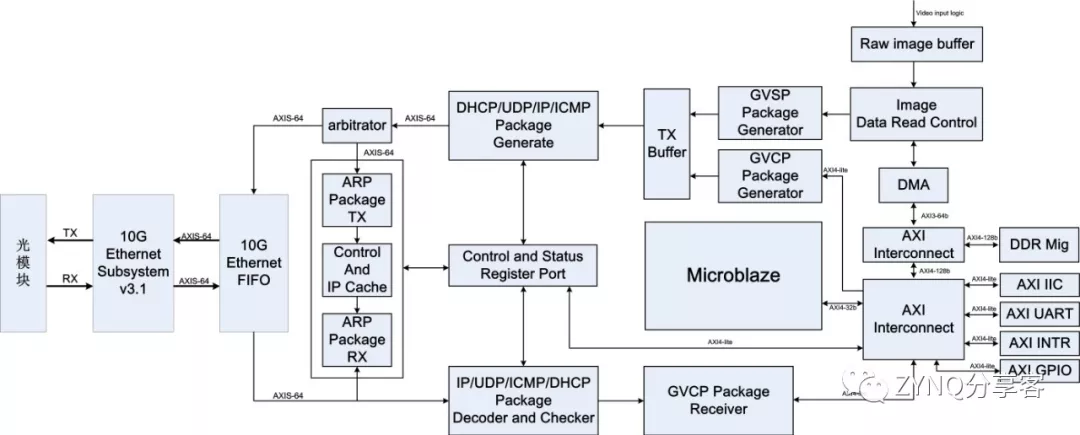

GigE Vison邏輯IP需要實現(xiàn)圖1所示的所有協(xié)議層,方案中硬件平臺基于Xilinx 7系列器件XC7K325T/XC7K160T,下圖2是GigE Vision IP核的模塊框架結構。

圖2 GigE Vision IP核的框架結構

(1)物理層

物理層使用Xilinx 10G Ethernet Subsystem IP核,版本v3.1。對外數(shù)據(jù)接口例化為AXI4 Stream,位寬64bit,數(shù)據(jù)時鐘156.25MHz;配置接口例化為AXI4-Lite,位寬32bit,時鐘頻率100MHz。

IP核配置通過Microblaze軟核完成,并且使能Jumbo幀功能。功能、接口、配置和使用說明參見Xilinx官方文檔PG157。

(2)IP/UDP層

IP層協(xié)議僅支持IPv4版本,IP數(shù)據(jù)報頭Options項為空;需要支持DHCP、ARP和ICMP協(xié)議,內(nèi)部通信采用64位AXI4 Steam總線通信。

(3)GVCP/GVSP協(xié)議

支持GigE Vison Specification version 1.0標準描述的所有必須支持的項,GVSP數(shù)據(jù)包負載類型支持Payload type = RawData/YUV422-8bit/RGB888。為完整實現(xiàn)功能,部分控制放在處理器上完成(本設計實例使用MicroBlaze),需要掉電保存的項存儲在外部Flash中,需要大量緩存的數(shù)據(jù)存儲在片外DDR中。

RTL描述語言使用Verilog,編譯工具使用XilinxVivado2016.4,仿真工具使用ModelSim 10.2C。

備注:

(1)為簡化邏輯端的設計難度,可將GVCP協(xié)議放在Microblaze里面實現(xiàn),使用ZYNQ系列器件的,可以直接在PS里運行;

(2)物理層使用千兆網(wǎng)的,本方案仍然可行,只需修改物理層接口即可;使用ZYNQ系列器件的,可以直接在PS里軟件實現(xiàn)所有的GVCP和GVSP協(xié)議;

三、測試結果

在Xilinx K7 325T器件上實現(xiàn)完整的系統(tǒng)(包括DDRMig、Microblaze等),占用Slice約30K。

與PC進行點對點數(shù)據(jù)傳輸測試,穩(wěn)定傳輸速率約為6.5Gbps,可輕松傳輸4K無壓縮原圖或一些特殊圖像數(shù)據(jù)如超聲、CT、雷達等原始數(shù)據(jù)。

-

FPGA

+關注

關注

1645文章

22033瀏覽量

617730 -

以太網(wǎng)

+關注

關注

41文章

5630瀏覽量

175710 -

GigE Vision

+關注

關注

0文章

5瀏覽量

5808

發(fā)布評論請先 登錄

Altera FPGA 的PIO IP當中bidir和inout選項的區(qū)別

FPGA調(diào)試方式之VIO/ILA的使用

高速多層板SI/PI分析的關鍵要點是什么

海外住宅IP代理優(yōu)勢綜合分析

將40+臺GigE工業(yè)相機連接到單一系統(tǒng)竟能零錯誤運行數(shù)天!

使用IP核和開源庫減少FPGA設計周期

基于FPGA的GigE Vision相機圖像采集方案設計

網(wǎng)絡研討會: Teledyne FLIR IIS Forge 5GigE高速高精度機器視覺工業(yè)相機

解鎖跨國業(yè)務:國外IP節(jié)點選擇與性能分析

如何查看公共IP地址安全?這些要點要牢記

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰(zhàn)的任務!

東京裸機云多IP服務器全面分析

基于FPGA的CCD工業(yè)相機系統(tǒng)設計

基于FPGA的GigE Vison IP設計要點分析

基于FPGA的GigE Vison IP設計要點分析

評論