上一期的學習中,我們系統(tǒng)性地介紹了PYNQ與ZYNQ地區(qū)別與聯(lián)系。PYNQ = Python + ZYNQ,即將ZYNQ部分功能的Python化,直接調(diào)用Python庫和FPGA硬件庫進行功能的開發(fā)。

Pynq降低了開發(fā)人員的門檻,但知其然也知其所以然,開發(fā)效率將會更高。因此,在進入PYNQ的python開發(fā)之前,我們先來學習ZYNQ的PL與PS開發(fā),為接下來的學習提供良好的基礎。

本部分的學習,我們依舊借助PYNQ_z2來完成。

1. ZYNQ功能塊

ZYNQ中包含兩大功能塊:PS部分和PL部分。

PS部分指Processing System,一個基于雙ARM Cortex A9內(nèi)核的處理系統(tǒng),其中集成了內(nèi)存存儲器和外部存儲器接口,以及如GPIO、UART接口等大量的外設。

PL部分指Programmable Logic,基于Xilinx 7系列架構的可編程邏輯單元,通過PL部分可以為ARM定制很多外設,這也是ZYNQ的一大優(yōu)點。

2. ZYNQ整體架構

ZYNQ中雖然包含PS端和PL端,但是整個設計是以ARM處理器為中心的,PS端的ARM內(nèi)核可以獨立于PL端運行;雖然PL端也可以獨立于PS端運行,但是PL的配置是由PS端完成的,所以不能采用傳統(tǒng)的固化FLASH的方式固化PL端程序。

PS端和PL端通信是通過AXI接口協(xié)議連接,這個協(xié)議是AMBA的一部分,是一種高性能、高帶寬、低延遲的片內(nèi)總線。

3. vivado與PL開發(fā)

下面我們通過一個LED燈的小項目進行本部分學習:

實驗:輪流點亮LED燈

1. 打開vivado hls,點擊Create New Project Project”,創(chuàng)建一個新工程。

選擇板子的時候搜索xc7z020clg400-1,這是PYNQ的板子號,選擇完成(PYNQ-Z2板采用ZYNQ XC7Z020-1CLG400C SoC)。

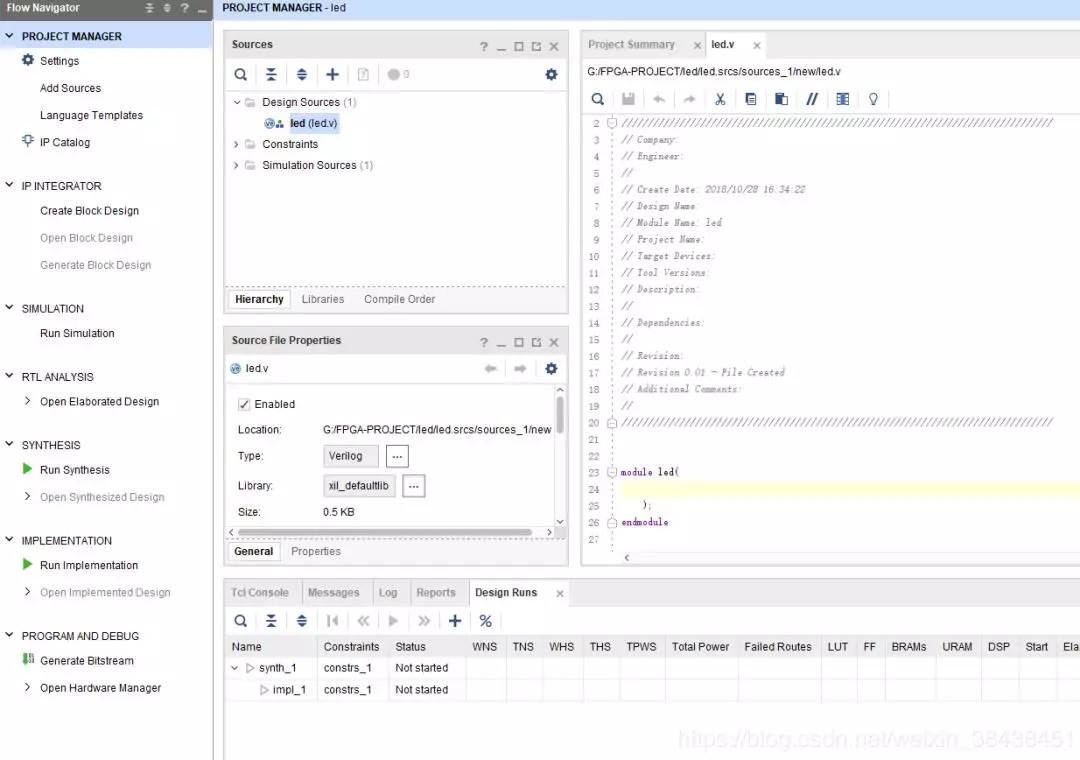

3. 新建一個 VerilogHDL 文件,可以通過右擊 Design sourse 選擇 AddSourse,選擇第二個選項

選擇 CreateFile…在彈出下面窗口填寫新建源文件名稱

創(chuàng)建完成點擊 Finish

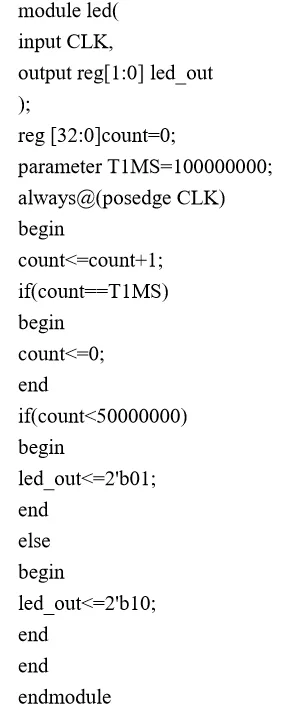

4. 在用戶區(qū) VerilogHDL 文件窗口中輸入源程序,保存時文件名與實體名 保持一致,代碼如下:

得到的最終界面:

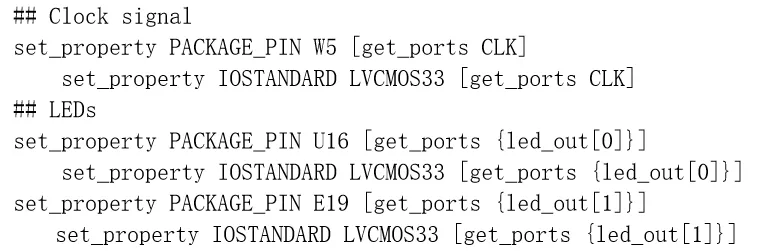

5. 新建約束文件,輸入下面指令

在彈出的對話框中可以選擇任務數(shù)量,這里和CPU核心數(shù)有關,一般數(shù)字越大,編譯越快,單擊”O(jiān)K”

9. 這個時候開始編譯,可以看到右上角有個狀態(tài)信息,在編譯過程中可能會被殺毒軟件、電腦管家攔截運行,導致無法編譯或很長時間沒有編譯成功。

編譯中沒有任何錯誤,編譯完成,彈出一個對話框讓我們選擇后續(xù)操作,這里選項“open hardware manager” ,然后單擊“OK”

10. 下載到板子

1)連接好開發(fā)板的 JTAG接口,給開發(fā)板上電

2)可以看到JTAG掃描到arm和 FPGA 內(nèi)核

3)選擇FPGA內(nèi)核,右鍵選擇“Program Device...” ,在彈出窗口中點擊“Program”

4)等待下載,下載完成以后,我們可以看到4 顆LED開始每秒變化一次

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614798 -

led

+關注

關注

242文章

23748瀏覽量

671543 -

python

+關注

關注

56文章

4825瀏覽量

86313

發(fā)布評論請先 登錄

正點原子Z20 ZYNQ 開發(fā)板發(fā)布!板載FMC LPC、LVDS LCD和WIFI&藍牙等接口,資料豐富!

ZYNQ FPGA的PS端IIC設備接口使用

Zynq7000處理器的配置詳解

從零開始馴服Linux(一):ZYNQ-Linux啟動文件構建全解析

ZYNQ基礎---AXI DMA使用

基于Xilinx ZYNQ7000 FPGA嵌入式開發(fā)實戰(zhàn)指南

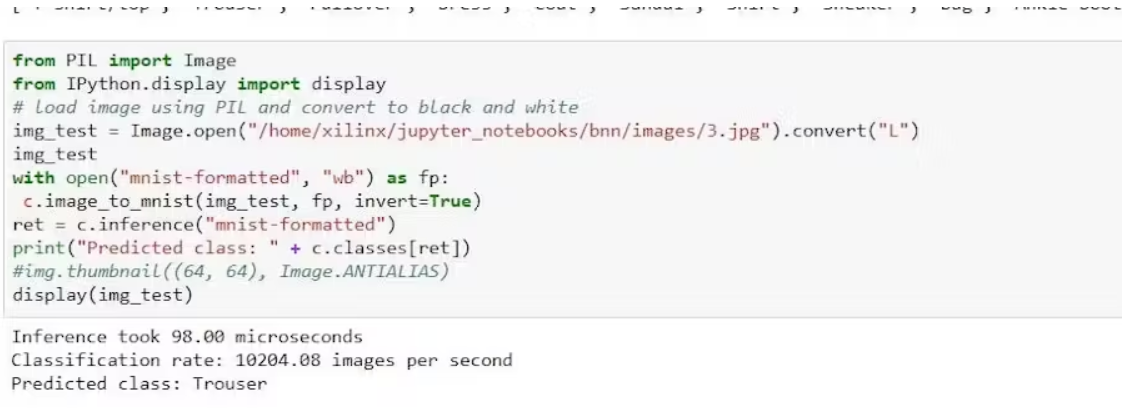

基于PYNQ和機器學習探索MPSOC筆記

PICO-IMX8PL和SRG-IMX8PL:共創(chuàng)您的物聯(lián)網(wǎng)集成網(wǎng)關

PYNQ案例(一):ZYNQ的PL與PS開發(fā)

PYNQ案例(一):ZYNQ的PL與PS開發(fā)

評論