所謂的Xnet,是指在無源器件的兩端,兩個不同的網(wǎng)絡(luò),但是本質(zhì)上其實是同一個網(wǎng)絡(luò)的這種情況。比如一個源端串聯(lián)電阻或者串容兩端的網(wǎng)絡(luò)。在實際設(shè)計情況中,我們需要對這種進(jìn)行Xnet的設(shè)置,方便進(jìn)行時序等長的設(shè)計,一般信號傳輸要求都是信號的傳輸總長度達(dá)到要求,而不是分段信號等長,這時采用Xnet就可以非常方便的實現(xiàn)這一功能,在allegro軟件中添加xnet的具體步驟如下所示:

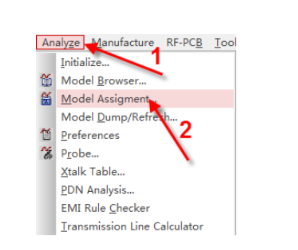

第一步,執(zhí)行菜單命令A(yù)nalyze-Model Assigment,進(jìn)行模型的指定,如圖5-112所示;

圖5-112 創(chuàng)建模型示意圖

第二步,點擊指定模型之后,會彈出如圖5-113所示的界面,這些是沒有解決的問題,一般都是電壓的問題,系統(tǒng)會顯示這個是個電源,但是并沒有賦予電壓值,所以會顯示錯誤。一般我們添加Xnet可以忽略掉這些,不用管這些錯誤,直接點擊OK按鈕即可;

圖5-113 SI Design Audit示意圖

第三步,在PCB界面點擊需要設(shè)置Xnet模型的元器件,右側(cè)對應(yīng)列表中會同步進(jìn)行選中,也可以將同一類型的全部選中,如圖5-114所示;

圖5-114 給元器件創(chuàng)建模型示意圖

第四步,選中需要創(chuàng)建模型的元器件之后,點擊如圖352-3所示的列表的下方“Create Model”選項,進(jìn)行模型的創(chuàng)建,在彈出的界面中,按照默認(rèn)的即可,選擇“Create ESpiceDevice model”即可,如圖5-115所示;

圖5-115 給元器件創(chuàng)建模型示意圖

第五步,在彈出的對話框中,如圖5-116所示,需要我們自己填寫的是:Value值按照實際Value值去填寫,仿真的時候會用到這個數(shù)據(jù);Single Pins需要我們?nèi)?yīng)好電阻的關(guān)系,如圖5-116輸入中的一致,表示的含義是1 8是一個電阻,一個電阻兩端的網(wǎng)絡(luò)是同一個網(wǎng)絡(luò),以此類推,這個我們舉例添加的排阻有四個Xnet;

圖5-116 設(shè)置模型參數(shù)示意圖

第六步,添加完成以后,可以回到PCB界面,點擊查詢按鈕,可以查詢該網(wǎng)絡(luò),是否添加了Xnet,如圖5-117所示。

圖5-117 Xnet顯示示意圖

上述,就是在Allegro軟件中添加Xnet的方法解析,一般多用于帶有串阻串容的時序等長中。

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4362文章

23458瀏覽量

408253 -

allegro

+關(guān)注

關(guān)注

42文章

713瀏覽量

147211 -

無源器件

+關(guān)注

關(guān)注

5文章

220瀏覽量

23928

發(fā)布評論請先 登錄

Cadence SPB OrCAD Allegro24.1安裝包

解鎖未來汽車電子技術(shù):軟件定義車輛與區(qū)域架構(gòu)深度解析

Allegro Skill封裝功能之導(dǎo)出單個封裝介紹

Allegro Skill封裝功能之添加禁布區(qū)介紹

RZ MPU工業(yè)控制教程連載(62)Yocto系統(tǒng)添加程序

緩存技術(shù)在軟件開發(fā)中的應(yīng)用

必看!PCB幾層板設(shè)計的決定要素全解析

ZCAN PRO解析的DBC Singal 起始位與XNET解析的起始位不同;解析的信號不符合大端邏輯

AD20原理圖跟PCB怎么交互

ad中原理圖畫好如何生成pcb

Altium怎么把原理圖換成pcb

AD軟件如何生成PCB網(wǎng)表

pcb怎么改變焊盤大小

PCB電路板設(shè)計與制作的步驟和要點

Allegro X 23.11 版本更新 I PCB 設(shè)計:DFA_BOUND 用于 DFA 規(guī)則設(shè)定

PCB技術(shù):allegro軟件中添加xnet的步驟解析

PCB技術(shù):allegro軟件中添加xnet的步驟解析

評論