引言

近年發展速度迅猛的全彩色 LED顯示屏,具有大尺寸、高亮度、高清晰度、高對比度的顯示效果以及比傳統顯示技術大得多的顏色復現能力的特點,憑借這些優點使其在公眾多媒體顯示領域一枝獨秀。目前 LED顯示的單基色灰度級數已經達到 8192或更高,這就使其對信號源的質量要求更加嚴格。面對顯示面積不斷增大,顏色復現能力不斷增強的顯示終端,對高清晰度圖像的無損、實時傳輸系統提出了迫切需求。維持高畫質的視頻,最好的方法便是從來源裝置傳輸未壓縮的影音數據流。IEEE 1394等界面標準只能傳輸壓縮影音數據,因此可能會降低畫面品質。傳統的視頻接口已經難以滿足 LED顯示技術的需求。2002年 Sony, Hitachi, Thomson (RCA), Philips, Matsushi(Panasonic),Toshiba,Silicon Image 為數字高清電視(HDTV)與消費電子領域共同制定了下一代高清多媒體接口規范,并于 2002年12月 9日發布了 HDMI規范的 1.0版本。HDMI以 Silicon Image公司的高速數字 TMDS(Transition Minimized Differential Signaling) 技術,傳輸純數字內容, 不壓縮數據,無需轉換從而實現了最佳的畫面與音響效果。2006年7月更新發布了HDMI1.3版本, HDMI 1.3將其單鏈接帶寬提高到 340 MHz,其色深由舊版本 HDMI 規范的 8 位色深提升至 10 位、12和 16 位(RGB或 YCbCr),能夠以無沉淀細節完美呈現十多億種色彩。

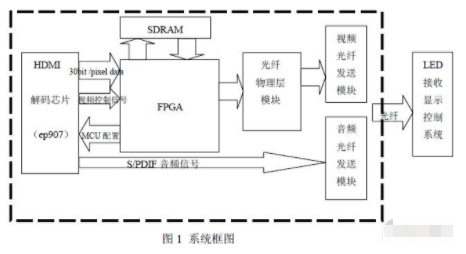

2系統硬件設計

本文設計傳輸分辨率為 720P(1280×720),刷新率為60HZ,30位 RGB色深的 HDMI數字信號,對信號解碼應用于 LED顯示系統中。設計框圖如下:

如上圖所示,系統采用光纖傳輸,這樣的設計有利于數字信號遠距離傳輸,以滿足 LED屏幕顯示的工程需要。整個系統分為視頻源解碼,FPGA與 SDRAM的數據交換,數據幀通過光纖發送模塊的發送。

3 系統各部分組成原理

3.1視頻源的解碼恢復

系統使用的 HDMI信號的解碼出 30bit的視頻信號,Hsync(行同步)、Vsync(場同步),DE(數使能信號)和 Pclk(像素時鐘)。對于需要進行分區掃描顯示的 LED顯示屏而言,一般只需接收芯片提供的Vsync、DE和 Pclk作為采集視頻數據的控制信號。跟據 Vsync來界定一場圖像的起始點,DE來確定每行數據的起始點,在 LED顯示屏內由 FPGA來完成整個顯示區域的掃描控制。系統選用的是 Explore公司生產EP907S,它是一款三端口輸出解碼芯片。支持 HDMI1.3a版本, 最高支持 36bitRGB色深表現,分辨率最支持 1080P(1920×1080),支持 8聲道的 IIS和 S/PDIF音頻格式傳輸,支持寬帶數字內容保護HDCP(High Bandwidth Digital Content Protection),內置 HDMI控制器簡化了外部 MCU控制。

FPGA采集 HDMI象素數據就是利用同步控制信號來進行,在 FPGA內部設計了一個 HDMI數據接收模塊,這個模塊由一個寫緩沖區和寫緩沖區寫控制器構成。寫緩沖區負責緩存采集的 30bit并行數據信號,然后以 60bit并行數據結構寫入至片外 SDRAM中,故稱為寫緩沖區,它是由 Altera公司的 FPGA中自帶 M4K塊通過臺 QuartusII設計平臺里面包含的 IP核配置成的,寫入數據為30bit,由寫時鐘進行操作,讀取數據為60bit,由讀時鐘進行操作;寫緩沖區寫控制器負責對寫緩沖區進行寫入控制,它將決定寫緩沖區何時開始寫操作,何時停止寫操作,寫入數據具體的寫入位置等,寫緩沖區寫控制器就是通過 HDMI同步控制信號來實現以上這些功能,在每個Vsync高電平脈沖到來的時候,寫緩沖區寫控制器就會將寫緩沖區的寫入地址清零,待 DE處于高電平狀態時,就將寫緩沖區寫使能信號置為有效開啟寫緩沖區的寫入功能,同時會以 Pclk為單位將寫緩沖區地址依次加“1”,DE處于低電平狀態時寫緩沖區寫使能信號變為無效寫緩沖區寫操作停止,此時以 Pclk為單位的寫地址產生操作也隨之停止。這樣在寫緩沖區寫控制器的控制下,寫緩沖區會及時將傳入的 30bit象素數據緩存,保證視頻數據的完整存儲.FPGA內部模塊圖 2所示:

3.2 片外存儲器

作為數據中轉站的片外存儲器,不僅用于簡單的數據存儲,更起到了調節平衡 FPGA發送端和接收端兩邊時鐘操作頻率的重要作用。以本文為例,HDMI發送1280×720@60Hz圖像

格式的視頻數據,根據象素時鐘 Pclk計算公式得出 Pclk=1280×720×60×(1+0.3)≈

71.8MHz,而每幀圖象的大小為 1280×720×30=2.4678Mbyte

為滿足系統要求,本文選用比較經濟的 SDRAM作為片外存儲器。具體為 SAMSUNG的 2片 K4S643232H-tc60,位寬為32bit,每片 SDRAM容量為8Mbyte。為實現實時圖象的連續傳輸,即在新的一幀寫入的同時上一幀也要同時讀出,這就要求內存的位寬為視頻格式像素寬度的兩倍,即 30bit ×2=60bit,本設計采用2 片32 位的 64Mbit SDRAM組合成 64位位寬的數據總線,這樣就有兩條物理上的數據和指令通道,滿足系統 60bit帶寬要求, 在實際操作中,進行大量連續數據讀操作時,雙通道可以同時工作。進行大量數據寫操作時,先寫第一片SDRAM的一行,然后在快要寫完該行數據的時候對第二片SDRAM 進行操作,將后面的數據寫入第二片 SDRAM中的同一行,這樣的效率將近是單片SDRAM 讀操作的兩倍。

雖然讀緩沖區控制器和寫緩沖區控制器分別處于不同的 FPGA模塊之中,但由于其控制的緩沖區均是由 FPGA嵌入式 RAM――M4K RAM通過 Quartus II硬件開發平臺自帶的 IP核配置成雙端口RAM的形式產生的,而且兩個緩沖區功能上是一樣的,因此相應的其控制器設計思路是一致的。圖 3為設計的寫緩沖區。

3.3 數據發送部分

整個 FPGA發送端的核心控制模塊是數據幀產生模塊。這里的數據幀不是一般意義的圖像幀,數據幀設計的提出涉及到以太網技術的一個術語――MAC(Medium Access Control,介質訪問控制子層協議)的概念。MAC層面向以太網物理層,主要用來對用戶數據進行打包、封裝并按照選定的數據接口時序要求進行數據傳輸。MAC層按照規定的封裝結構將數據打包形成一個個數據幀。根據 IEEE 802.3標準規定的標準以太網數據幀結構包括:前導碼(Preamble)、數據幀開始標識碼(Start Fream Delimite,SFD)、目標和源 MAC層地址(Destination/Source MAC Address)、數據長度/類型表示碼(Length/Type)、客戶端數據(MAC Client Data)、Pad碼以及幀檢查序列(Fream Check Sequence)共8個部分。

針對實時視頻傳輸特點,對數據幀結構的封裝結構做了重新設計,撤銷了對于本系統沒有實際意義的目標和源 MAC層地址、數據長度/類型表示碼、Pad碼和幀檢查序列,使得數據幀結構得到了極大的精簡,傳輸效率也明顯提高。精簡幀結構如下。

前導碼(Preamble)和數據幀開始標識碼(SDF)用于恢復數據鏈路與確定每個數據幀起始位置,在 Device id部分用戶可以自定義這一字節的具體含義,Sync Count記數值用于準確恢復同步信號,應注意保證記數溢處,本文選用 14bit可以保證數據不溢出,本文采用對幀計數的方式,一幅圖象由許多數據幀組成,定義一幅圖象的開始的一幀數據為0000H,當放送一幀的計數全為0 時,表示新的一幅圖象的開始。從而恢復圖象的幀同步信息。由于本文視頻源的數據格式為 30 bit ,所以定義數據塊格式為 360×30 bit。由于以太網幀結構中規定數據必須為字節的整數倍,固將數據轉換為450×24bit,即 5個字節存儲 4個單基色象素信息。以滿足物理層芯片的一個數據塊的長度不能超過 1536個字節的要求。幀間隙IPG是必須的,物理層芯片在期間處于 Idle狀態進行時鐘步。IEEE802.3規定 IPG其最小值為96個碼元時鐘,為了滿足要求。設計選定 120個時鐘碼元。

精簡的幀結構的效率為(320×30)/(16+8+10+14+360×30+4×30)=98.46%。提高了幀傳輸的效率。

FPGA發送端光纖物理層傳輸芯片――TLK2501具有 16bit并行數據總線寬度,最高

2.5Gbps的數據傳輸帶寬,內置 8B/10B的標準以太網編/解碼器。而系統需要的最大帶寬W=1280×720×60×30=1.65Gbit。可見物理層芯片可以滿足系統的要求。它通訊是由高速數據傳輸芯片控制模塊進行控制的,這個模塊可以按照用戶自定義實現對 TLK2501傳輸端所有運行模式的控制。24bit/16bit轉換器的負責將數據幀轉換成物理層信片所需數據格式。 在本文背景下,對于芯片的操作比較簡單,只是用到了它的最基本傳輸功能。在數據幀間隙期間,控制模塊置數據傳輸控制信號“TxEN(發送使能)=0,TxER(接收使能)=0”,數據接口TD[15:0]上任何信號均不會被放置在數據總線上,此時物理層傳輸芯片處于 IDLE狀態,用于芯片的時鐘同步;其余時間均為數據傳輸狀態,控制信號“TxEN=1,TxER=0”,數據接口TD[15:0]接收來自數據幀產生模塊的數據幀信號并輸出至物理層數據總線上。通過光纖發送模塊將數據發送到 LED接收控制端進行數據的恢復。

3.4音頻傳輸HDMI的一大特點就是在一根傳輸線中可以同時傳輸視頻和音頻信號。從 HDMI 規范

1.0開始,HDMI就定義了支持 Dolby Digital(包括 Dolby Digital EX)和 DTS(包括 DTS-ES)。HDMI 1.1 增加了支持 DVD-Audio 的功能,而 HDMI 1.2 增加了 SACD 功能。此外,HDMI(除 1.0 版外)都能夠傳輸 8 聲道192kHz、24 比特的無壓縮音頻,其效果優于其它所有消費音頻格式。因此,如果播放器能夠將音頻格式解碼為多聲道 PCM,那么就能夠以解碼 PCM 流的形式傳輸上述任何一種音頻格式。為了保證音頻數據完整傳輸,減少傳輸過程中信號的衰減,本文選用 S/PDIF音頻接口傳輸音頻信號。

S/PDIF是“SONY/PHILIPS Digital Interface Format”的縮寫,它是由 SONY與PHILIPS公司在上世紀 80年代制訂的一種數字音頻信號傳輸標準,可以傳輸 LPCM流和 DolbyDigital、DTS這類數字音頻信號。采用一根數碼線同時傳遞數據和時鐘,簡化了連接。音頻數據字長可以擴展到 24位。常用的 SPDIF接口有光纖和同軸接口兩種。

HDMI解碼芯片 EP907上具備 S/PDIF接口輸出,芯片內部完成 S/PDIF信號的編碼,簡化了外部配置,經編碼后的音頻信號被發送到光纖發送模塊,本文選區的模塊為TOSHIBA 的TOTX173,將電信號轉換為光信號通過光纖傳輸,發送到 LED屏幕的接收控制系統進行解碼。

3 總結

本文設計了一種基于HDMI的視頻傳輸系統。提高了 LED顯示所需視頻信號源的質量,音頻系統的加入,豐富了 LED屏幕的功能,考慮到 LED顯示技術的工程需要,采用光纖傳輸數據。減少在傳輸過程中信號的衰減,實現遠距離傳輸。

責任編輯:gt

-

led

+關注

關注

242文章

23808瀏覽量

673139 -

芯片

+關注

關注

459文章

52420瀏覽量

439564 -

分辨率

+關注

關注

2文章

1080瀏覽量

42590

發布評論請先 登錄

MS2109 HDMI轉USB 高清視頻傳輸方案

基于IPP庫的MPEG-4視頻傳輸系統設計

基于IP組播技術的視頻傳輸系統的設計與實現

基于Live555的視頻傳輸系統設計

基于HDMI的實時視頻/音頻傳輸系統設計

光纖HDMI線的音視頻傳輸優勢是什么

網絡解碼矩陣:醫院高清視頻傳輸的可靠保障

基于HDMI解碼芯片EP907實現視頻傳輸系統的設計

基于HDMI解碼芯片EP907實現視頻傳輸系統的設計

評論