之前做的一個(gè)超寬帶非均勻采樣系統(tǒng)中遇到的一些問(wèn)題,雖然本文所述方法并未實(shí)際用到并解決遇到的問(wèn)題,但也是給了很大的啟發(fā)和參考,所以今天專門整理出來(lái)作為備忘。

在高速信號(hào)處理時(shí)的時(shí)許約束不僅僅包括片內(nèi)時(shí)序約束,要想實(shí)現(xiàn)高速信號(hào)的有效傳輸就必須進(jìn)行片外靜態(tài)時(shí)序分析。本文作為在高速信號(hào)處理時(shí)信號(hào)輸入輸出的理論參考,之所以說(shuō)作為理論參考是因?yàn)橛捎诟咚傩盘?hào)處理,具體的一些參數(shù)無(wú)法實(shí)際計(jì)算出來(lái),只能在理論參考的方向進(jìn)行不斷嘗試。

對(duì)于建立時(shí)間和保持時(shí)間本文就不再過(guò)多敘述,可參考【FPGA】幾種時(shí)序問(wèn)題的常見(jiàn)解決方法-------3,可以說(shuō)在數(shù)字高速信號(hào)處理中最基本的概念就是建立時(shí)間和保持時(shí)間,而我們要做的就是解決亞穩(wěn)態(tài)問(wèn)題和傳輸穩(wěn)定問(wèn)題。

下面就IO口時(shí)序約束分析進(jìn)行原理性的討論,首先在分析時(shí)要考慮的時(shí)序范圍是信號(hào)的兩端(FPGA和另一端器件)、信號(hào)傳輸路徑,三部分,這三部分中信號(hào)傳輸路徑可以包括邏輯器件或者單純外部信號(hào)線路。先將FPGA的建立時(shí)間和保持時(shí)間按照觸發(fā)器的定義方式進(jìn)行一下定義:

(1) Tdin為從FPGA的IO口到FPGA內(nèi)部寄存器輸入端的延時(shí);

(2) Tclk為從FPGA的IO口到FPGA內(nèi)部寄存器時(shí)鐘端的延時(shí);

(3) Tus/Th為FPGA內(nèi)部寄存器的建立時(shí)間和保持時(shí)間;

(4) Tco為FPGA內(nèi)部寄存器傳輸時(shí)間;

(5) Tout為從FPGA寄存器輸出到IO口輸出的延時(shí);

FPGA的建立時(shí)間和保持時(shí)間可定義為:

(1) FPGA建立時(shí)間:FTsu = Tdin + Tsu – Tclk;

(2) FPGA保持時(shí)間:FTh = Th + Tclk - Tdin;

(3) FPGA數(shù)據(jù)傳輸時(shí)間:FTco = Tclk + Tco + Tout;

-----------------------------------------------進(jìn)行輸入的最大延遲和最小延遲-----------------------------------------------

有了上述的重新定義的參數(shù),就可以將FPGA和器件之間的時(shí)序分析按照內(nèi)部分析的模式來(lái)進(jìn)行分析了,對(duì)FPGA的IO口進(jìn)行輸入最大最小延時(shí)約束是為了讓FPGA設(shè)計(jì)工具能夠盡可能的優(yōu)化從輸入端口到第一級(jí)寄存器之間的路徑延遲,使其能夠保證系統(tǒng)時(shí)鐘可靠的采到從外部芯片到FPGA的信號(hào)。

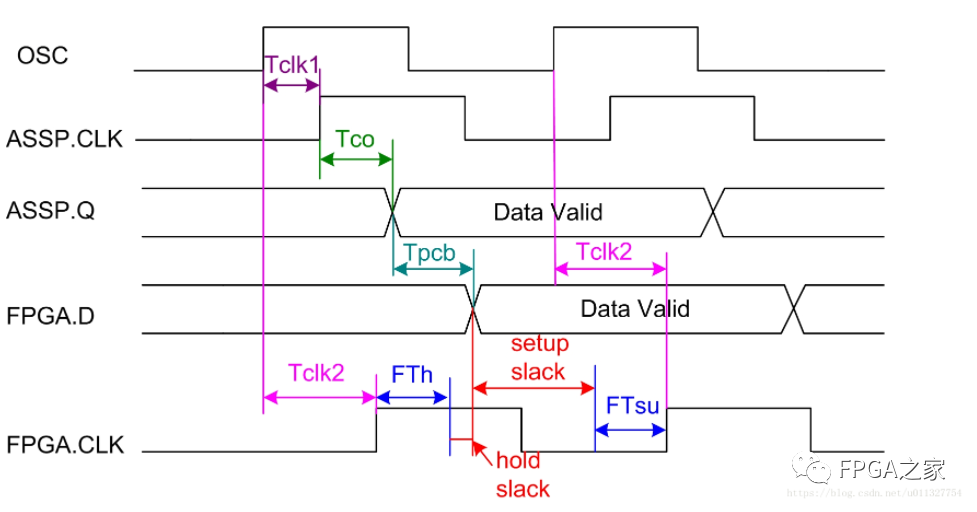

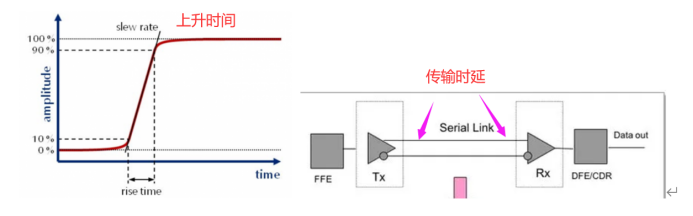

輸入延時(shí)即為從外部器件發(fā)出數(shù)據(jù)到FPGA輸入端口的延時(shí)時(shí)間。其中包括時(shí)鐘源到FPGA延時(shí)和到外部器件延時(shí)之差、經(jīng)過(guò)外部器件的數(shù)據(jù)發(fā)送Tco,再加上PCB板上的走線延時(shí)。如圖1.4所示,為外部器件和FPGA接口時(shí)序。

1,最大輸入延時(shí)

最大輸入延時(shí)(input delay max)為當(dāng)從數(shù)據(jù)發(fā)送時(shí)鐘沿(lanuch edge)經(jīng)過(guò)最大外部器件時(shí)鐘偏斜(Tclk1),最大的器件數(shù)據(jù)輸出延時(shí)(Tco),再加上最大的PCB走線延時(shí)(Tpcb),減去最小的FPGA時(shí)鐘偏移(FTsu)的情況下還能保證時(shí)序滿足的延時(shí)。這樣才能保證FPGA的建立時(shí)間,準(zhǔn)確采集到本次數(shù)據(jù)值,即為setup slack必須為正,計(jì)算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max) +Tco(max) +Tpcb(max) +FTsu)≥0

推出如下公式:

Tclk1(max) + Tco(max) + Tpcb(max) –Tclk2(min) ≤ Tclk - FTsu

PS:上式中max和min是為了保證傳輸質(zhì)量所必需的條件,如果不加max和min就會(huì)有可能導(dǎo)致系統(tǒng)有些情況不滿足上式,從而導(dǎo)致信號(hào)傳輸產(chǎn)生錯(cuò)誤。Tclk為同步時(shí)鐘的周期。

可以得出最大輸入時(shí)延表達(dá)式為上述不等式的左半部分而其最大值為上述不等式的右半部份,即:

最大輸入延時(shí)(input delay max) =Tclk - FTsu

歸根結(jié)底就是輸入信號(hào)的各部分時(shí)延必須滿足Tclk1(max) + Tco(max) + Tpcb(max) –Tclk2(min) ≤ Tclk - FTsu這個(gè)公式。但是式中Tco(max)可以通過(guò)對(duì)片外器件延時(shí)實(shí)現(xiàn)手動(dòng)調(diào)節(jié),Tclk2(min)也可以通過(guò)時(shí)許約束(offset)或者FPGA內(nèi)部DCM實(shí)現(xiàn)相移等操作。最大最小輸入延時(shí)指的是數(shù)據(jù)的最大輸入延時(shí),可通過(guò)始終約束其最大輸入延時(shí)來(lái)保證時(shí)序正確。

2,最小輸入延時(shí)

最小輸入延時(shí)(input delay min)為當(dāng)從數(shù)據(jù)發(fā)送時(shí)鐘沿(lanuch edge)經(jīng)過(guò)最小外部器件時(shí)鐘偏斜(Tclk1),最小器件數(shù)據(jù)輸出延時(shí)(Tco),再加上最小PCB走線延時(shí)(Tpcb),此時(shí)的時(shí)間總延時(shí)值一定要大于FPGA的最大時(shí)鐘延時(shí)和建立時(shí)間之和,這樣才能不破壞FPGA上一次數(shù)據(jù)的保持時(shí)間,即為hold slack必須為正,計(jì)算公式如下式所示:

Hold slack = (Tclk1(min) + Tco(min) + Tpcb(min))–(FTh + Tclk2(max))≥ 0

推出如下公式:

Tclk1(min) + Tco(min) + Tpcb(min) – Tclk2(max) ≥ FTh

可以得出最大輸入時(shí)延表達(dá)式為上述不等式的左半部分而其最大值為上述不等式的右半部份,即:

最小輸入延時(shí)(input delay min) = FTh

歸根結(jié)底就是輸入信號(hào)的各部分時(shí)延必須滿足Tclk1(min) + Tco(min) + Tpcb(min) – Tclk2(max) ≥ FTh這個(gè)公式。但是式中Tco(max)可以通過(guò)對(duì)片外器件延時(shí)實(shí)現(xiàn)手動(dòng)調(diào)節(jié),Tclk2(min)也可以通過(guò)時(shí)許約束(offset)或者FPGA內(nèi)部DCM實(shí)現(xiàn)相移等操作。外部器件輸出數(shù)據(jù)通過(guò)PCB板到達(dá)FPGA端口的最大值和最小值Tpcb,PCB延時(shí)經(jīng)驗(yàn)值為600mil/ns,1mm = 39.37mil。

-----------------------------------------------------------------------------------------------------

本文所述為高速信號(hào)處理時(shí),片間信號(hào)傳輸?shù)撵o態(tài)時(shí)許分析,中間的很多參數(shù)需要查看數(shù)據(jù)手冊(cè),另外對(duì)于FPGA輸出的靜態(tài)時(shí)許分析大家可以參考FPGA輸入的靜態(tài)時(shí)序分析進(jìn)行對(duì)照分析,在此就不再贅述。

原文標(biāo)題:【FPGA】高速信號(hào)處理中的片外信號(hào)輸入輸出靜態(tài)時(shí)序分析

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1645文章

22028瀏覽量

617721 -

信號(hào)

+關(guān)注

關(guān)注

11文章

2851瀏覽量

78193

原文標(biāo)題:【FPGA】高速信號(hào)處理中的片外信號(hào)輸入輸出靜態(tài)時(shí)序分析

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

泰克示波器MSO64如何應(yīng)對(duì)高速信號(hào)分析

高速信號(hào)如何判定?常見(jiàn)的高速信號(hào)有哪些?

深度解析:PCB高速信號(hào)傳輸中的阻抗匹配與信號(hào)完整性

差分信號(hào)線的選擇與處理

PCB板厚度對(duì)信號(hào)傳輸的影響

pcie布線對(duì)信號(hào)傳輸的影響

高速信號(hào)測(cè)試知識(shí)分享

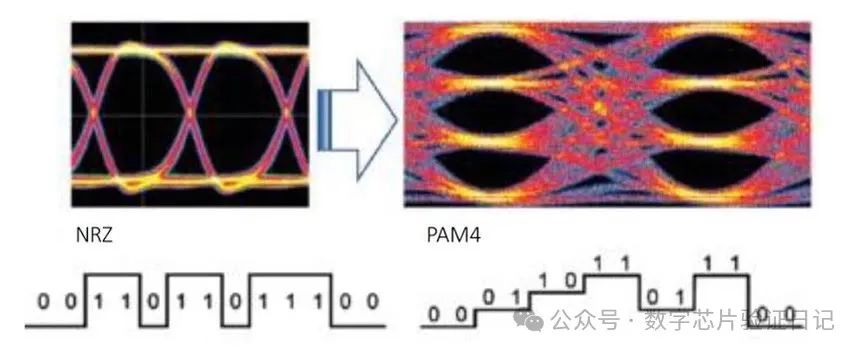

高速信號(hào)眼圖怎么看

高速電路設(shè)計(jì)與信號(hào)完整性分析

高速PCB信號(hào)完整性分析及應(yīng)用

高速PCB信號(hào)完整性分析及硬件系統(tǒng)設(shè)計(jì)中的應(yīng)用

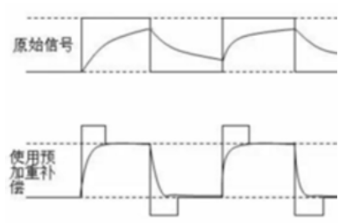

高速信號(hào)的預(yù)加重和去加重仿真分析

高速信號(hào)的定義和仿真驗(yàn)證分析

高速信號(hào)處理時(shí)片間信號(hào)傳輸?shù)撵o態(tài)時(shí)許分析

高速信號(hào)處理時(shí)片間信號(hào)傳輸?shù)撵o態(tài)時(shí)許分析

評(píng)論