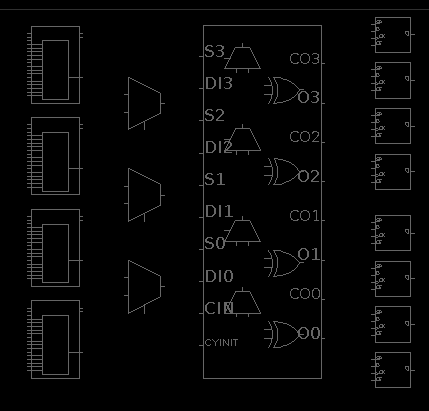

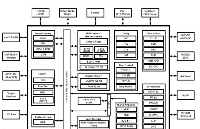

FPGA 的全稱(chēng)為Field Programmable Gate Array(現(xiàn)場(chǎng)可編程門(mén)陣列),屬于專(zhuān)用集成電路中的一種半定制電路,是可編程的邏輯陣列。FPGA 的基本結(jié)構(gòu)包括可編程輸入輸出單元、基本可編程邏輯單元、數(shù)字時(shí)鐘管理模塊、嵌入式塊RAM、豐富的布線資源、內(nèi)嵌專(zhuān)用硬核,以及底層內(nèi)嵌功能單元。

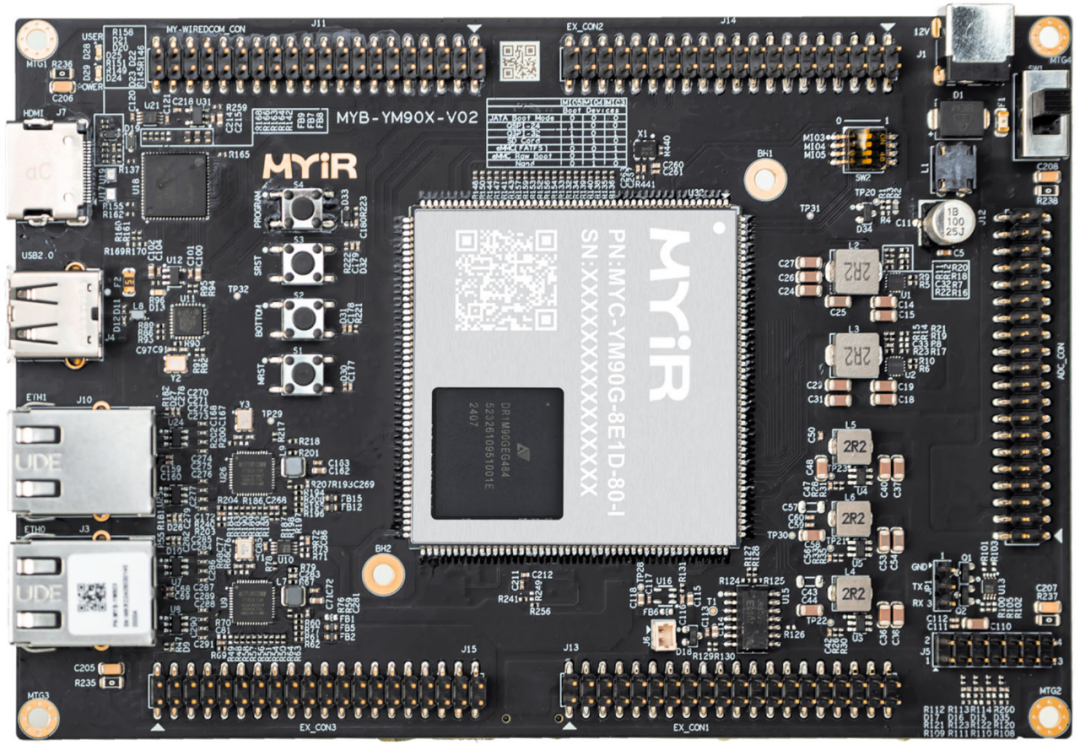

圖1 某FPGA的基本邏輯單元 市售常見(jiàn)的基于FPGA的平臺(tái)產(chǎn)品包括FPGA開(kāi)發(fā)板、FPGA原型驗(yàn)證系統(tǒng)。既然他們同樣都是基于FPGA芯片設(shè)計(jì)的,為什么規(guī)模、功能、成本和價(jià)格上有非常大的差異?這要從它們應(yīng)用場(chǎng)景和設(shè)計(jì)目標(biāo)的區(qū)別說(shuō)起:

FPGA開(kāi)發(fā)板:

FPGA開(kāi)發(fā)板的主要場(chǎng)景是“開(kāi)發(fā)基于獨(dú)立FPGA芯片的IP或應(yīng)用系統(tǒng)”,其設(shè)計(jì)目標(biāo)是精簡(jiǎn)化、高性能、低成本,并自帶合適的外設(shè)接口,對(duì)調(diào)試功能的要求限于在單顆FPGA上用原廠軟件調(diào)試。

因此其搭載的FPGA芯片通常的容量為小到中等規(guī)模,實(shí)際應(yīng)用中,往往用于進(jìn)行中小規(guī)模、特定協(xié)議功能芯片的開(kāi)發(fā),比如涉及以太網(wǎng)、MIPI、NVME/M.2 SSD控制、UART/I2C 控制、HDMI/DVI顯示控制等。也有直接把一塊FPGA開(kāi)發(fā)板放在一個(gè)大型系統(tǒng)之中,起到控制板的作用,這樣用戶可以靈活地對(duì)控制信號(hào)做各種調(diào)整。也有一些應(yīng)用場(chǎng)景計(jì)算算法用較大容量的FPGA實(shí)現(xiàn),達(dá)到高性能和算法靈活性的應(yīng)用目標(biāo)。同時(shí),由于中低端的開(kāi)發(fā)板售價(jià)適中,F(xiàn)PGA開(kāi)發(fā)板也適合初學(xué)者進(jìn)行學(xué)習(xí)使用。

其次,部分FPGA開(kāi)發(fā)板也被用在IP和小型芯片設(shè)計(jì)的開(kāi)發(fā)驗(yàn)證場(chǎng)景。這部分開(kāi)發(fā)板配備大容量的FPGA芯片,甚至是單板配備多片F(xiàn)PGA芯片來(lái)適應(yīng)開(kāi)發(fā)驗(yàn)證場(chǎng)景,一般由用戶自己負(fù)責(zé)手工實(shí)現(xiàn)從設(shè)計(jì)到FPGA功能原型的流程。

FPGA原型驗(yàn)證系統(tǒng):

FPGA原型驗(yàn)證系統(tǒng)的主要應(yīng)用場(chǎng)景是“芯片設(shè)計(jì)過(guò)程中搭建軟硬件一體的系統(tǒng)驗(yàn)證環(huán)境”:一是芯片流片回來(lái)前為軟件團(tuán)隊(duì)提供調(diào)試驅(qū)動(dòng)軟件的平臺(tái),加速芯片上市時(shí)間;二是作為芯片仿真驗(yàn)證的一個(gè)補(bǔ)充,因?yàn)镕PGA可以接真實(shí)的硬件子卡,跟仿真使用的軟件模型有一定差別,有一定機(jī)會(huì)發(fā)現(xiàn)隱蔽的bug ;此外FPGA相對(duì)軟件仿真以及Emulator速度快,比較適合一些耗時(shí)較多的大場(chǎng)景case。故在芯片設(shè)計(jì)越來(lái)越大的情況下,其設(shè)計(jì)目標(biāo)是能使用多顆FPGA芯片快速實(shí)現(xiàn)高性能的全系統(tǒng)驗(yàn)證原型,并支持該場(chǎng)景下的調(diào)試需求。

首先,它搭載的往往是較大容量和多片的FPGA芯片,如Xilinx VU440/VU19P, Intel 的Stratix 10等,那么它就非常適合進(jìn)行復(fù)雜算法、CPU/GPU類(lèi)型芯片的驗(yàn)證和實(shí)現(xiàn):比如人工智能,多核RISC-V處理器IP等開(kāi)發(fā)環(huán)境;如果是SoC芯片或大型IP的開(kāi)發(fā),那么可以將FPGA系統(tǒng)經(jīng)過(guò)互聯(lián)擴(kuò)展容量后,進(jìn)行驗(yàn)證。

其次,F(xiàn)PGA原型驗(yàn)證系統(tǒng)更重要的目標(biāo),是從硬件和軟件上支持大型芯片功能原型的各項(xiàng)要求。如低延遲并行IO接口、高帶寬Serdes接口、自動(dòng)化設(shè)計(jì)分割到多片F(xiàn)PGA并優(yōu)化性能、多片F(xiàn)PGA的信號(hào)調(diào)試、原型系統(tǒng)規(guī)模的任意縮放、各種軟硬件接口擴(kuò)展方案,等等。這些目標(biāo)決定了原型驗(yàn)證系統(tǒng)需要更專(zhuān)門(mén)的設(shè)計(jì),特別是配套的自動(dòng)化工具,因?yàn)閷?duì)兩三片F(xiàn)PGA以上的中大型設(shè)計(jì),手工實(shí)現(xiàn)設(shè)計(jì)分割和優(yōu)化的投入太大,設(shè)計(jì)團(tuán)隊(duì)更需要自動(dòng)化工具。

區(qū)分了FPGA開(kāi)發(fā)板和FPGA 原型驗(yàn)證系統(tǒng)平臺(tái)的應(yīng)用場(chǎng)景和設(shè)計(jì)目標(biāo),我們就明白它們?yōu)槭裁磿?huì)有如此大的差異,本質(zhì)上就是基于設(shè)計(jì)目標(biāo)的功能取舍。下面我們分別介紹一下這2種產(chǎn)品和它們的關(guān)鍵點(diǎn):

FPGA開(kāi)發(fā)板

我們就先從FPGA開(kāi)發(fā)板說(shuō)起。為了實(shí)現(xiàn)基于FPGA芯片的開(kāi)發(fā)、測(cè)試、應(yīng)用,我們需要再為它加上一系列的外圍電路及元件,這樣FPGA才能夠正常地上電、配置、加載運(yùn)行程序、提供相應(yīng)的外設(shè)接口及長(zhǎng)時(shí)間保持穩(wěn)定的工作狀態(tài)。以目前最簡(jiǎn)單的實(shí)現(xiàn)方式來(lái)看,這就是FPGA開(kāi)發(fā)板。前文提到它的主要場(chǎng)景是為FPGA芯片的直接應(yīng)用而做開(kāi)發(fā),因此這類(lèi)產(chǎn)品的設(shè)計(jì)重點(diǎn)也在于盡量接近目標(biāo)應(yīng)用系統(tǒng)。

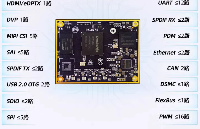

圖2 Xilinx公司出品的Zynq系列FPGA開(kāi)發(fā)板 首先,從外觀上看,單顆FPGA開(kāi)發(fā)板尺寸可以做到很小,通常不會(huì)超過(guò)一張A4紙的大小,方便擺放和移動(dòng)。上面布局FPGA 主芯片、電源處理芯片、外部接口部件、電容電阻等分立元件。Xilinx、Intel、Lattice等FPGA原廠都推出過(guò)各種各樣的開(kāi)發(fā)板。其中不光有傳統(tǒng)范疇的FPGA功能開(kāi)發(fā)板,也有采取ARM核 + FPGA架構(gòu)的SoC解決方案,如Xilinx Zynq、Intel Arria10等等。ARM接口資源豐富、功耗低,擅長(zhǎng)進(jìn)行多媒體顯示、邏輯控制;而FPGA擅長(zhǎng)進(jìn)行多通道或高速AD采集、接口拓展,以及高速信號(hào)傳輸?shù)取烧呦嗷ソY(jié)合,可滿足各種工業(yè)現(xiàn)場(chǎng)應(yīng)用場(chǎng)景。 其次,從硬件架構(gòu)上,因?yàn)橐话阕詭Я撕芏喑S猛庠O(shè)接口,而且以單顆芯片的應(yīng)用為主,所以FPGA開(kāi)發(fā)板對(duì)互聯(lián)和擴(kuò)展的要求不高,有時(shí)會(huì)在板上有多顆FPGA芯片互連,但通常不考慮多板之間的高速連接需求,畢竟太大規(guī)模的邏輯設(shè)計(jì)要用到多顆FPGA,運(yùn)行性能和調(diào)試能力會(huì)受很大影響。 在軟件方面,用戶主要依靠FPGA廠商提供的一體化軟件(如Xilinx公司的Vivado,Intel公司的Quartus,Lattice公司的Diamond等)來(lái)實(shí)現(xiàn)FPGA工程的綜合及布局布線。當(dāng)然,也有一些實(shí)力技術(shù)雄厚的第三方廠商提供了不錯(cuò)的綜合工具(如Synplify, Precision等),先由設(shè)計(jì)源代碼得到網(wǎng)表,再交由原廠軟件進(jìn)行布局布線。但以上這些工具都不支持多片F(xiàn)PGA場(chǎng)景,因此FPGA開(kāi)發(fā)板用于超過(guò)單片F(xiàn)PGA容量的芯片設(shè)計(jì)或IP驗(yàn)證時(shí),都只能由用戶自己手工做設(shè)計(jì)分割,這需要解決很多時(shí)鐘、資源、性能、調(diào)試的問(wèn)題,對(duì)工程師要求高,投入時(shí)間多。 從市面上的FPGA開(kāi)發(fā)板銷(xiāo)售情況來(lái)看,目前一些國(guó)產(chǎn)廠商占有的份額也很高。他們提供的開(kāi)發(fā)板往往配置了中低端的FPGA芯片(包括有國(guó)產(chǎn)及進(jìn)口的),并自行設(shè)計(jì)/制造PCB板。配套豐富的學(xué)習(xí)資料,同時(shí)在板上集成了常用的接口模塊,如Flash、HDMI、DDR4,PCIe等;加之這些開(kāi)發(fā)板的售價(jià)并不昂貴,一般從幾百元到幾千元人民幣不等,適合大專(zhuān)院校和自學(xué)的人群購(gòu)買(mǎi)使用。

FPGA原型平臺(tái)

隨著目前集成電路的不斷發(fā)展,設(shè)計(jì)規(guī)模的大型化,單顆FPGA板在容量上就顯得捉襟見(jiàn)肘,已經(jīng)無(wú)法滿足設(shè)計(jì)需求。首先,以目前國(guó)內(nèi)頭部的CPU、GPU設(shè)計(jì)公司的設(shè)計(jì)規(guī)模,單顆IC芯片的設(shè)計(jì)體量,需要占用到幾十顆Xilinx VU440級(jí)別FPGA的情況,已屢見(jiàn)不鮮。 在這種背景之下,F(xiàn)PGA系統(tǒng)供應(yīng)廠商開(kāi)始著手研究多顆FPGA的系統(tǒng)解決方案。其中就包括在單塊的PCB板上裝配多顆FPGA及多個(gè)FPGA系統(tǒng)之間進(jìn)行互聯(lián)。 經(jīng)過(guò)一段時(shí)間的發(fā)展和探索,F(xiàn)PGA原型驗(yàn)證平臺(tái)產(chǎn)品應(yīng)運(yùn)而生。之所以經(jīng)常稱(chēng)之為“平臺(tái)”或“系統(tǒng)”,首先在硬件結(jié)構(gòu)上比單板形式的FPGA開(kāi)發(fā)板復(fù)雜很多,其次FPGA芯片廠商提供的軟件工具無(wú)法支持這么復(fù)雜的多片F(xiàn)PGA實(shí)現(xiàn),需要配套專(zhuān)業(yè)的FPGA原型實(shí)現(xiàn)相關(guān)軟件工具。 一套優(yōu)秀的FPGA原型驗(yàn)證系統(tǒng),應(yīng)該具有以下產(chǎn)品特性:

基于模塊化的設(shè)計(jì)/可伸縮的驗(yàn)證平臺(tái)規(guī)模

在保證一定的高速仿真性能的前提下提供驗(yàn)證完整性

提供從軟件早期開(kāi)發(fā)到系統(tǒng)級(jí)驗(yàn)證的解決方案

提供從綜合、自動(dòng)模塊分割 、布局布線、FPGA bit產(chǎn)生、下載,以及在線/離線Debug的整套流程

提供豐富的調(diào)測(cè)手段,幫助用戶快速定位問(wèn)題,易于Bring Up

提供豐富的接口子板和外部真實(shí)設(shè)備相連

提供軟件接口與外部軟件通訊

提供豐富的IO接口,以及高速Serdes接口用于partition互連以及外設(shè)子卡的互連

如本文開(kāi)頭所述,復(fù)雜算法、CPU/GPU類(lèi)型芯片的驗(yàn)證和實(shí)現(xiàn)都是適合在FPGA原型驗(yàn)證系統(tǒng)上進(jìn)行的。不過(guò),由于芯片規(guī)模的日益大型化,單顆的系統(tǒng)往往已經(jīng)無(wú)法容納下一個(gè)大型的IP/SoC了。 這個(gè)時(shí)候我們需要把多個(gè)原型系統(tǒng)進(jìn)行互聯(lián),把分割后的邏輯下載到所有的系統(tǒng)當(dāng)中,這樣來(lái)進(jìn)行整個(gè)設(shè)計(jì)的驗(yàn)證和調(diào)試工作。那么以目前的Partition互聯(lián)技術(shù)手段看,主要分為單端IO、差分LVDS IO和高速Serdes IO (如Xilinx的GTH )互聯(lián)的方式。 Serdes IO互聯(lián)可以達(dá)到很高的帶寬(Bandwidth),但根據(jù)收發(fā)器內(nèi)部信號(hào)寬度和傳輸協(xié)議的不同,加上串并轉(zhuǎn)換和Encoder/Decoder的時(shí)間開(kāi)銷(xiāo),會(huì)產(chǎn)生幾十到幾百ns的額外延遲,可能影響分布于多顆FPGA芯片上的系統(tǒng)原型性能;而單端IO的延遲一般就在ns級(jí)別,故其分割后的系統(tǒng)性能會(huì)更高,但這對(duì)并行單端IO信號(hào)連接器的設(shè)計(jì)提出了很高的要求,目前包括Synopsys以及芯華章少數(shù)FPGA原型平臺(tái)能夠達(dá)到1.4Gbps的較高速率。 在實(shí)際原型系統(tǒng)的核心設(shè)計(jì)分割中,單端IO連接器用得更多一些,在連接獨(dú)立的高速外設(shè)和接口時(shí),Serdes高速連接器用得更多一些。這類(lèi)高速互聯(lián)接口及其線纜的成本都很高,但對(duì)于原型系統(tǒng)的設(shè)計(jì)目的來(lái)說(shuō)是必須的,這也是為什么FPGA原型系統(tǒng)的價(jià)格要遠(yuǎn)遠(yuǎn)高于FPGA開(kāi)發(fā)板的原因之一。 說(shuō)完了硬件方面,再看軟件方面,如果用到了多顆的FPGA系統(tǒng),那么對(duì)于大設(shè)計(jì)的分割問(wèn)題變得十分重要。對(duì)于一個(gè)大設(shè)計(jì),軟件可以自動(dòng)或者手動(dòng)的把邏輯分割到幾片F(xiàn)PGA當(dāng)中,根據(jù)連線資源情況插入TDM(時(shí)分復(fù)用)的IP,再對(duì)分割后的邏輯進(jìn)行時(shí)序優(yōu)化;軟件能夠保留頂層的端口信號(hào)名稱(chēng)。從調(diào)試方面考慮,需要探及設(shè)計(jì)的內(nèi)部的信號(hào)。 隨著設(shè)計(jì)規(guī)模增大,除了軟件運(yùn)行速度之外,綜合階段進(jìn)行Timing Driven Synthesis優(yōu)化的動(dòng)作,以實(shí)現(xiàn)冗余邏輯的優(yōu)化和時(shí)序上的提升,因此軟件的算法優(yōu)化顯得十分重要。從性能指標(biāo)上看,主要是分割的功能正確性、邏輯和時(shí)序的優(yōu)化度及Timing-driven減少hop提升編譯性能。利用分布式技術(shù),減少設(shè)計(jì)規(guī)模對(duì)CPU時(shí)間和內(nèi)存造成的影響。 目前,各大原型驗(yàn)證平臺(tái)供應(yīng)商都在軟件上加大了投入。一款擁有出色的FPGA原型軟件工具應(yīng)具備以下的特點(diǎn):

綜合時(shí)進(jìn)行專(zhuān)門(mén)的時(shí)序驅(qū)動(dòng)優(yōu)化

綜合階段充分利用并行化手段降低設(shè)計(jì)規(guī)模對(duì)綜合時(shí)間造成的影響,盡量?jī)?yōu)化網(wǎng)表的時(shí)序和面積

算法優(yōu)化、能夠?qū)崿F(xiàn)大數(shù)量的FPGA自動(dòng)分割且配置簡(jiǎn)便綜合工具與分割工具配合保留內(nèi)部信號(hào)名稱(chēng),并與綜合工具配合映射信號(hào)名稱(chēng),支持RTL源代碼調(diào)試

自動(dòng)產(chǎn)生時(shí)鐘并處理時(shí)鐘的分割,對(duì)于數(shù)片至數(shù)十片F(xiàn)PGA的大型設(shè)計(jì)實(shí)現(xiàn)很重要

最大程度保留原來(lái)代碼設(shè)計(jì)層次,提高增量編譯度和可調(diào)試性,分割前后功能保持一致

服務(wù)器軟件時(shí)內(nèi)存資源控制得當(dāng)

保證分割結(jié)果正確的情況下,耗時(shí)短

這樣的配套軟件,能夠一體化地完成綜合及分割步驟,將為整個(gè)原型驗(yàn)證系統(tǒng)大大加分。隨著設(shè)計(jì)規(guī)模的日益增長(zhǎng),用戶對(duì)軟件的綜合/分割功能十分注重;軟件功能出色,無(wú)疑能對(duì)硬件系統(tǒng)的銷(xiāo)售產(chǎn)生極大的促進(jìn);反之,硬件系統(tǒng)做的很大,軟件的功能跟不上,甚至要依賴外部的綜合或分割工具,無(wú)疑為整套系統(tǒng)拖了后腿,無(wú)法實(shí)現(xiàn)上述的關(guān)鍵功能。

總 結(jié)

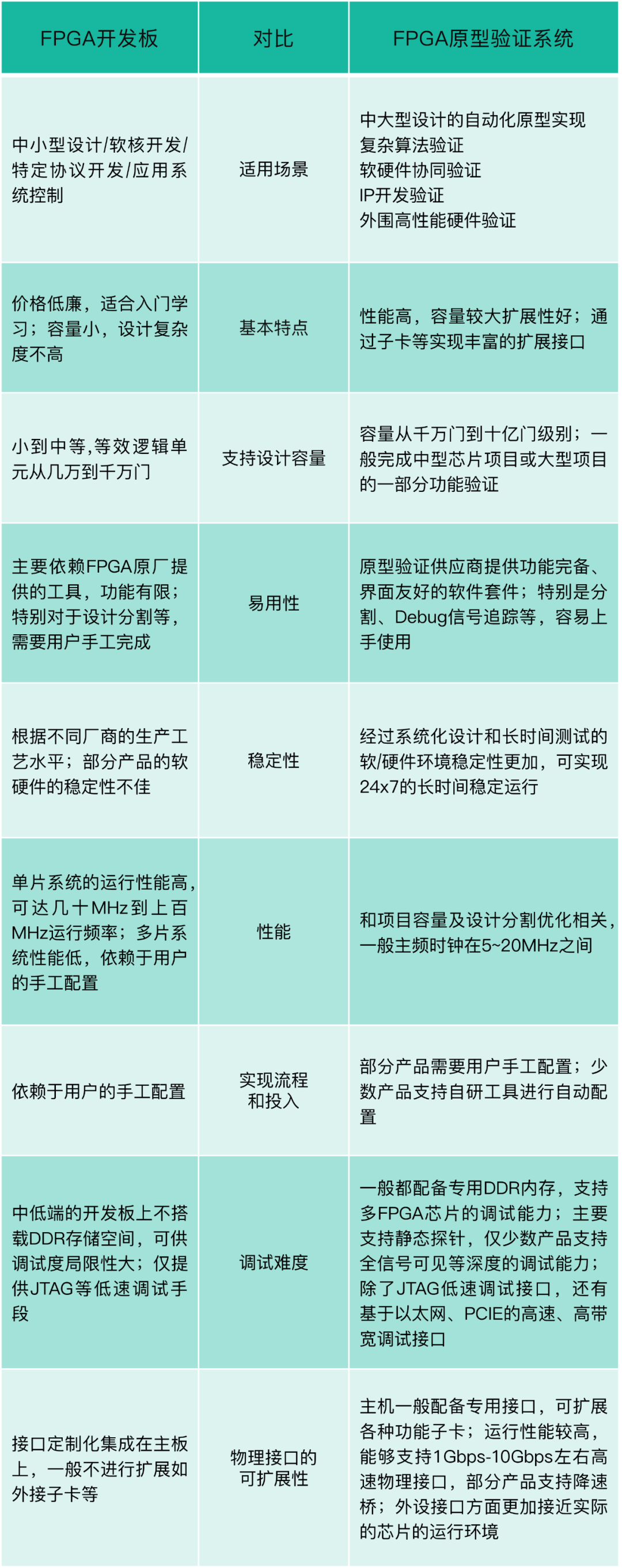

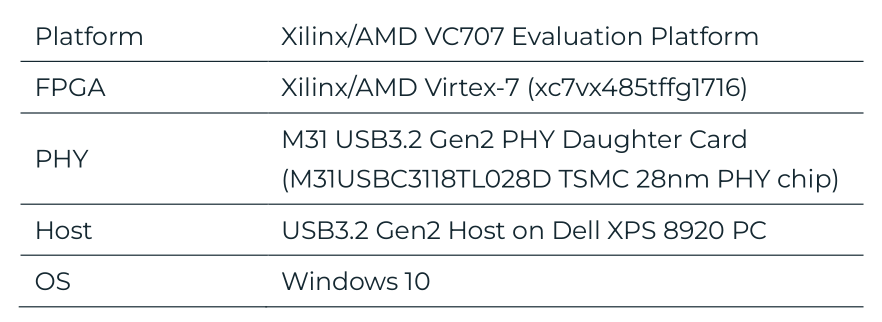

綜上所述,我們?cè)賮?lái)看一下FPGA開(kāi)發(fā)板、FPGA原型驗(yàn)證系統(tǒng)之間的對(duì)比表格:

圖3FPGA開(kāi)發(fā)板、FPGA原型驗(yàn)證系統(tǒng)之間的對(duì)比表格

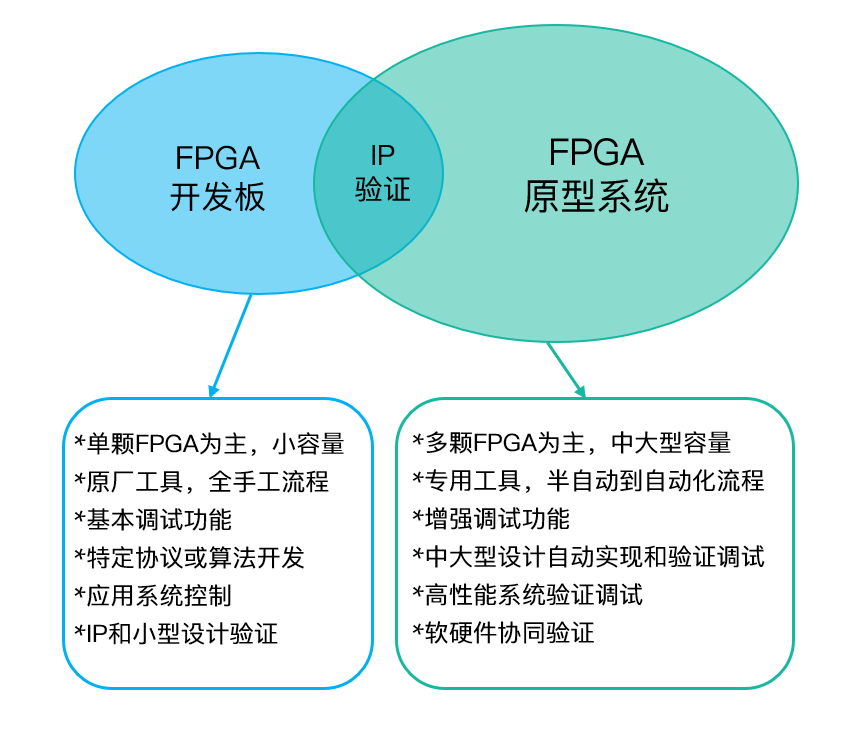

下面的圖例便于讀者更容易的理解它們二者之間的關(guān)系:

圖4 FPGA開(kāi)發(fā)板和原型系統(tǒng)應(yīng)用上的交集圖示 從應(yīng)用場(chǎng)景上看,我們看到,F(xiàn)PGA開(kāi)發(fā)板適合小型設(shè)計(jì)的手工驗(yàn)證、特定協(xié)議的開(kāi)發(fā),及在整個(gè)系統(tǒng)中起到控制的作用等等;而FPGA原型系統(tǒng)適合中大型設(shè)計(jì)和復(fù)雜算法的自動(dòng)化驗(yàn)證及連接真實(shí)外圍硬件的高性能系統(tǒng)驗(yàn)證/調(diào)試,軟硬件協(xié)同調(diào)試等等。在IP驗(yàn)證方面,F(xiàn)PGA開(kāi)發(fā)板和原型系統(tǒng)有一定的重合度。 以上就是關(guān)于FPGA開(kāi)發(fā)板和原型驗(yàn)證系統(tǒng)這2種不同的數(shù)字設(shè)計(jì)驗(yàn)證平臺(tái)的對(duì)比介紹,謝謝!

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1645文章

22033瀏覽量

617730 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

5656瀏覽量

104246

原文標(biāo)題:FPGA開(kāi)發(fā)板vs原型驗(yàn)證系統(tǒng)

文章出處:【微信號(hào):X-EPIC,微信公眾號(hào):芯華章科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

西門(mén)子桌面級(jí)原型驗(yàn)證系統(tǒng)Veloce proFPGA介紹

有ARM,NPU,FPGA三種核心的開(kāi)發(fā)板 — 米爾安路飛龍派開(kāi)發(fā)板

第二章 開(kāi)發(fā)板與芯片介紹 詳解W55MH32芯片及開(kāi)發(fā)板

發(fā)布|CAE1200+FPGA開(kāi)發(fā)板

瑞芯微主板/開(kāi)發(fā)板Linux系統(tǒng)播放音頻方法,觸覺(jué)智能RK3562開(kāi)發(fā)板演示

【迅為電子】i.MX6UL和i.MX6ULL芯片區(qū)別與開(kāi)發(fā)板對(duì)比

正點(diǎn)原子fpga開(kāi)發(fā)板不同型號(hào)

正點(diǎn)原子和野火開(kāi)發(fā)板哪個(gè)好

ARM開(kāi)發(fā)板與FPGA的結(jié)合應(yīng)用

盤(pán)古22K開(kāi)發(fā)板

數(shù)字芯片設(shè)計(jì)驗(yàn)證經(jīng)驗(yàn)分享文章 實(shí)際案例說(shuō)明用基于FPGA的原型來(lái)測(cè)試、驗(yàn)證和確認(rèn)IP——如何做到魚(yú)與熊掌兼

快速部署原型驗(yàn)證:從子卡到調(diào)試的全方位優(yōu)化

關(guān)于FPGA開(kāi)發(fā)板和原型驗(yàn)證系統(tǒng)對(duì)比介紹

關(guān)于FPGA開(kāi)發(fā)板和原型驗(yàn)證系統(tǒng)對(duì)比介紹

評(píng)論