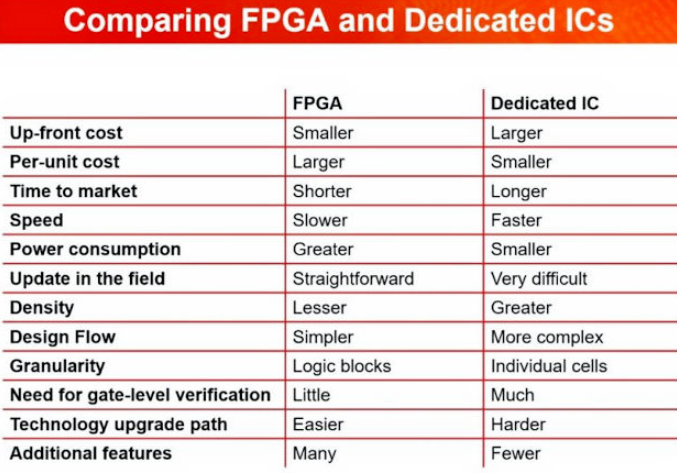

土耳其伊斯坦布爾 ElectraIC 總經(jīng)理兼管理合伙人 Ates Berna 曾經(jīng)在 LinkedIn 上發(fā)布了一份總結(jié)比較圖表,展示了 FPGA 和 ASIC 之間的差異。

雖然這不是一個詳細(xì)的圖表,但我認(rèn)為它是一個很好的破冰船,當(dāng)你需要一個相當(dāng)復(fù)雜的高性能、非標(biāo)準(zhǔn) IC 來解決設(shè)計挑戰(zhàn)時,它會導(dǎo)致關(guān)于你在 FPGA 和 ASIC 之間做出的選擇。

我經(jīng)常收到 FPGA 與 ASIC 的問題,我認(rèn)為討論 Berna 發(fā)布的圖表很有價值。因此,這里對圖表中的項目進行了更詳細(xì)的逐行討論:

這是我對這張圖表的逐行討論:

預(yù)付費:ASIC 的前期成本很高。首先,ASIC 開發(fā)工具的成本。您需要一個相當(dāng)大的工具鏈來開發(fā) ASIC,您必須租用或購買,并且您需要知道如何使用這些工具。如果您的設(shè)計團隊沒有這些知識,您需要將培訓(xùn)團隊的成本包括在您的前期成本清單中。此外,您將產(chǎn)生相當(dāng)大的 NRE(非經(jīng)常性工程)費用,大約為數(shù)十萬或數(shù)百萬美元,您將支付給硅代工廠以構(gòu)建您的 ASIC。NRE 費用用于支付掩模制造和檢查,在代工廠繁忙的制造計劃中預(yù)留一個位置來制造您的 ASIC、芯片測試和分揀、封裝和最終測試。相比之下,F(xiàn)PGA 是現(xiàn)成的部件,因此沒有代工 NRE 費用,F(xiàn)PGA 工具比 ASIC 設(shè)計工具便宜得多,大概低三個數(shù)量級。根據(jù) FPGA 的不同,您甚至可以通過分銷方式購買零件并在第二天獲得。

單位成本:這就是 ASIC 大放異彩的地方。因為您通常設(shè)計 ASIC 以滿足您的確切設(shè)計要求,所以您只購買您真正想要的硅片。很少或沒有浪費。因此,假設(shè)您有預(yù)計的產(chǎn)品銷量來證明創(chuàng)建 ASIC 的合理性,那么 ASIC 的單位成本應(yīng)該低于 FPGA。這是因為 FPGA 的芯片開銷很大。首先,您的設(shè)計可能無法 100% 使用任何給定的 FPGA。如果幸運的話,您可能會獲得 90% 的利用率。通常,您可能無法使用多達 10% 或更多的 FPGA 資源來滿足可布線性和時序目標(biāo),因為布線擁塞太大,并且如果您嘗試使用整個 FPGA,信號會變得太長和太慢。此外,F(xiàn)PGA 上的信號路由矩陣非常豐富,以確保您可以在 FPGA 上路由您的設(shè)計。

上市時間:到目前為止,F(xiàn)PGA 是上市時間的領(lǐng)先者。如果您已準(zhǔn)備好制造 pcb,則可以在 FPGA 設(shè)計完成的同一天發(fā)貨。您需要做的就是將最終配置閃存到板上的 EEPROM 中,對其進行測試、封裝并發(fā)貨。相反,當(dāng)您完成 ASIC 設(shè)計時,您會將設(shè)計運送到硅代工廠并舉行流片派對。然后,您等待幾個月,而代工廠會接受您的設(shè)計、檢查、制造芯片、測試芯片、封裝芯片,然后將封裝好的 ASIC 寄回給您。當(dāng)您收到完成的 ASIC 盒時,您可以構(gòu)建和測試您的電路板。同時,來自競爭對手的類似產(chǎn)品,但基于 FPGA,在您等待從代工廠取回 ASIC 的那幾個月里,將一直在您的市場上銷售。如果上市時間對您來說至關(guān)重要,那么 FPGA 可能是您的最佳選擇。

速度:假設(shè)您的設(shè)計人員知道他們在做什么,ASIC 從任何給定的 IC 工藝節(jié)點中提取最高性能。由于 FPGA 的大型(電容式)可編程路由矩陣,相對于 ASIC 的性能,任何給定的 IC 工藝節(jié)點的性能都會損失大約一個數(shù)量級。

能量消耗:這并不明顯,但 FPGA 在單位成本和速度方面的硅效率低下也增加了 FPGA 相對于 ASIC 的功耗。FPGA 上的所有這些額外的路由矩陣晶體管都會泄漏,從而導(dǎo)致更高的靜態(tài)功耗。由于有序 FPGA 中所需的曼哈頓布線,F(xiàn)PGA 中固有的較長布線會為每條布線增加電容,從而導(dǎo)致更高的動態(tài)功耗。但是,F(xiàn)PGA 供應(yīng)商可以反擊其 FPGA 中的額外功耗。

例如,萊迪思半導(dǎo)體為其 Nexus FPGA 選擇了 28nm FDSOI 工藝技術(shù),以降低靜態(tài)功耗。有很多這樣的設(shè)計技巧可以降低功耗,但是 FPGA 有大芯片,大芯片有很多電容,

現(xiàn)場更新:這是一個容易理解的。基于 SRAM 的 FPGA 很容易在現(xiàn)場重新編程。更改存儲在閃存中的配置并更新您的設(shè)計。在 FPGA 設(shè)計的早期,您必須從其 IC 插座中拔出舊配置的 EPROM 或 EEPROM,然后插入一個新配置來執(zhí)行現(xiàn)場更新。如今,您很可能通過 USB 或 JTAG 端口進行可重編程設(shè)計。一些最終產(chǎn)品設(shè)計允許無線更新,盡管允許無線硬件更新存在許多安全問題。

相反,更新 ASIC 通常需要換板(在無線行業(yè)中稱為上門服務(wù))。一些 ASIC 設(shè)計結(jié)合了來自 eFPGA 供應(yīng)商(如 Achronix、Flex Logix、Menta 或 QuickLogic)的嵌入式 FPGA (eFPGA) 結(jié)構(gòu),以實現(xiàn)有限數(shù)量的現(xiàn)場更新而無需上門服務(wù)。如果您想采用這種方法,您甚至可以獲得名為 OpenFPGA 的開源 FPGA 結(jié)構(gòu)生成器和工具集。但是,如果您在 ASIC 中嵌入 FPGA 架構(gòu),那么 ASIC 就變成了 FPGA,不是嗎?

密度:因為器件密度與單位成本密切相關(guān),所以同樣適用 FPGA 與 ASIC 的論點,只是增加了一點。在任何給定的工藝技術(shù)中,由于 FPGA 的路由開銷和資源利用限制,您總是可以設(shè)計一個更大的設(shè)備,一個具有更多資源的 ASIC,如上所述。

設(shè)計流程:與 ASIC 不同,F(xiàn)PGA 的物理設(shè)計在您看到設(shè)備之前已經(jīng)為您完成并由 FPGA 供應(yīng)商驗證,盡管有勘誤表。您通常會使用一個供應(yīng)商的工具鏈來設(shè)計 FPGA 配置,盡管一些富有的設(shè)計公司使用來自三大 EDA 供應(yīng)商之一的 ASIC 級布局布線工具:Cadence、Siemens/Mentor 和 Synopsys。對于 ASIC 設(shè)計,您通常會采用混合搭配的方法,從三大 EDA 公司購買 EDA 工具,也許還從尚未被三大 EDA 公司之一吸收的新 EDA 初創(chuàng)公司購買一些額外的設(shè)計工具。

粒度:ASIC 的數(shù)字粒度是一個門,或者在某些情況下是一個晶體管。FPGA 必須具有更粗的粒度,大約為一個邏輯單元。否則,F(xiàn)PGA 的布線開銷將變得完全不切實際。ASIC 和 FPGA 之間的這種粒度差異導(dǎo)致 FPGA 更高的單位成本和相對缺乏密度。

需要門級驗證:FPGA 和 ASIC 一樣需要設(shè)計級驗證。但是,F(xiàn)PGA 在門級不是細(xì)粒度的,因此它們不需要門級驗證。您將每個門都放置在 ASIC 設(shè)計中,因此您需要驗證每個門。

技術(shù)升級路徑:理論上,在一個 FPGA 供應(yīng)商的產(chǎn)品線中從一個 FPGA 系列升級到下一個系列會更容易。例如,通過三個 Xilinx 7 系列器件遷移設(shè)計相對容易:Artix、Kintex 和 Virtex。然而,遷移到其他供應(yīng)商的 FPGA 也意味著遷移到其他 FPGA 供應(yīng)商的設(shè)計工具,這并不是特別容易,盡管它并不像某些人可能認(rèn)為的那么困難。工程師們已經(jīng)設(shè)法掌握了不止一個 FPGA 供應(yīng)商的工具鏈。他們只是在進行更改時抱怨很多。ASIC 沒有技術(shù)升級路徑。要升級 ASIC,您需要設(shè)計、驗證和制造新的 ASIC。

附加功能:在這里,我必須與上面的圖表不同。盡管 FPGA 供應(yīng)商長期以來一直在尋找附加功能塊以添加到他們的 FPGA 中,但 FPGA 上可用的幾乎任何東西都可以作為 IP 設(shè)計或購買并放置在 ASIC 上。這可能并不容易,但通常是可能的。關(guān)于 ASIC IP 的聲明包括嵌入式 FPGA IP。也許該圖表旨在表明更容易利用 FPGA 供應(yīng)商塞進其部件中的許多其他前沿特性。例如,F(xiàn)PGA 供應(yīng)商在過去 20 年一直引領(lǐng)著高速 SerDes 設(shè)計。如果您想要一個快速的 SerDes,您可能會在 FPGA 供應(yīng)商的最新設(shè)備上找到最快的,尤其是 Achronix、Intel 和 Xilinx。

當(dāng)然還有很多其他的設(shè)計考慮沒有出現(xiàn)在上面的圖表中。例如,在 FPGA 和 ASIC 之間有一個中間步驟——結(jié)構(gòu)化 ASIC——與 ASIC 相比,它以更低的 NRE 成本提供了 ASIC 的許多(但不是全部)優(yōu)勢。十五年前,許多公司提供結(jié)構(gòu)化 ASIC,并建議它們是下一代門陣列。由于許多商業(yè)原因,僅剩下一家商業(yè)結(jié)構(gòu)化 ASIC 供應(yīng)商——英特爾——它在 2018 年收購了最后一家結(jié)構(gòu)化 ASIC 供應(yīng)商 eASIC。

盡管觸發(fā)本文的圖表并不全面,但它確實為在 FPGA 和 ASIC 之間做出決定提供了一個很好的起點。到目前為止,這篇文章應(yīng)該已經(jīng)戳到了某人的痛處,所以請隨時發(fā)表評論,讓我們知道您的想法。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22020瀏覽量

617161 -

asic

+關(guān)注

關(guān)注

34文章

1245瀏覽量

122237

發(fā)布評論請先 登錄

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

ASIC和GPU的原理和優(yōu)勢

大多數(shù)FPGA的程序存儲器(FLASH)為什么都放在外面呢?FPGA的主要應(yīng)用

FPGA與ASIC的區(qū)別 FPGA性能優(yōu)化技巧

ASIC集成電路與FPGA的區(qū)別

FPGA和ASIC在大模型推理加速中的應(yīng)用

FPGA與ASIC的優(yōu)缺點比較

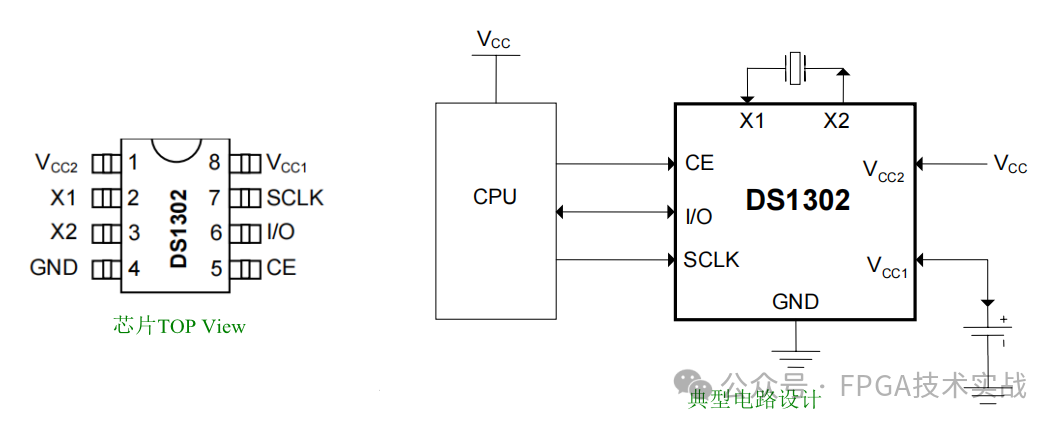

DS1302芯片與FPGA之間SPI通信原理

FPGA做深度學(xué)習(xí)能走多遠?

如何在兩種類型的SOT663封裝之間進行協(xié)同布局

如何在SOT-563封裝和SOT-236封裝之間實現(xiàn)共同布局

為低功耗FPGA、處理器和ASIC實施啟用LVDS鏈路

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰(zhàn)的任務(wù)!

如何在FPGA中實現(xiàn)隨機數(shù)發(fā)生器

如何在FPGA和ASIC之間做選擇

如何在FPGA和ASIC之間做選擇

評論