1. 概述

1)PCIe(Peripheral Component Interconnect Express)是繼ISA和PCI總線之后的第三代I/O總線。一般翻譯為周邊設(shè)備高速連接標(biāo)準(zhǔn)。

2)PCIe協(xié)議是一種端對端的互連協(xié)議,提供了高速傳輸帶寬的解決方案。目前PCIe已經(jīng)發(fā)展到第四代PCIe4.0, 每一代的發(fā)展,最明顯的特征就是速率翻倍。

3)是Intel公司1991年推出的。批準(zhǔn)組織:PCI SIG (PCI興趣小組)

4)一個x16插槽可以運行x1、x2、x4、x8、x16的卡

2. PCIe 布線規(guī)則

從金手指邊緣到PCIe芯片管腳的走線長度應(yīng)限制在4英寸(約100MM)以內(nèi)。

PCIe的PERP/N,PETP/N,PECKP/N是三個差分對線,注意保護(hù)(差分對之間的距離、差分對和所有非PCIe信號的距離是20MIL,以減少有害串?dāng)_的影響和電磁干擾(EMI)的影響。芯片及PCIe信號線反面避免高頻信號線,最好全GND)。

差分對中2條走線的長度差最多5MIL。2條走線的每一部分都要求長度匹配。差分線的線寬7MIL,差分對中2條走線的間距是7MIL。

當(dāng)PCIe信號對走線換層時,應(yīng)在靠近信號對過孔處放置地信號過孔,每對信號建議置1到3個地信號過孔。PCIE差分對采用25/14的過孔,并且兩個過孔必須放置的相互對稱。

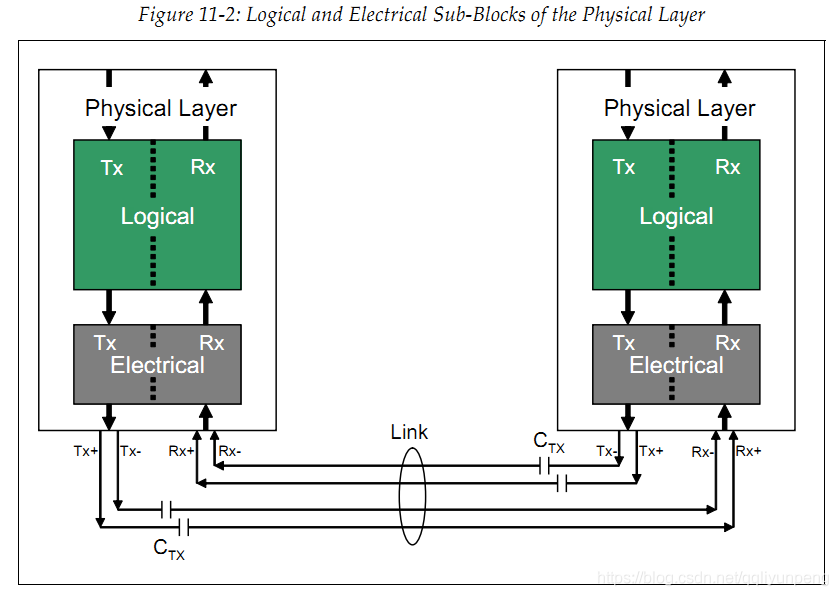

PCIe需要在發(fā)射端和接收端之間交流耦合,差分對的兩個交流耦合電容必須有相同的封裝尺寸,位置要對稱且要擺放在靠近金手指這邊,電容值推薦為0.1uF。

SCL等信號線不能穿越PCIe主芯片。

3. PCIe 分類、速度

按lane( 車道 --》 通道 )的個數(shù)分有 x1 x2 x4 x8 x16 (最大可支持32個通道)

按代來分 有 gen1 gen2 gen3 gen4 gen5

速度:

PCIe 與 PCI 之間的區(qū)別

速度上

PCI的工作頻率分為33MHz和66MHz,最大吞吐率 266MB/s

PCIe如3中描述,PCIe 1.0 x1 的吞吐率就達(dá)到了250MB/s

傳輸方式上

PCI 是并行數(shù)據(jù)傳輸,一次傳輸4字節(jié)/8字節(jié),半雙工

PCIe是串行數(shù)據(jù)傳輸,全雙工

硬件上

傳輸PCI信號的是普通電平

傳輸PCIe信號的是差分電平

鏈路上

PCI是總線的連接方式

PCIe是點對點的連接方式

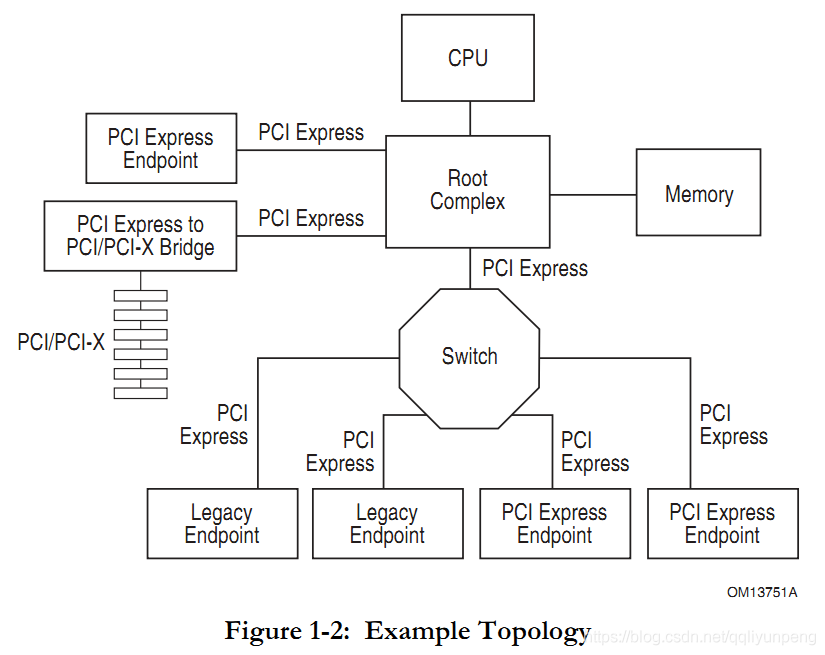

點對點拓?fù)涫鞘裁礃拥模?/p>

PCIe的物理連接方式:

5. 編碼方式介紹

PCIe gen1 和 PCIe gen2 采用的編解碼方式是 8b/10b,PCIe gen3 和 之后的 采用的是 128b/130b 的編碼方式。

8b/10b 意思是說,當(dāng)我們要傳輸8b的數(shù)據(jù)時,實際在通道上傳輸?shù)氖?0b的數(shù)據(jù),解碼的時候,我們希望得到的是8b的有效數(shù)據(jù)。這樣,相當(dāng)于有效的帶寬是實際帶寬的 80%。

同理128b/130b,是傳輸128bit數(shù)據(jù)實際線路中傳輸?shù)氖?30bit數(shù)據(jù)。

速率圖中的單位間的關(guān)系:

傳輸速率單位 GT/s,表示 千兆傳輸/秒,是實際每秒傳輸?shù)奈粩?shù),他不包括額外吞吐量的開銷位。

兩個例子:

PCIe gen1 x1 傳輸速率 2.5GT/s = 2500MT/s = ( 2500 / 10 ) MB/s

PCIe gen3 x1 傳輸速率 8GT/s = 8000MT/s = ( 8000 / 130 ) x ( 128/8 ) MB/s= 984.6153.。. MB/s

6. inbound 和 outbound

在PCIe設(shè)備和系統(tǒng)內(nèi)存互相訪問時,outbound是指CPU到設(shè)備方向;inbound指Device--》 RC(CPU端)方向。從這個概念上說,設(shè)備(device)都是外部的,沒有內(nèi)部設(shè)備之說。CPU讀寫RC 端的寄存器時,還是屬于片上系統(tǒng)的范圍,所以既不是inbound 也不是outbound。

7. PCI 配置空間

PCI設(shè)備擁有256B的配置空間,PCIe還提供另外4KB的擴(kuò)展,這256B的配置空間中前64B是規(guī)范了的,其他的字節(jié)是各個廠商自己定義的。

7.1 PCI 設(shè)備的地址組成

① 總線號 --- 廠家ID

② 設(shè)備號 --- 設(shè)備ID

③ 功能號 --- 設(shè)備類

查看PCI設(shè)備的工具是 lspci

使用工具 lspci 查找 ①②③

》lspci

上邊輸出的每行開頭邏輯地址(XX:YY.Z)分別表示①②③,

其中一個PCI域能容納 256 個總線,

每個總線可以支持 32 個PCI設(shè)備,

每個PCI設(shè)備可容納 8 個PCI功能

》 lspci -t (以樹狀結(jié)構(gòu)顯示)

》 lspci -x (打印出配置空間前64字節(jié)的內(nèi)容)

》 lspci -s (指定哪個)

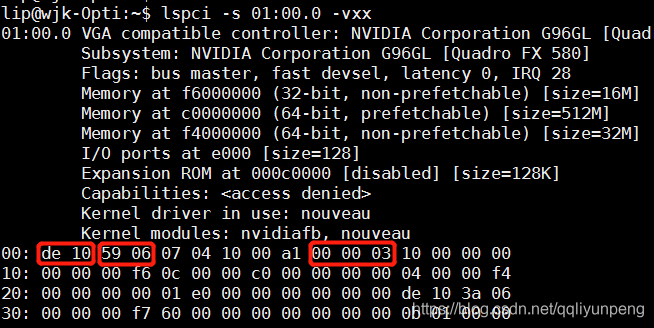

挑選一個 VGA compatible controller,如下

》 lspci -s 01:00.0 -vxx

字節(jié)序是小端格式,

[ 0 - 1 ] 表示的是廠家 ID,上圖的是 0x10de

[ 2 - 3 ] 表示的是設(shè)備 ID,上圖的是 0x0659

[ 9 - 11 ] 表示的是設(shè)備類型代碼,上圖的是 0x030000

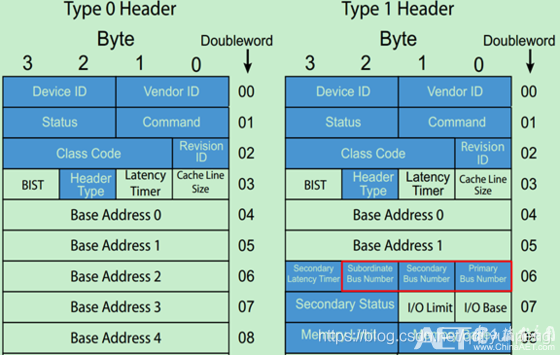

[14]表示的是設(shè)備類型,00表示普通端點設(shè)備;01表示Bridge設(shè)備;02表示CardBus bridges

使用命令查詢PCI設(shè)備的廠商號和設(shè)備號

》 lspci -n -s 01:00.0

列出格式 【設(shè)備類型:廠商ID:設(shè)備ID】

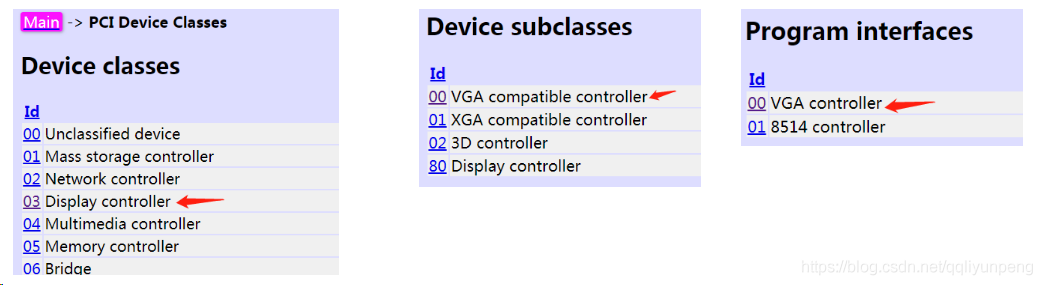

設(shè)備類型介紹:

設(shè)備類型可以在 http://pci-ids.ucw.cz/read/PD 網(wǎng)站進(jìn)行查詢,包括 classes、subclasses、Program interfaces 三部分,上圖中的設(shè)備類型是 030000依次對應(yīng)下圖,03是 Device classes,00是Device subclasses,00是Program interfaces

7.2 基地址/BAR

BAR0: 0XF6000000

BAR1: 0XC000000C

。..。

BAR5:0X0000E001

有6個BAR空間,每個BAR記錄了該設(shè)備映射的一段地址空間,為了區(qū)分 IO空間和 IO內(nèi)存,分開描述如下:

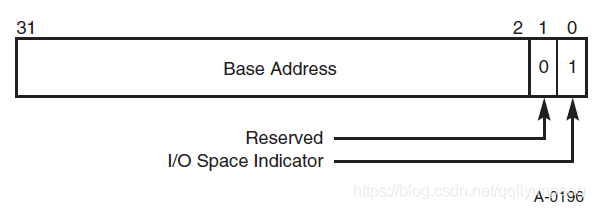

當(dāng)BAR的最后一位為0,如下圖,表示這是映射的IO內(nèi)存,1-2位表示內(nèi)存的類型,00=任意32位地址,01=少于1M,10=任意64位地址,11保留。bit1為1表示區(qū)間大小超過1M,為0表示不超過1M。bit3表示是否支持可預(yù)取。

如上例子中,BAR0是 映射的IO內(nèi)存,32位地址,不超過1M,不支持預(yù)取。

BAR1(最后幾位0110)也是映射的IO內(nèi)存,64位地址,區(qū)間大小超過1M,不支持預(yù)取。

當(dāng)BAR的最后一位為1,如下圖,表示這是映射的IO地址空間。上邊例子中的BAR5(最后一位是1)是映射的是IO地址空間,基地址是 0x0000e

中斷

由配置空間的IRQ Pin決定是否支持中斷,1表示支持,0表示不支持,加入支持,IRQ Line是中斷號。

上邊的例子中支持中斷號,中斷號是0x0b

訪問PCI

PCI設(shè)備包含3個尋址空間:配置空間、I/O端口 和 設(shè)備內(nèi)存。

驅(qū)動中操作 PCI 的配置區(qū)(上邊討論的64B的空間)

pci_read_config_[byte|word|dword](struct pci_dev *pdev, int offset, int *value);

pci_write_config_[byte|word|dword](struct pci_dev *pdev, int offset, int value);

offset, 想訪問的配置空間中字節(jié)位置

value, 對read函數(shù)來說,用于存放讀回來的數(shù)據(jù)

對write函數(shù)來說,是要寫進(jìn)去的值(這個int.。..。)

驅(qū)動中操作 I/O和內(nèi)存

I/O區(qū)域包含寄存器,內(nèi)存區(qū)域存放數(shù)據(jù)。

驅(qū)動中操作 PCI 的I/O和內(nèi)存

unsigned long pci_resource = pci_resource_[start|len|end|flags] (struct pci_dev *pdev, int bar);

start, 區(qū)域的基地址

bar, 取值 0 - 5

8. PCIe 的配置空間

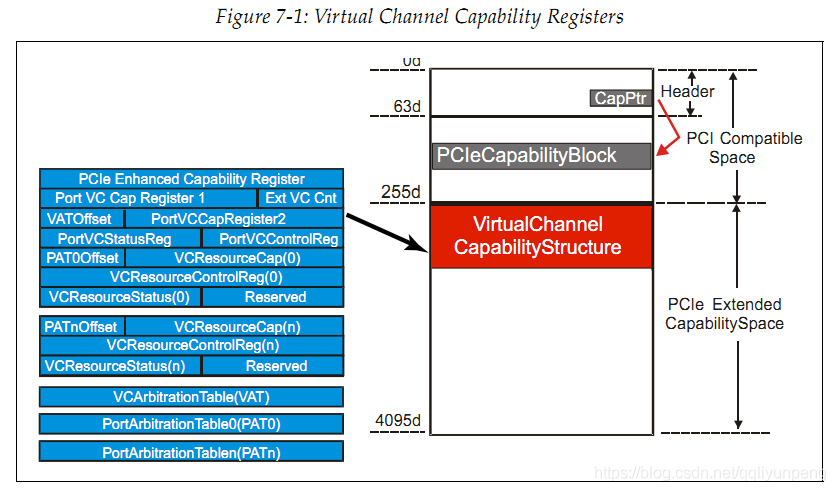

PCI的配置空間是256字節(jié),即 0x00~0xFF,而PCIe的配置空間是4k字節(jié),即 0x00~0xFFF。

PCIe 一共支持 256條bus,32個dev,8個fun。同PCI是一樣的。共需要內(nèi)存大小= 4k * 256 *32*8 = 256K Bytes = 256M,這個256M的內(nèi)存空間是為PCIe設(shè)備準(zhǔn)備的空間系統(tǒng)不可用。

PCIe設(shè)備發(fā)展向前兼容PCI,每個設(shè)備的配置空間的前256個Byte是PCI空間,后(4k-256)個Byte的空間是PCIe擴(kuò)展空間

Root和Switch的每一個端口中都包含一個P2P橋,橋的配置空間是Type1型

每個Type1型的Header中都包含最后一級總線號(Subordinate Bus Number)、下一級總線號(Secondary Bus Number)和上一級總線號(Primary Bus Number)等信息。當(dāng)配置請求進(jìn)行BDF路由的時候,正是依靠這些信息來確定要找的設(shè)備的。

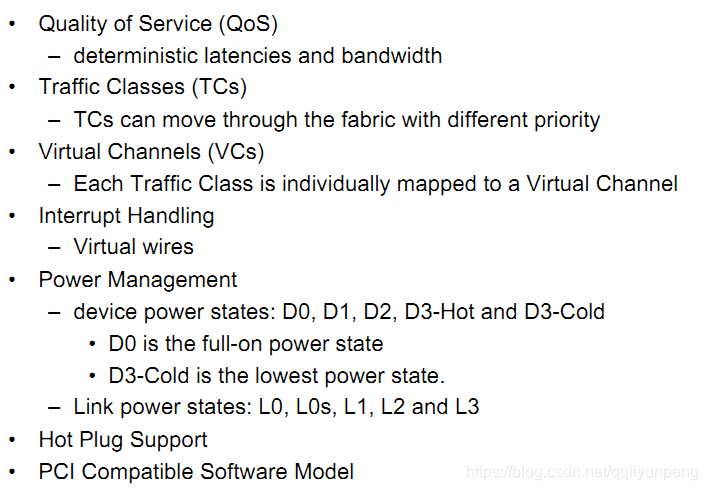

9. PCIe 屬性

服務(wù)質(zhì)量(Qos)

決斷振幅和帶寬

10. FAQ

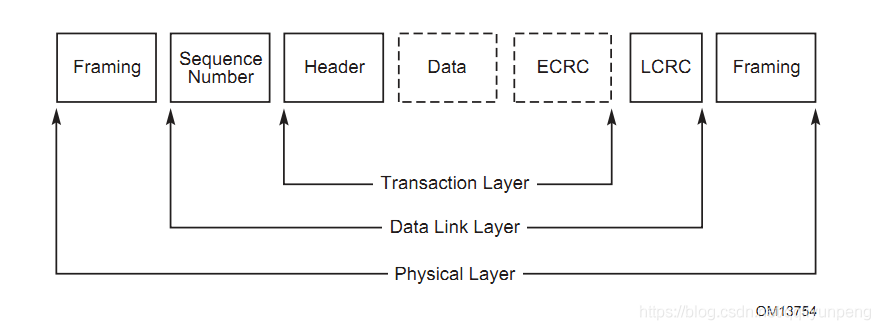

TLP 和 DLLP 是什么?

TCP 是 事務(wù)層包的簡寫,結(jié)構(gòu)下圖

Capability是什么?

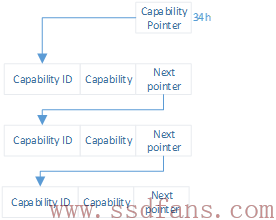

Capability是device通過在4k Byte的Configuration Space里告訴host它支持哪些特性的,而Capability又大致分為基本的Capability與之后擴(kuò)展的Capability,在使用4K的配置空間時兩者大同小異,都是采用鏈表形式來自定義Capability的位置的,唯一的區(qū)別是后者種類多,且不同廠商所支持的Capability有很大區(qū)別。如下圖為Configuration Space的基本架構(gòu)——0-3Fh(PCI Head域),40h-FFh(基本Capability區(qū)域),100-FFF(擴(kuò)展Capability區(qū)域)。

基本的Capability

Capability point是在0-3Fh(PCI Head域),偏移為34h,用于存放第一個Capability的偏移量,偏移量的范圍是40h-FFh(基本Capability區(qū)域),這段區(qū)間可任意讓你分配各種基本Capability。

擴(kuò)展的Capability

第一個擴(kuò)展Capability默認(rèn)就從100h的偏移位置開始放置,而不是像基本的Capability那樣從34h通過指針指過來。

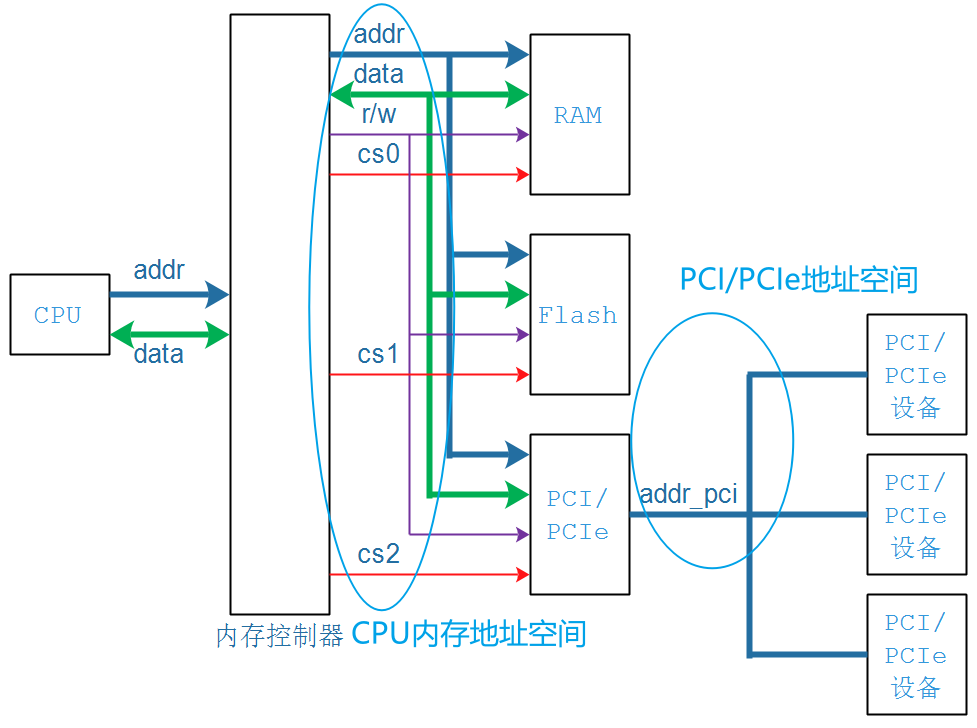

PCI總線空間與處理器空間隔離

PCI設(shè)備具有獨立的地址空間,即PCI總線地址空間,該空間與存儲器地址空間通過HOST主橋隔離。處理器需要通過HOST主橋才能訪問PCI設(shè)備,而PCI設(shè)備需要通過HOST主橋才能訪問主存儲器。

處理器訪問PCI設(shè)備時,必須通過HOST主橋進(jìn)行地址轉(zhuǎn)換,反過來也是。HOST主橋的一個重要作用就是將處理器訪問的存儲器地址轉(zhuǎn)換成PCI總線地址。

原文標(biāo)題:FPGA學(xué)習(xí)-PCIe基礎(chǔ)知識

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

芯片

+關(guān)注

關(guān)注

459文章

52308瀏覽量

437927 -

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

2009瀏覽量

65819 -

PCI

+關(guān)注

關(guān)注

5文章

678瀏覽量

131608 -

PCIe

+關(guān)注

關(guān)注

16文章

1329瀏覽量

84839

原文標(biāo)題:FPGA學(xué)習(xí)-PCIe基礎(chǔ)知識

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PCIE板設(shè)計規(guī)則--PCI Express Board Design Guidelines

國外PCIE的書籍《pci express system architecture》

zc706板和主機(jī)PC之間的PCI Express如何進(jìn)行通信

求分享關(guān)于PCI和PCIE轉(zhuǎn)串口的芯片

從PCI、PCI-X到PCI-Express之間的連接

pcie和pci插槽有什么區(qū)別

由PCI-SIG發(fā)布的PCIe板卡結(jié)構(gòu)規(guī)范

理解PCI和PCIE的關(guān)鍵

PCIe與PCI之間的區(qū)別

PCIe與PCI之間的區(qū)別

評論