1. 簡介

Quick bootloader 是一個用于快速制作bootloader的組件。

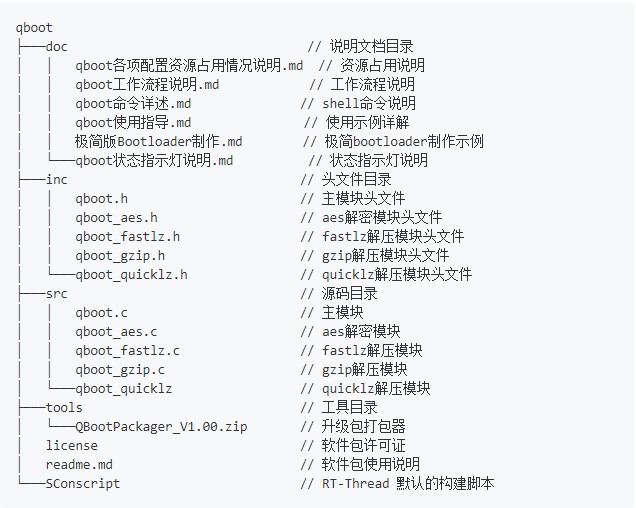

1.1 目錄結構

Quick bootloader 軟件包目錄結構如下所示:

1.2 許可證

Quick bootloader 遵循 LGPLv2.1 許可,詳見 LICENSE 文件。

1.3 依賴

RT_Thread 4.0

fal

crclib

2. 使用

2.1 獲取組件

方式1: 通過 Env配置工具 或 RT-Thread studio 開啟軟件包,根據需要配置各項參數;配置路徑為 RT-Thread online packages -> system -> qboot

2.2 功能選項宏定義說明

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

bootloader

+關注

關注

2文章

238瀏覽量

46549 -

狀態指示燈

+關注

關注

0文章

3瀏覽量

7544 -

RT-Thread

+關注

關注

32文章

1385瀏覽量

41657

發布評論請先 登錄

相關推薦

熱點推薦

怎樣使用Jlink (SEGGER) 通過SWD讀寫呢?

怎樣使用Jlink (SEGGER) 通過SWD讀寫呢?Jlink沒有找到CYPD6125的信號,官方也沒有找到CYPD6125對應的FLM和xml 文件

發表于 05-27 06:45

U-Boot 和 Bootloader,99% 的工程師都分不清?

嵌入式軟件工程師聽說過 u-boot 和 bootloader,但很多工程師依然不知道他們到底是啥。 ? 今天就來簡單講講?u-boot 和 bootloader?的內容以及區別

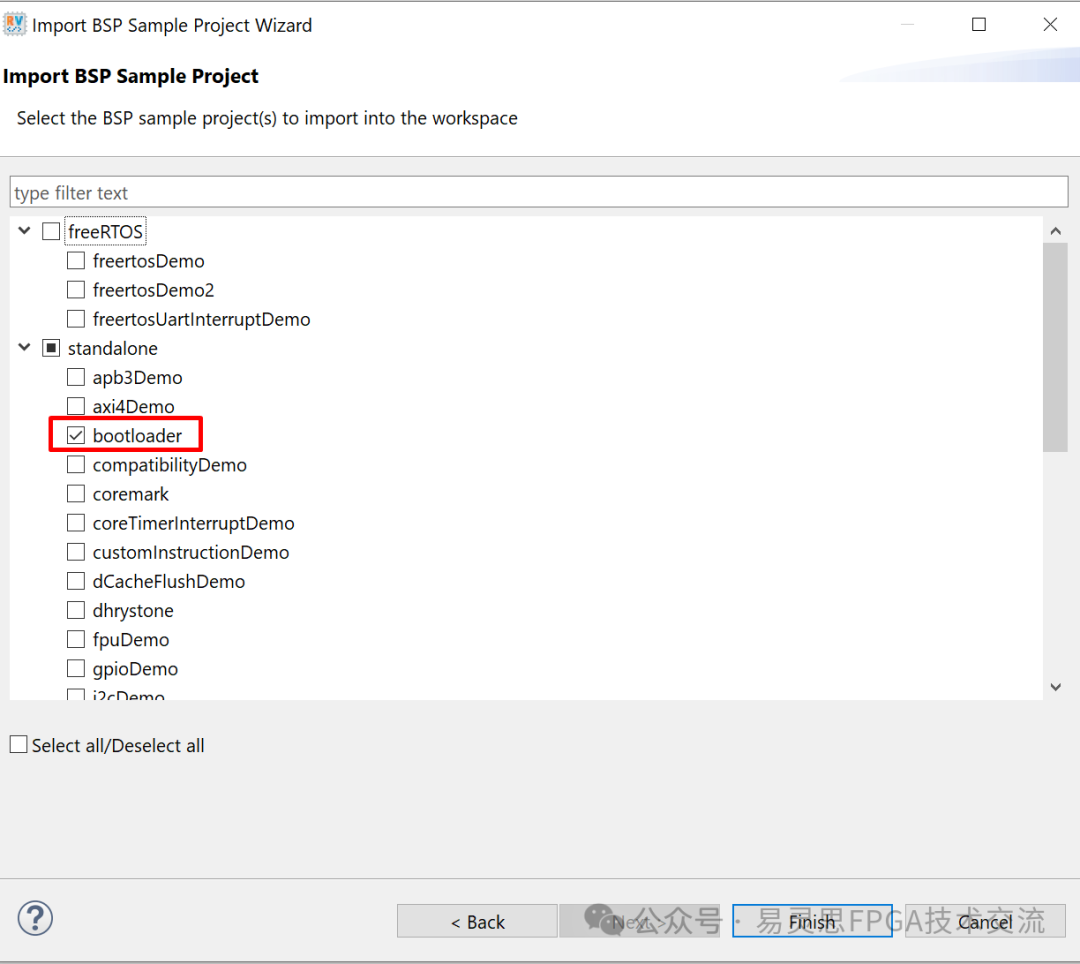

自定義RISC V的bootloader-v3

來講解下怎樣定義自己的bootloader ? 指向外部存儲的Bootloader ? 1、導入軟件自帶的bootloader工程, 在工程中 選擇 bootloaderConfig.

ADS1256的輸出電路是怎樣設計的呢?

對于ADS1256的輸出電路是怎樣設計的呢?一般ADC測試中為了提高輸出的驅動能力,防止發射和振鈴現象,應該怎樣進行設計輸出電路呢?

發表于 11-22 06:01

自定義RISC V的bootloader-v2

來講解下怎樣定義自己的bootloader 在外部存儲的Bootloader 1、導入軟件自帶的bootloader工程,在工程中選擇bootloaderConfig.h文件。 2、修

HPM6750 Bootloader設計

我正在做一個hpm6750evk2的bootloader。設計很簡單,boot工程代碼只做跳轉到1M后的APP工程代碼處,APP工程就是做的一個點燈的程序而已,boot、APP工程都是跑

發表于 10-23 18:59

如何去控制vca820的增益呢?

今天看了vca820的資料。想問一下如何去控制vca820的增益呢?根據數據手冊上做了一個簡單的仿真,在Vg端輸入一個1v正弦波時,必須要加上3v以上的偏置電壓才可以使信號放大10倍,但是改變vg

發表于 09-19 06:49

如何開發不帶Flash API 的Bootloader實現在線升級

電子發燒友網站提供《如何開發不帶Flash API 的Bootloader實現在線升級.pdf》資料免費下載

發表于 09-12 09:41

?0次下載

OPA842增益是怎樣算的,怎么去確定各個阻值的參數呢?

只有當Rf和R1是253到256歐時候,增益才是1倍,可是芯片手冊上面推薦的數據是402歐,請問這個芯片的增益是怎樣算的,怎么去確定各個阻值的參數呢?

新手剛上道,問題膚淺,請不要見怪。

發表于 09-11 07:53

LMH7322怎樣去改善輸出波形呢 ?

圖一

我按照LMH7322資料中,按照上圖一 畫的 PCB圖 (見圖二)

圖二

測試時輸出的波形為:

請問工程師 怎樣去改善輸出波形呢 ?

發表于 09-02 06:57

以下是放大脈沖信號后的輸出波形 ,輸入的脈沖信號為100HZ 占空比為 34% ,怎么去改善波形呢 ?

你好下圖是我 放大脈沖信號后的輸出波形 ,輸入的脈沖信號為100HZ占空比為 34%,請問我該怎樣去改善波形呢 ?

發表于 08-29 06:13

瓴羊Quick BI連續五年入選Gartner? 分析和商業智能平臺魔力象限,中國唯一!

近日,阿里云宣布其憑借商業智能分析產品——Quick BI連續五年獲全球咨詢機構Gartner的分析與商業智能(ABI)魔力象限報告的認可。阿里云成功鞏固在數據分析領域中的挑戰者地位,這也是中國

Quick bootloader是什么?怎樣去使用呢

Quick bootloader是什么?怎樣去使用呢

評論