近期,DRAM制造工藝又實現了一次突破,這次操作來自于SK海力士,該公司宣布,已成功開發出全球首款采用HKMG(High-K Metal Gate)工藝的LPDDR5X內存,采用1αnm制程,該款LPDDR5X與上一代產品相比,功耗降低了25%,數據傳輸速率提高了33%,并在JEDEC設定的1.01V-1.12V超低電壓范圍內運行。

LPDDR5X用于以手機為代表的移動設備,它與PC、服務器用DRAM不同,對低功耗要求很高,同時,性能又不能下降太多,通過采用HKMG工藝,可以更好地保證提高性能地同時,又降低功耗。

以往,HKMG工藝主要用于邏輯芯片,特別是CPU、GPU等處理器,近些年,隨著市場需求的發展,特別是5G通信、汽車智能化、VR/AR和使用AI的邊緣計算等應用場景對內存性能的要求越來越高,DRAM制程工藝演進到了10nm-20nm范圍,此時,高性能與低功耗的矛盾逐漸凸出,而HKMG是解決這一矛盾體的有效方法,首先是應用于非移動設備用DRAM,如服務器中的DRAM,代表企業是三星,如今,HKMG被引入移動設備用DRAM,也就是LPDDR,也是一個標志性的跨越。

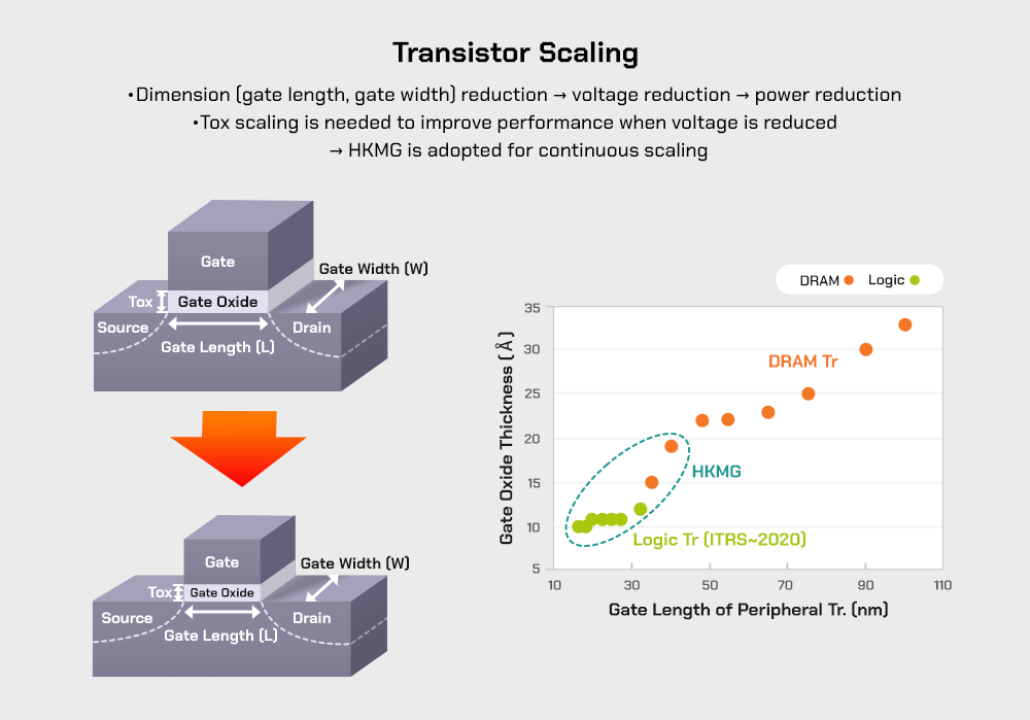

01、HKMG是何方神圣?

早期,集成電路晶體管柵極材料用的是鋁,采用的相關配套結構是鋁金屬/二氧化硅,后來發展到了多晶硅柵,采用的配套結構是多晶硅柵/二氧化硅,之后又經過一段時間的發展,升級到了多晶硅柵/SiON,2007年,HKMG橫空出世。

提起HKMG工藝的由來,不得不提到集成電路傳統霸主英特爾,2007年初,英特爾宣布在45nm制程節點處利用新型High-k(高介電常數)介質材料HfO2(二氧化鉿)來代替傳統SiON作為柵介質層,以改善柵極漏電流問題,同時利用金屬柵代替多晶硅柵,開發出了HKMG工藝。之所以是45nm,是因為半導體制程按照摩爾定律發展到這個節點時,晶體管中最先達到極限的是柵極電介質,傳統的柵極電介質已無法滿足晶體管性能提高、體積縮小的要求,易產生漏電流等問題,造成晶體管可靠性下降,而高K金屬柵則可以解決這一問題。HKMG工藝的最大特點就是介電常數高,HKMG以金屬氧化物作為柵極電介質,與傳統柵極結構相比,可以減少柵極漏電流,降低工作電壓,并提高晶體管可靠性。這是20世紀60年代以來,晶體管技術的重大突破,也是半導體產業的一項重要創新。

可用作高K金屬柵極電介質的金屬氧化物需要具備禁帶寬度高、物理化學性質穩定、熱穩定性好、可制造薄膜材料、與硅元素兼容、兼容CMOS工藝等特點。HfO2是主流的高K金屬柵極電介質材料,在半導體產業得到廣泛應用。但HfO2存在高溫穩定性較弱、與硅兼容性較差、沉積薄膜易產生缺陷等缺點,新的高K金屬柵極電介質還在開發過程中。另外,鉿基材料與多晶硅柵的兼容性一直是一個問題,所以需要采用金屬柵。

當然,采用HKMG技術,對于金屬柵極是有要求的,金屬柵極的選擇受到多種因素的影響,具體就不在此詳述了。

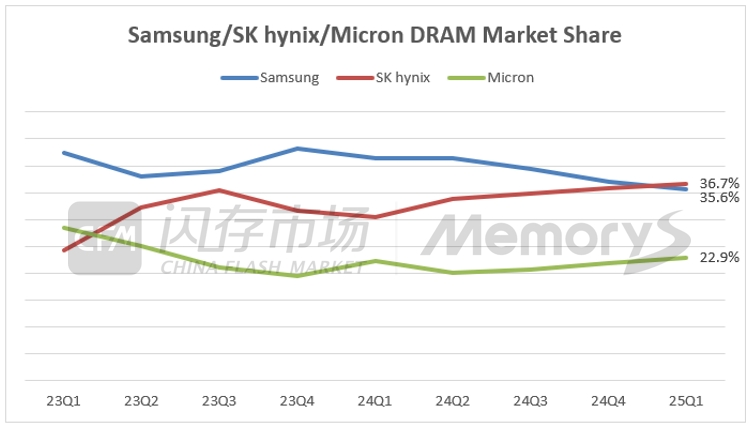

02、DRAM大廠聚焦HKMG

近些年,三星電子,SK海力士、美光這三大存儲芯片廠商競相開發10nm-20nm制程級別DRAM,相繼引入了EUV光刻設備,這在以前只會用于制造各種CPU等處理器,可見市場應用對DRAM要求越來越高,使得這三大廠商必須在制程工藝方面下更多功夫,因此,繼 EUV之后,HKMG成為了另一個焦點。

2021年,三星電子首次將HKMG工藝用于DDR5,并推動了商業化進程。當時,三星電子曾經表示,HKMG DDR5內存模塊的功耗比傳統工藝減少了約13%,計劃根據下一代計算市場的客戶需求,適時將該內存商業化。但是,三星一直沒有公開該款DRAM的商用化案例。今年,TechInsights透露了相關信息,該芯片已經應用于一家中國臺灣高性能內存模塊制造商的產品,據悉,該款DRAM是16Gb的DDR5,采用了HKMG工藝制造。

作為三星電子的老對手,DRAM大廠SK海力士自然不會坐視三星在DRAM技術方面領先,看到對手在PC、服務器用DRAM上采用了HKMG工藝,SK海力士更進一步,將該工藝用在了對功耗要求更高的移動設備DRAM上,也就是前文提到的LPDDR5X。

那么,SK海力士是如何做到的呢?

首先要了解一下DRAM的基本結構,組成DRAM的晶體管有以下幾種:存儲數據的單元晶體管(Cell Transistor),恢復數據的核心晶體管(Core Transistor),涉及控制邏輯和數據輸入/輸出的外圍晶體管(Peripheral Transistor)。隨著技術的進步,單元晶體管在提高DRAM存儲容量方面取得了一些技術突破。然而,原來的核心晶體管和外圍晶體管特性越來越不適合DRAM的應用要求,成為了發展瓶頸,特別是對于外圍晶體管而言,只有實現工藝尺寸的進一步微縮,才能提高性能,在需要快速提高性能的高端產品中尤為如此。因此,需要一種全新的解決方案來克服微縮基于多晶硅柵極/SiON的晶體管時存在的限制,此時,HKMG工藝就是一個理想方案。

為了將DRAM的多晶硅柵極/SiON轉換為HKMG柵極,需要對相關工藝進行更改,還必須對HKMG材料、工藝和集成流程進行優化,以適合新材料和新工藝。具體來看,要開發出一套復雜的工藝(具體情況不得而知,因為這是SK海力士的核心競爭力,屬于絕對的商業機密),來解決以下幾個問題。

一是要解決兼容性問題。與多晶硅柵極/SiON相比,HKMG的熱穩定性較弱,由于DRAM需要在高溫下進行特殊處理,以實現單元陣列結構,這與邏輯芯片(CPU、GPU等)采用的HKMG工藝有很大不同。因此,DRAM中HKMG工藝的特殊性會導致其可靠性下降,這就必須對HKMG工藝和DRAM集成工藝進行優化,以解決可靠性下降問題。

二是新材料控制。需要引入工藝控制措施,例如針對新材料的測量方案,以防止現有器件受到新材料和新工藝的影響。

三是要開發具有成本效益的工藝。可通過工藝集成優化,最大限度地減少因引入新材料和新工藝而導致的成本增加。

四是設計與測試優化。隨著柵極材料的變化,晶體管特性和可靠性與傳統多晶硅柵極/SiON截然不同,為了最大限度地發揮HKMG的優勢,增強可靠性,需要新設計方案,并優化相關測試。

總之,通過將HKMG整合、優化成為適用于DRAM工藝的形式,開發出新平臺,并通過包括試點操作在內的預驗證工藝來確保方案可行,從而實現將HKMG工藝用于DRAM量產。

03、結語

以往,具備低漏電、高性能特性的先進制程工藝多用于邏輯芯片,特別是PC、服務器和智能手機用CPU,如今,這些工藝開始在以DRAM為代表的存儲器中應用,再加上EUV等先進設備和工藝的“互通”,邏輯芯片和存儲器的制程節點和制造工藝越來越相近。

在上世紀60年代,當CPU剛開始批量生產的時候,其制造工藝就是基于當時的存儲器SRAM的工藝,經過幾十年的發展,應用系統的變遷對CPU的要求不斷提高,相應的制程工藝隨摩爾定律快速發展。相對而言,存儲器對制程的要求沒有CPU那么高,但隨著應用的進一步發展,特別是大數據和AI的演進,原有存儲器制程的發展節奏難以滿足應用要求了。因此,存儲器制程工藝緊追了上來,目前已經十分接近以CPU為代表的邏輯芯片了。

這樣的發展也使得CPU和DRAM之間的工藝壁壘變小了,這也在一定程度上迎合了存算一體發展趨勢,也就是將CPU、AI等功能集成進DRAM。HKMG工藝在DRAM上的應用可以進一步促進存算一體的發展。

審核編輯:郭婷

-

芯片

+關注

關注

459文章

52395瀏覽量

439173 -

DRAM

+關注

關注

40文章

2344瀏覽量

185408 -

服務器

+關注

關注

13文章

9764瀏覽量

87669

原文標題:DRAM工藝快追上CPU了

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

針對晶圓上芯片工藝的光刻膠剝離方法及白光干涉儀在光刻圖形的測量

利基DRAM市場趨勢

HBM重構DRAM市場格局,2025年首季DRAM市占排名

三星在4nm邏輯芯片上實現40%以上的測試良率

三星否認重新設計1b DRAM

三星重啟1b nm DRAM設計,應對良率與性能挑戰

高K金屬柵極的結構、材料、優勢以及工藝流程

北京君正預計年底推出21nm DRAM產品

SRAM和DRAM有什么區別

DRAM存儲器的基本單元

SK海力士轉向4F2 DRAM以降低成本

DRAM在計算機中的應用

底部填充工藝在倒裝芯片上的應用

HKMG工藝在DRAM上的應用

HKMG工藝在DRAM上的應用

評論