你是否還在為你接收機中的鄰信道抗擾性頭疼不已?

怎么就沒達到指標要求呢?

到底要整哪部分呢?

更換濾波器的形式,提高濾波器的抑制度?但是到底要提高多少?

改變一下鏈路中的增益,會不會有效果?

優化一下本振的相噪?但到底要優化多少。

今天這篇文章就給你講清楚。

假設,鏈路的動態范圍是OK的,也就是說,強的干擾信號和小的有用信號一起進入接收機,不管采用何種手段,需要保證,這兩個信號到達ADC前面時,兩者的功率差,是能滿足ADC的SFDR的,即ADC能夠同時識別這兩個信號。

這時,鄰信道抗擾性的好壞,就主要與以下兩個因素相關:

(1)本振相噪

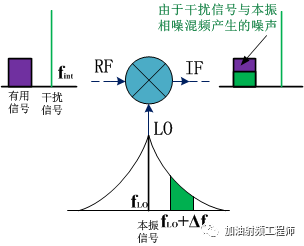

干擾信號會與本振相噪,通過混頻器,在有效中頻處產生噪聲,進而影響信號的SNR,如下圖所示。

(2) 混頻前鏈路中對干擾信號的抑制度

上面的兩個因素是聯動的,混頻前鏈路中對干擾信號的抑制度增加1dB,對本振相噪的要求就會降低1dB。

所以,可以由鄰信道抗擾性指標,推算出要求的本振相噪。如果本振由于其他限制,達不到要求的指標,就可以用濾波器來協助。

有人說,我覺得那些公式太燒腦,我想閉眼就能計算出來。

沒問題,我給你們整理成excel計算工具了。

審核編輯:湯梓紅

-

接收機

+關注

關注

8文章

1221瀏覽量

54298 -

adc

+關注

關注

99文章

6659瀏覽量

548547 -

混頻器

+關注

關注

10文章

844瀏覽量

46792 -

鏈路

+關注

關注

1文章

74瀏覽量

14218 -

射頻系統

+關注

關注

0文章

124瀏覽量

13527

原文標題:知道這一點,射頻系統設計能力上個臺階

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何判斷你的電路設計能力

W25Q128FV圖像寫入如何在PSoC5LP中做到這一點?

我希望PSOC-5在使用UBFSUART時中斷,每次接收到字節,如何做到這一點?

請問我該如何停止這一點,并獲得準確的閱讀?

請問我可以用vee做到這一點嗎?

在用到stm32的adc的時候需要注意外部無法操作這一點嗎?

用編程方式禁用滑塊我怎樣才能做到這一點?

求助,為何作為USB從設備時,M4521能免晶振,而M452沒說這一點?

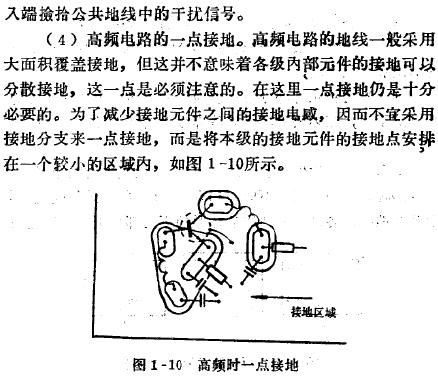

一點接地,什么是一點接地,一點接地應注意的問題

iOS10.2正式版發布 但蘋果這一點還是輸給了小米

空調能效等級對消費者的意義真的就只是省電這一點嗎

輕薄與高性能可否兼具?最新的AERO 15 OLED版做到這一點?

直角減速電機真的可以節省空間嗎?它是怎樣做到這一點的?

【經驗分享】PCB打板,只做錯了這一點,直接損失上百萬!

知道這一點,射頻系統設計能力上個臺階

知道這一點,射頻系統設計能力上個臺階

評論