來源:《半導體芯科技》雜志2/3月刊

作者:孫家遠,賀利氏技術方案工程師

射頻前端(RFFE)模組國內外手機終端中廣泛應用。它將功率放大器(PA)、開關(Switch)、低噪聲放大器(LNA)、濾波器(Filter)、無源器件等集成為一個模組,從而提高性能,并減小封裝體積。然而,受限于國外專利以及設計水平等因素,國產濾波器的份額相當低。在模塊集成化的趨勢下,國內射頻巨頭在布局和生產濾波器。聲學濾波器可分為聲表面濾波器和體聲波濾波器,其中聲表面濾波器可根據適用的頻率細分為SAW、TC-SAW和IHP-SAW。體聲波濾波器適用于較高的頻段,可細分為BAW、FBAR、XBAR等。無論是SAW(Surface Acoustic Wave filter)還是BAW(Bulk Acoustic Wave Filter),均是在晶圓級封測后以倒裝芯片的工藝貼裝在模組上。

在晶圓級封裝(WLP)工藝中,Bump制造是相當重要的一道工序,因此,本文將淺談濾波器晶圓級封裝中Bump制造的關鍵點。當前業內常見的幾種SAW filter Wafer Bumping工藝如下:

1.通過打線工藝在晶圓的UBM(Under Bump Metal)上植金球。

2.通過鋼網印刷工藝在UBM上印刷錫膏,再經過回流焊成球。

3.先在晶圓的UBM上印刷助焊劑,將錫球放到UBM上,再經過回流焊完成植球。

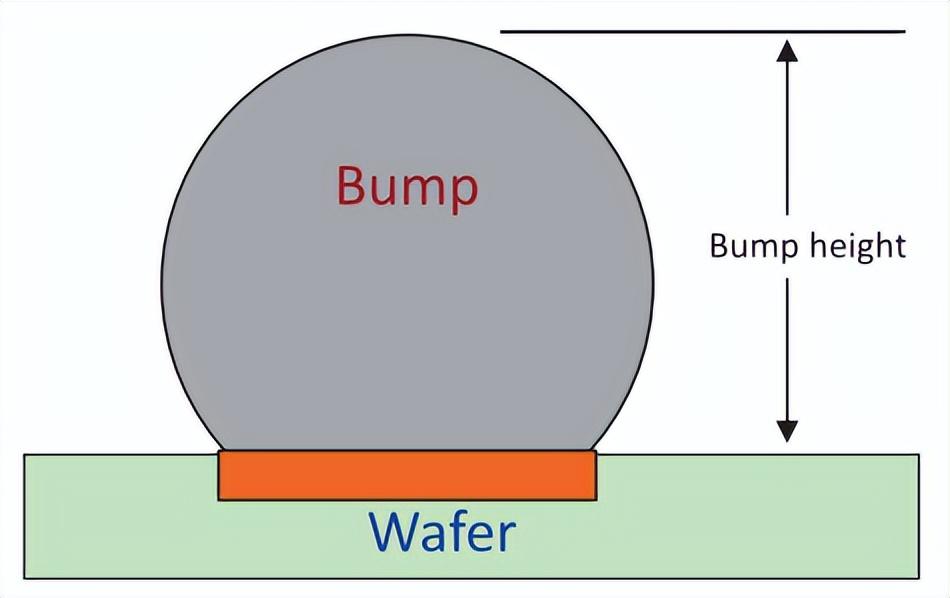

△圖1:球高。

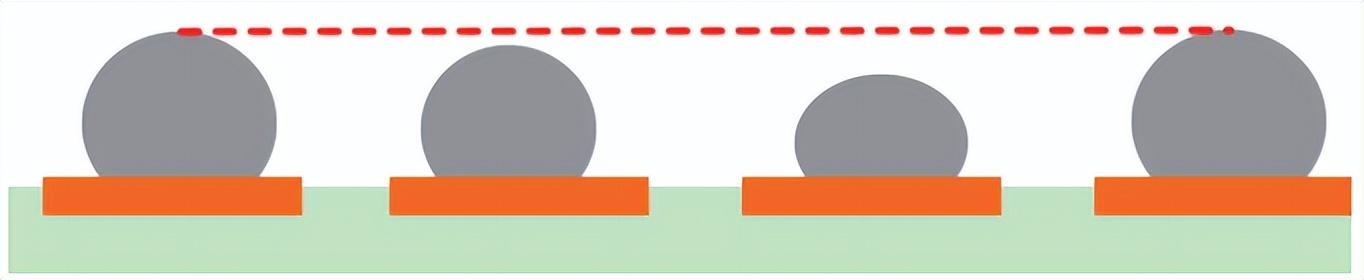

本文重點介紹第二種工藝。通過對印刷錫膏方案的剖析發現,在Bumping工藝中Bump的高度和共面度(同一顆芯片上Bump高度最大值最小值之差,差值越低越好)是最重要的關鍵指標(如圖1和圖2)。下面從鋼網的工藝和設計、錫膏的特性等方面進行分析。

△圖2:共面度。

鋼網印刷

鋼網印刷的目的是使錫膏材料通過特定的圖案孔沉積到正確的位置上。首先,將錫膏放到鋼網上,再用刮刀使其通過鋼網開孔沉積到焊盤上。鋼網與晶圓之間的距離(印刷間隙)、印刷角度、壓力、速度和膏體的流變特性是確保錫膏印刷的關鍵參數。一旦鋼網開孔被膏體填滿,脫模后膏體留在每個焊盤上,沉積在焊盤上的體積取決于鋼網的孔距和孔壁的質量、焊盤的表面特性和膏體的流變性能。

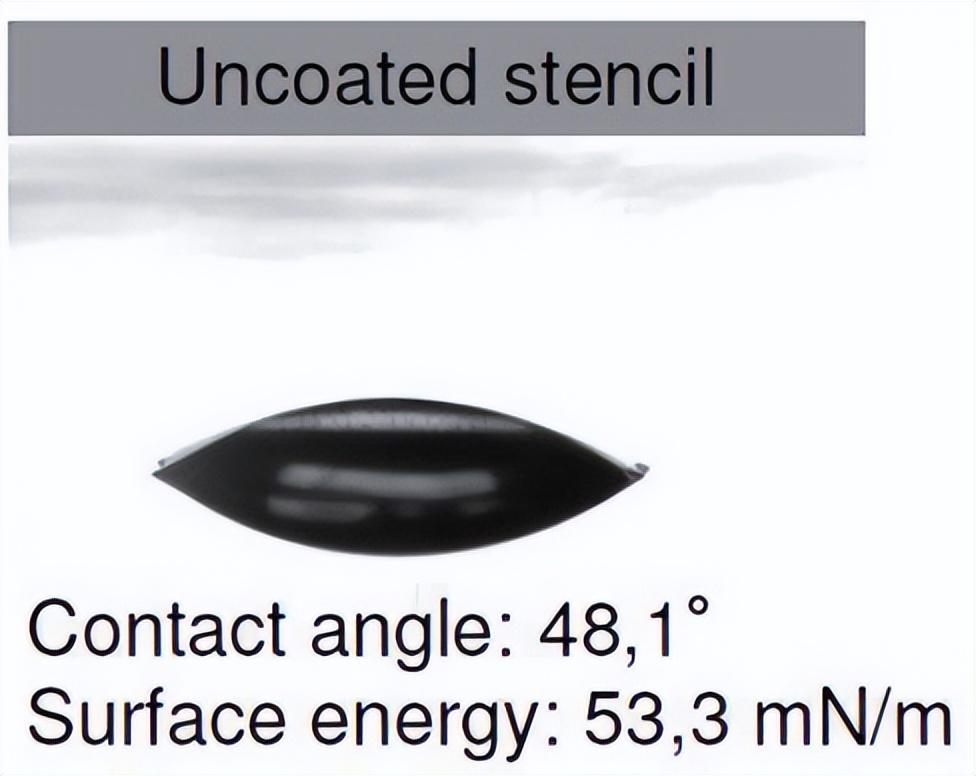

△圖3:無納米涂層鋼網(Source: Laser Job)

鋼網的加工工藝與開孔設計

鋼網孔壁質量、尺寸一致性、定位精度和鋼網生產成本是鋼網生產工藝的選擇標準。考慮到帶有Bump的濾波器是以倒裝芯片的工藝應用在前端射頻模組里,其特點是Bump的尺寸小(bump高度在50~100μm之間)、間距小、對Bump高度的一致性要求高(共面度在10μm以內)。為了滿足以上要求,業內最常選用的是納米涂層鋼網和電鑄鋼網。

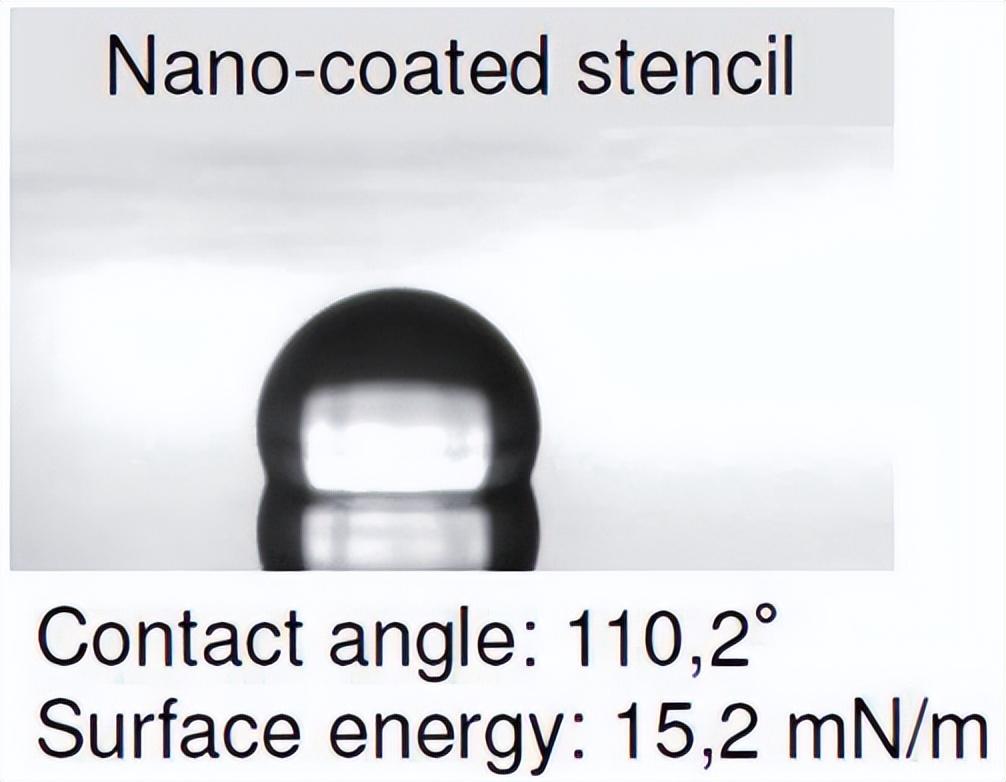

納米涂層鋼網的工藝是:在激光切割的基礎上對鋼網進行清洗,然后在鋼網內壁進行打磨拋光以降低粗糙度,最后涂覆納米涂層。納米涂層使接觸角顯著增加,從而降低鋼網材料的表面能,有利于錫膏脫模。

△圖4:納米涂層鋼網(Source: Laser Job)

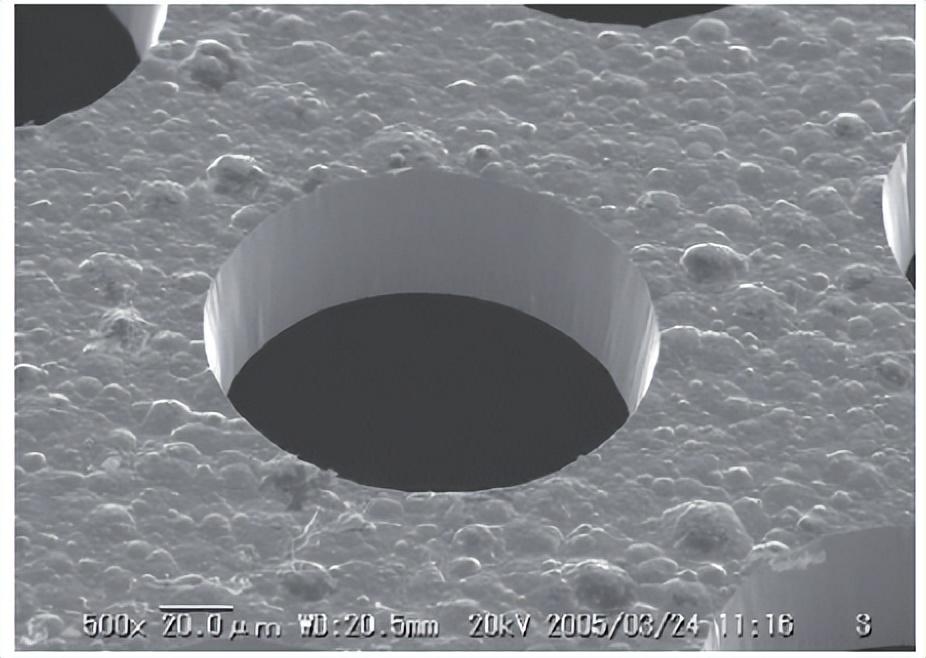

電鑄鋼網的制作方法是:先在導電基板上用光刻技術制備模板,然后在阻膠膜周圍進行直流電鑄,最后從光刻膠孔上剝離。電鑄鋼網的質量和印刷性能取決于光刻膠的靈敏度、所用光刻工具的類型、導電基材的光學性能和電鑄工藝。電鑄鋼網的開孔內壁非常光滑(如圖5所示),其印刷脫模的表現也最好最穩定。

△圖5:電鑄鋼網孔壁(Source: Bon Mark)

小結一下,納米涂層鋼網的印刷表現略遜于電鑄鋼網,其涂層在批量生產一段時間后可能會脫落,但是納米涂層鋼網的價格遠低于電鑄鋼網;電鑄鋼網的側壁非常光滑,其印刷表現最好,是超細間距應用的最佳選擇,但電鑄鋼網的價格相當昂貴。鋼網的選擇取決于客戶對產品特性和成本的綜合考量。

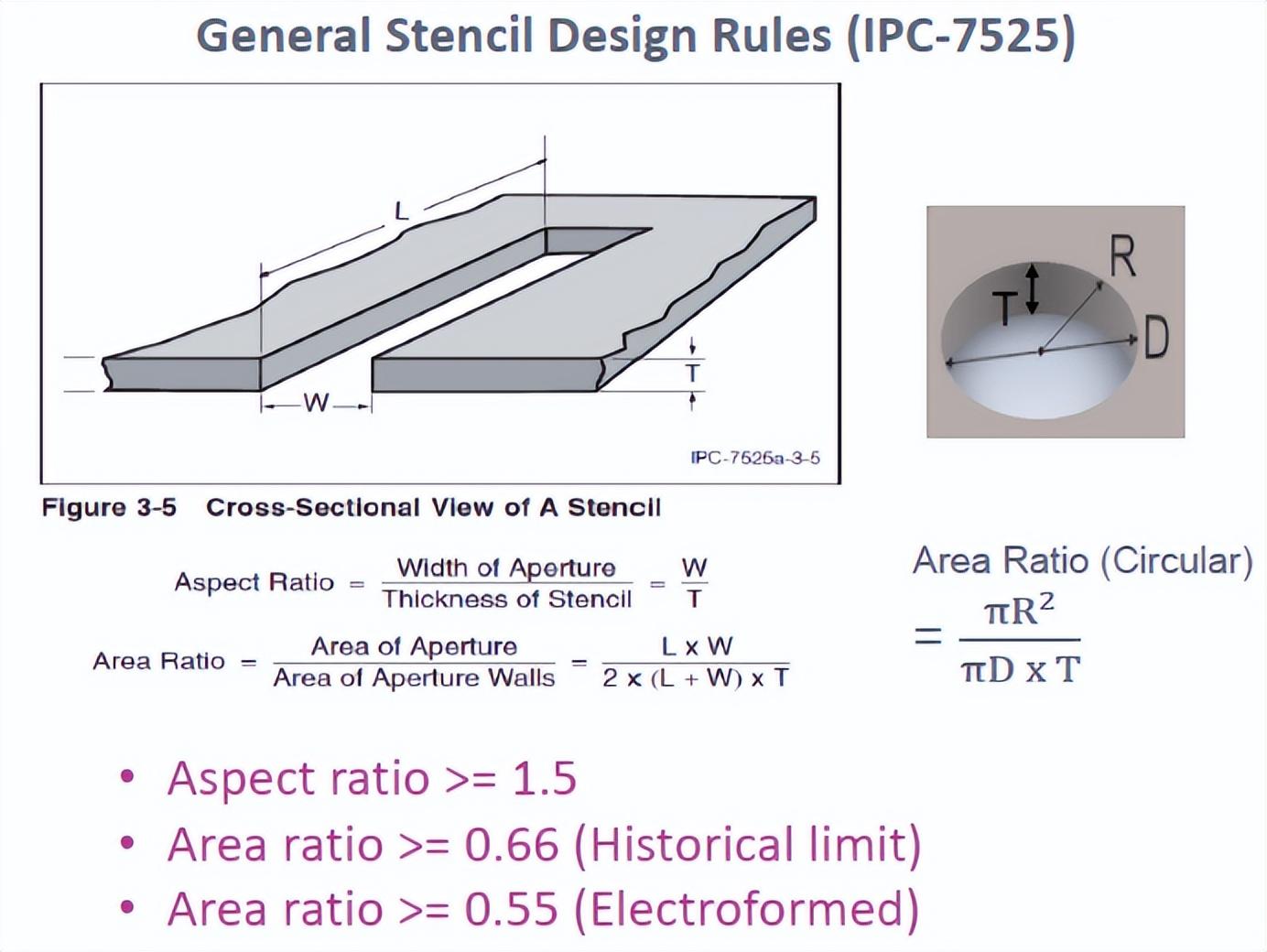

開孔面積比

由于CTE不匹配會影響封裝的可靠性,符合高度要求的Bump在這方面會起到積極的作用。這就要求鋼網印刷過程可靠地沉積穩定的錫膏量,以產生堅固的互連。錫膏從鋼網孔的釋放是由錫膏在鋼網孔側壁和晶圓焊盤之間的相互作用決定的。據文獻記載,為了從鋼網印刷中獲得良好的膏體釋放效率,模板開孔面積比[開孔面積比=開口面積/孔壁面積]應大于0.66。該比率限制了給定孔徑大小的模板厚度,并要求使用更薄的模板來印刷更細的間距。隨著鋼網制作工藝的提升,鋼網開孔的面積比可以適當降低,如圖6所示。

△圖6:鋼網開孔規則。

錫膏

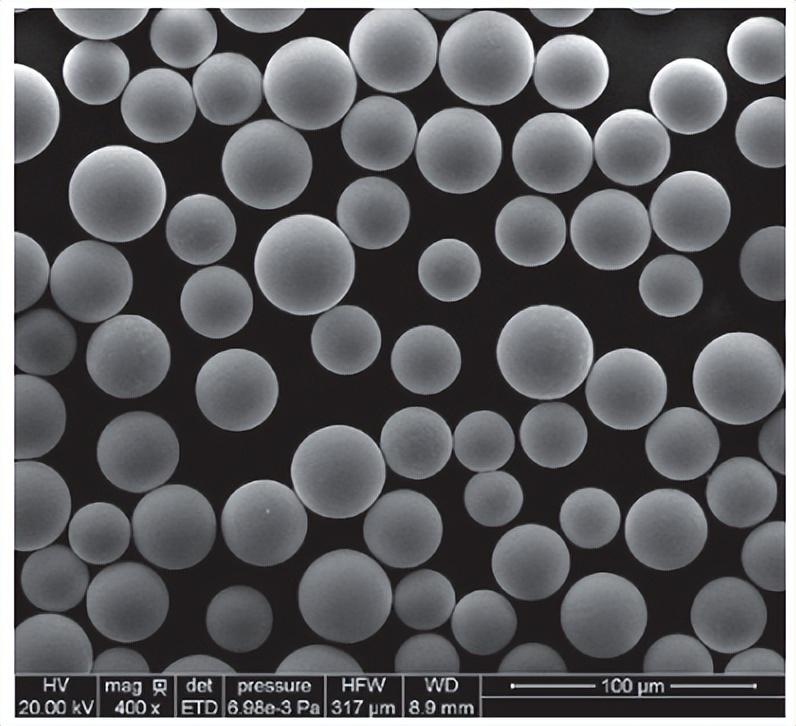

錫膏是由焊粉和助焊劑均勻混合而成的膏體,其中錫球的形狀、顆粒大小、尺寸分布、氧化程度以及助焊劑載體的流變性能和配方體系,都對錫膏的印刷和回流性能起著重要作用。細間距印刷用的焊粉一直是賀利氏電子的優勢,因為Welco?technology(一種在油介質中分散熔融合金的制造技術)利用兩種不同介質的表面張力存在差異的原理,用工藝配方控制粉末尺寸范圍,摒棄了傳統的網篩工序,避免了粉末顆粒因網篩而導致的形變(表面積變大)。再者,粉末在油介質中得到充分保護,減少了粉末表面的氧化。Welco?焊粉搭配賀利氏獨特的助焊劑配方體系,使印刷錫膏的轉化率能夠得到保證。

△圖7:Welco焊粉SEM圖片。

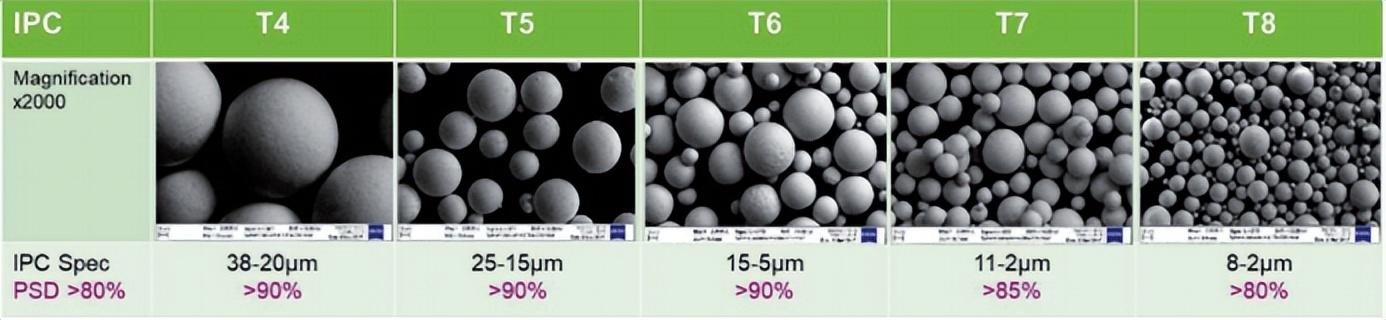

當前市場上SAW/BAW濾波器的應用中常見的Bump高度為50-100μm,結合單個芯片的layout,即相鄰bump的最小間距,以及相鄰芯片的bump的最小間距,6號粉和7號粉錫膏是匹配的選擇。粒徑的定義是基于IPC的標準(如圖8),即6號粉有80%的焊粉粒徑分布在5-15μm的區間。

△圖8:IPC粒徑規格。

選擇合適粒徑的錫膏非常重要,助焊劑體系的選擇也是非常關鍵。因為一些SAW的IDT位置是裸露的,焊錫膏或助焊劑的飛濺都有可能影響IDT的信號和聲波之間的轉換。對此,賀利氏開發的AP5112和AP520系列產品在開發時均在飛濺方面做了深入的研究,從而盡可能避免飛濺問題。Bump中空洞的表現也是非常重要的質量指標,尤其是在模組中經過多次回流焊之后。

案例分享

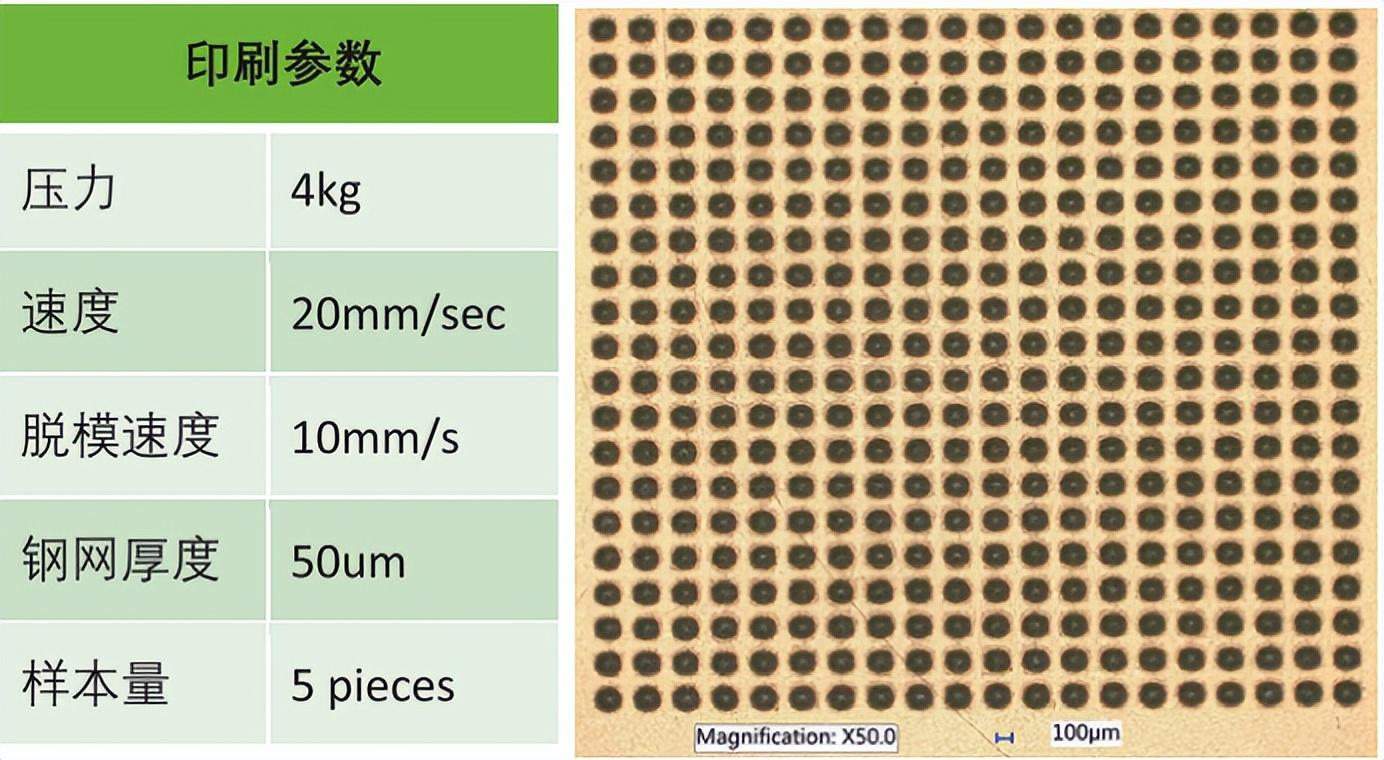

應用:SAW filter 6 inch

鉭酸鋰晶圓(印刷測試以銅板代替鉭酸鋰晶圓)

Bump高度=72±8μm;共面度<10μm

鋼網開孔尺寸:130*140*50μm

錫膏:AP5112 SAC305 T6

印刷穩定性是影響bump高度一致性的關鍵因素。印刷窗口的定義通常受印刷設備的能力、鋼網的加工工藝、產品設計等因素的影響,通常通過實驗驗證獲得。如圖9所示,6號粉錫膏的連續印刷表現優異,沒有發現連錫和大小點的問題。Bump的高度數據能夠更好地說明。

△圖9:印刷后。

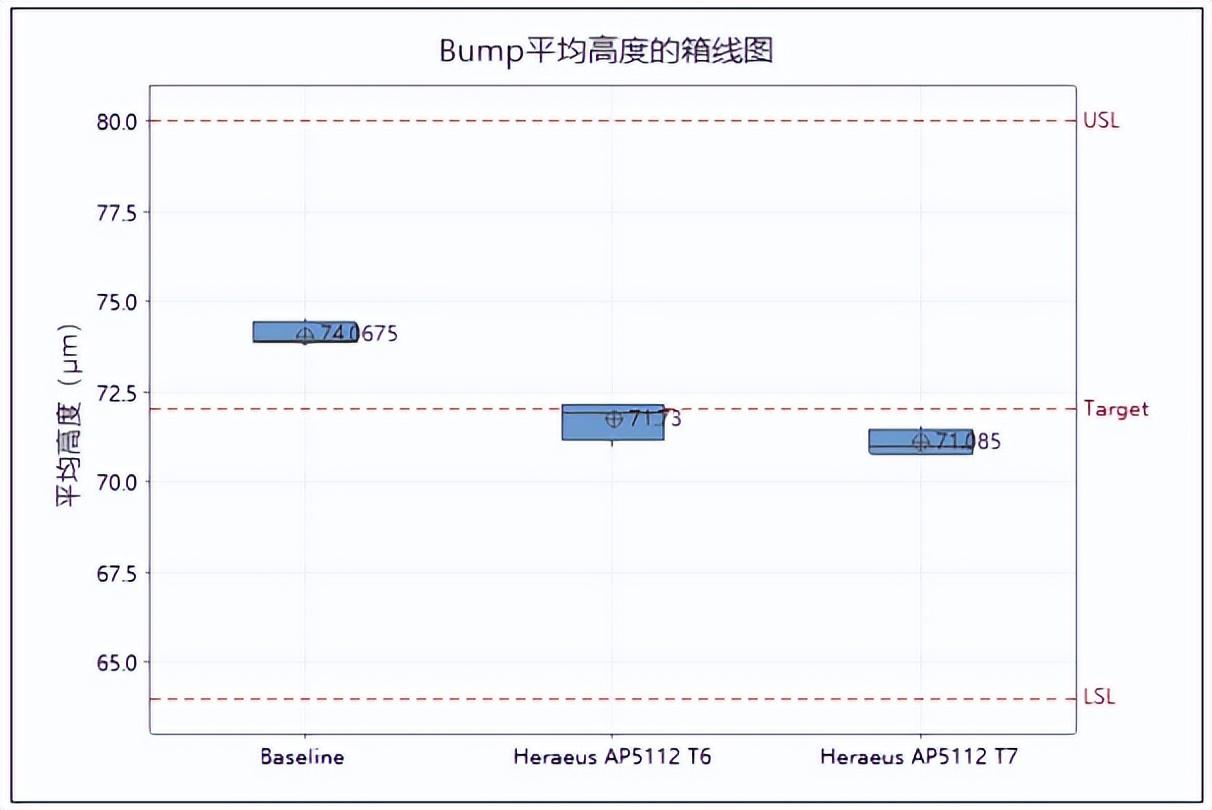

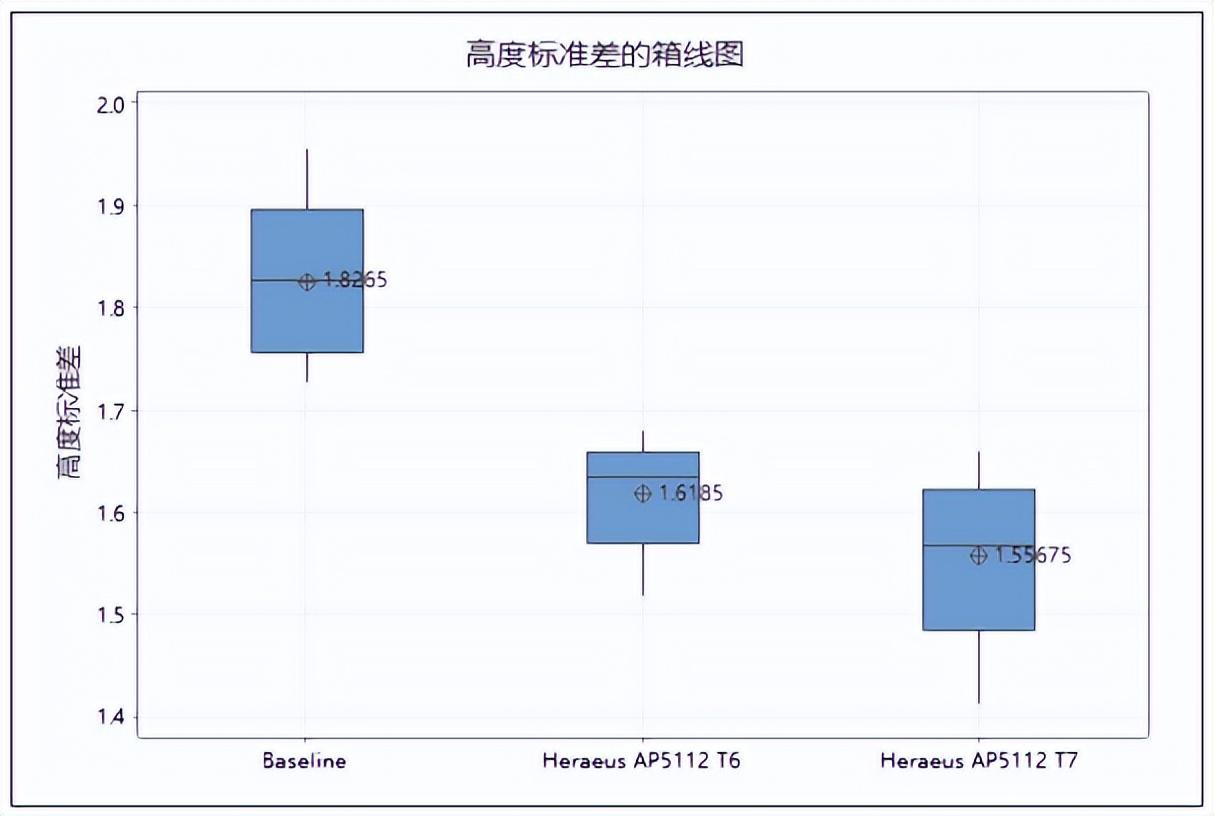

在回流焊過程中,已印刷在UBM區域的錫膏逐步熔化,助焊劑流至焊錫四周,而焊料熔化后回流到UBM上并在界面之間形成金屬間化合物(Intermetallic layer),冷卻后形成一定高度的Bump。Bump的平均高度非常靠近目標值,且標準差相對較小,如圖10和圖11所示。

△圖10:Bump高度數據。

△圖11:Bump高度標準差。

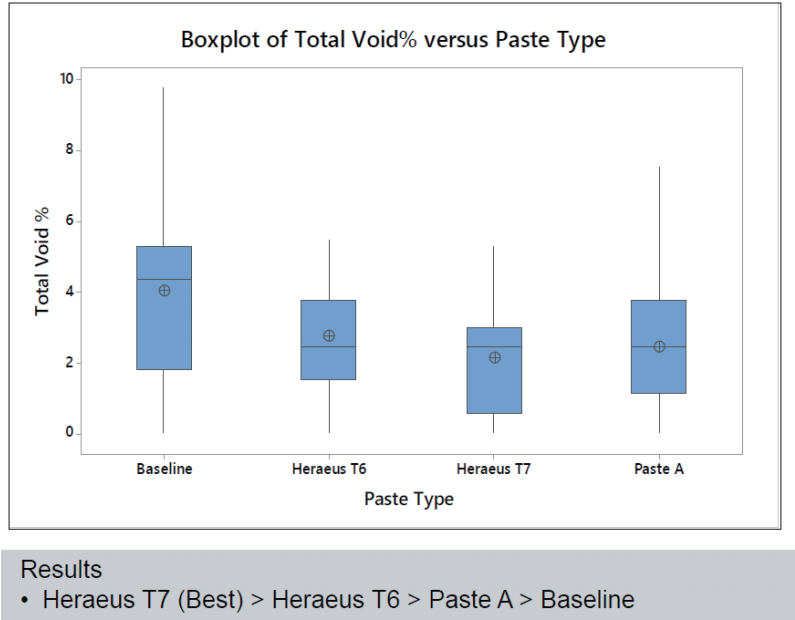

Bump高度的指標非常關鍵,Bump中的空洞也至關重要。在SAW filter上面的結果顯示,賀利氏的6號粉和7號粉具有良好的表現,如圖12所示。

△圖12:Bump void數據。

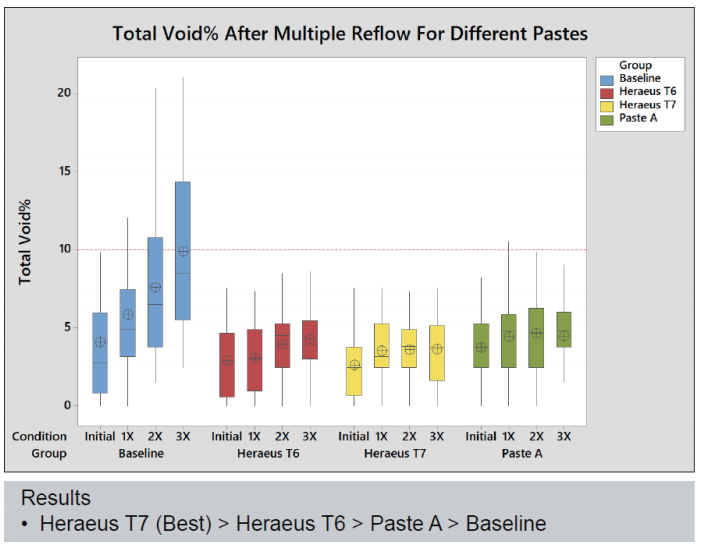

晶圓級封裝最終會以芯片級應用到系統封裝,即以倒裝芯片的工藝集成到模組里。在此過程中會經歷多次回流焊工藝,那么回流焊之后bump內部的空洞會發生怎樣的變化?對此,我們測試了3次回流焊之后bump內部空洞的變化,結果如圖13所示。賀利氏的6號和7號粉錫膏。對應的Bump,在經過3次回流焊之后仍然能夠保持在比較好的水平。

△圖13:多次回流焊后空洞變化的數據。

總結

本文簡單闡述了晶圓級封裝的關鍵技術點。賀利氏Welco焊粉和獨有的助焊劑配方體系能夠匹配SAW、BAW等濾波器的晶圓封裝需求。更深層次的技術細節,如Bump高度的設計和球高與錫膏量的關系,敬請期待下一篇文章。不論是晶圓級封裝還是先進封裝賀利氏都能提供成熟的解決方案。

審核編輯黃宇

-

濾波器

+關注

關注

162文章

8131瀏覽量

181862 -

晶圓

+關注

關注

53文章

5149瀏覽量

129675 -

封裝

+關注

關注

128文章

8641瀏覽量

145325

發布評論請先 登錄

晶圓級封裝Bump制造工藝關鍵點解析

晶圓級封裝Bump制造工藝關鍵點解析

評論