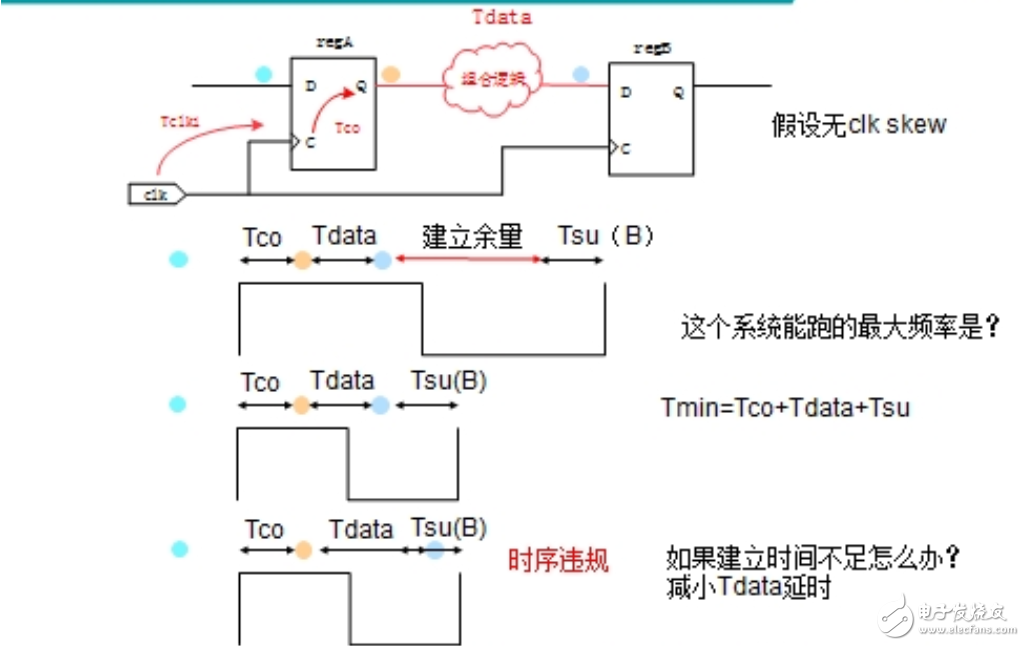

本文將詳細(xì)介紹輸出延時(shí)(output delay)的概念、場(chǎng)景分類(lèi)、約束參數(shù)獲取方法以及約束方法。

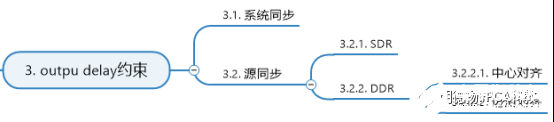

圖1 output delay約束類(lèi)型

如上圖1所示:輸出延時(shí)(output delay)約束與輸入延時(shí)(input delay)約束相似,輸出延時(shí)亦分成系統(tǒng)同步和源同步兩大情形。

其中源同步根據(jù)時(shí)鐘特性,又可以細(xì)分成SDR和DDR兩種情況。根據(jù)數(shù)據(jù)和時(shí)鐘的相位關(guān)系,DDR可以分成中心對(duì)齊和邊沿兩種。本文將詳細(xì)討論各種情況下的約束方法。

第1節(jié) 輸出延時(shí)約束的目的

在詳細(xì)討論輸出延時(shí)約束之前,明確為什么要做輸出延時(shí)約束,通過(guò)該約束可以解決什么問(wèn)題?

第2節(jié) 輸出延時(shí)概念

設(shè)置輸出延時(shí)的目標(biāo):讓FPGA調(diào)整自身輸出的時(shí)序,使輸出的時(shí)序滿足下游器件寄存器的建立時(shí)間和保持時(shí)間要求,來(lái)使得下游器件能夠正確的捕獲數(shù)據(jù)。

2.1 輸出延時(shí)的max與min

2.1.1 max

max的意思是最大延時(shí)時(shí)間,用于考慮建立時(shí)間:一般為正數(shù),表示數(shù)據(jù)在時(shí)鐘采樣沿之前就到達(dá)。

最大延時(shí)時(shí)間公式:最大板級(jí)延時(shí)+TSU。TSU為下游器件要求的建立時(shí)間。假如板級(jí)延時(shí)為0,則max就是下游器件的“TSU”。

2.1.2 min

min的意思為最小延時(shí)時(shí)間,用于考慮保持時(shí)間:一般為負(fù)數(shù),表示數(shù)據(jù)在時(shí)鐘采樣沿之后還保持了一段時(shí)間 。

公式:最小板級(jí)延時(shí)-TH。TH為下游器件要求的保持時(shí)間。假如板級(jí)延時(shí)為0,min則是下游器件的“-Th”。

第3節(jié) 輸出延時(shí)的兩種測(cè)量方法

3.1 下游器件的參數(shù)(推薦)

第一種是根據(jù)下游器件的參數(shù)來(lái)設(shè)置建立時(shí)間和保持時(shí)間,通過(guò)下游器件的數(shù)據(jù)手冊(cè),可以得知下游器件寄存器的建立時(shí)間和保持時(shí)間的要求。在得知下游器件的建立時(shí)間和保持時(shí)間之后,就可以進(jìn)行相應(yīng)的設(shè)置,從而實(shí)現(xiàn)時(shí)序約束。

3.2 示波器測(cè)量

第二種方法是用示波器測(cè)量下游器件的一個(gè)輸入端口,來(lái)得到它的時(shí)序信息。 比如說(shuō)它的延時(shí)這種信息。但這種方法一般不常用。本書(shū)推薦使用第一種方法,因?yàn)榈诙N方法要求硬件做的比較規(guī)范,不能出現(xiàn)延時(shí)不斷抖動(dòng)的情況。

第4節(jié) 各應(yīng)用場(chǎng)景下的約束方法

接下來(lái)討論各種不同情況下輸出接口的時(shí)序約束方式。

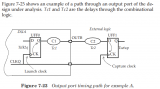

4.1 系統(tǒng)同步

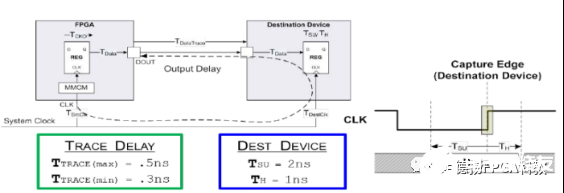

如圖2所示,系統(tǒng)同步就是FPGA和下游器件共用一個(gè)時(shí)鐘,可以認(rèn)為這個(gè)時(shí)鐘的延時(shí)等于零。但實(shí)際上,F(xiàn)PGA把數(shù)據(jù)送給下游器件,是有一定延時(shí)的。

一般下游器件的寄存器會(huì)有一個(gè)建立時(shí)間和保持時(shí)間參數(shù)。可以從數(shù)據(jù)手冊(cè)中得到下游器件相應(yīng)的參數(shù),比如說(shuō)它的建立時(shí)間是2ns,保持時(shí)間是1ns。而FPGA的延時(shí)可能符合一個(gè)抖動(dòng)的情況,通過(guò)示波器測(cè)量或者計(jì)算方式可以得到FPGA的板級(jí)延時(shí)。比如說(shuō)它的板級(jí)延時(shí)最大是0.5ns,板級(jí)延時(shí)最小是0.3ns。

圖2 系統(tǒng)同步接口示意圖

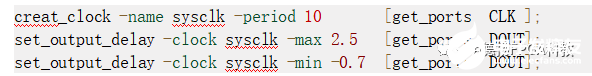

當(dāng)測(cè)量得到板級(jí)延時(shí)之后,下一步便可以進(jìn)行配置了。比如說(shuō)最大的輸出延時(shí)為最大的板級(jí)延時(shí)加上建立時(shí)間要求,即2ns+0.5ns=2.5ns。最小板級(jí)延時(shí)為輸出最小延遲時(shí)間減去下游芯片寄存器保持時(shí)間,即0.3ns–1ns=-0.7ns。使用TCL語(yǔ)句實(shí)現(xiàn)以上約束的代碼如下所示:

上面約束語(yǔ)句首先是通過(guò)creat_clock創(chuàng)建了一個(gè)生成時(shí)鐘,輸出給下游芯片作為時(shí)鐘信號(hào)(需要注意該信號(hào)本身是存在的,只是通過(guò)創(chuàng)建生成時(shí)鐘的方式告知quartus、vivado等綜合軟件該信號(hào)是時(shí)鐘信號(hào))。然后,set_output_delay –clock sysclk -max 2.5 [get_ports DOUT]的含義就是輸出信號(hào)DOUT相對(duì)生成時(shí)鐘sysclk的最大延遲是2.5ns。而set_output_delay –clock sysclk -min -0.7 [get_ports DOUT] 的含義就是輸出信號(hào)DOUT相對(duì)生成時(shí)鐘sysclk的最小延遲是-0.7ns。

這是系統(tǒng)同步的情況,系統(tǒng)同步就是FPGA和下游器件共用一個(gè)時(shí)鐘信號(hào)。

4.2 源同步SDR

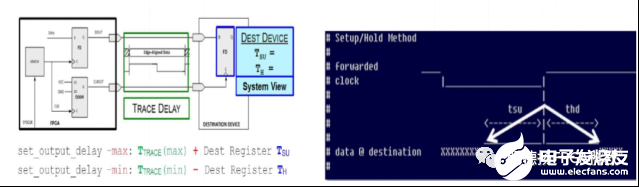

接下來(lái)看一下源同步,如圖3所示,F(xiàn)PGA輸出數(shù)據(jù)給下游器件同時(shí),也會(huì)與數(shù)據(jù)同步輸出一個(gè)時(shí)鐘信號(hào)給下游器件,時(shí)鐘和數(shù)據(jù)一起傳輸。其中分為SDR和DDR。SDR是指使用時(shí)鐘上升沿去采樣數(shù)據(jù),DDR是指上升沿和下降沿都去采樣數(shù)據(jù)。

圖3 SDR傳輸示意圖

上圖3為典型的SDR傳輸示意圖,SDR使用上升沿對(duì)數(shù)據(jù)進(jìn)行采樣。SDR的原理、方法與系統(tǒng)同步都是一樣的,也是通過(guò)查數(shù)據(jù)手冊(cè)得到下游器件寄存器的建立時(shí)間、保持時(shí)間。它保持的要求也能知道我的這個(gè)延時(shí)的抖動(dòng)是多少啊。在測(cè)量之后得到最大抖動(dòng)和最小抖動(dòng),就能根據(jù)公式計(jì)算出最大延遲時(shí)間和最小延遲時(shí)間。根據(jù)公式,最大延時(shí)時(shí)間是指板級(jí)傳輸延時(shí)最大值加上下游器件建立時(shí)間要求,而最小延遲是指板級(jí)傳輸延遲最小值減去下游器件保持時(shí)間。

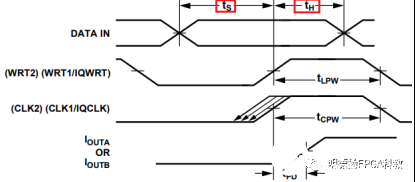

MP801開(kāi)發(fā)板提供了兩路高速DAC,AD9709時(shí)鐘頻率最高支持125MHz,輸出也是符合SDR要求的,通過(guò)閱讀手冊(cè)獲取該芯片寄存器的建立時(shí)間和保持時(shí)間。如下圖4是AD9709芯片的接口時(shí)序圖,CLK2是時(shí)鐘信號(hào),WRT2是類(lèi)似寫(xiě)使能的信號(hào),一般與時(shí)鐘CLK保持一致即可,DATA IN是FPGA個(gè)AD9709芯片的八位數(shù)字信號(hào),而IOUTA OR IOUTB是DAC芯片的兩路模擬輸出信號(hào),與本次時(shí)序分析無(wú)關(guān)。建立時(shí)間是指數(shù)據(jù)必須在時(shí)鐘上升沿之前到達(dá)的一段時(shí)間,所以下圖中ts就是AD9709接口寄存器建立時(shí)間。保持時(shí)間是指數(shù)據(jù)必須在時(shí)鐘上升沿之后保持的一段時(shí)間,所以下圖中tH就是AD9709接口寄存器的保持時(shí)間。

圖4 AD9709接口時(shí)序圖

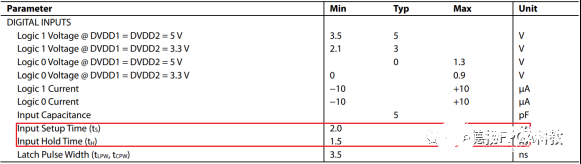

在根據(jù)芯片手冊(cè)的數(shù)據(jù)表查的上圖4中對(duì)應(yīng)的時(shí)間,如下圖5所示,tS的最小值為2.0ns,故建立時(shí)間為2.0ns,保持時(shí)間tH為1.5ns。能夠?qū)Ω拍罾斫猓还苁鞘裁葱酒伎梢愿鶕?jù)芯片手冊(cè)的接口時(shí)序圖得知接口寄存器的建立時(shí)間和保持時(shí)間,后續(xù)時(shí)序約束可以直接使用該參數(shù)。

圖5 AD9709芯片時(shí)間參數(shù)

4.3 源同步-DDR(查手冊(cè)方法)

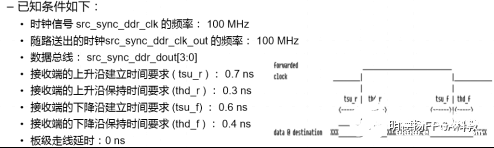

DDR其實(shí)就是SDRAM的升級(jí)版,為了提高數(shù)據(jù)傳輸效率,DDR在時(shí)鐘的上升沿和下降沿都對(duì)數(shù)據(jù)采樣。同樣可以查手冊(cè)得到接口寄存器的建立時(shí)間、保持時(shí)間,由于在時(shí)鐘上升沿和下降沿都在采集數(shù)據(jù),在這兩個(gè)邊沿都會(huì)存在建立時(shí)間和保持時(shí)間的要求,例如:

圖6 DDR接口示意圖

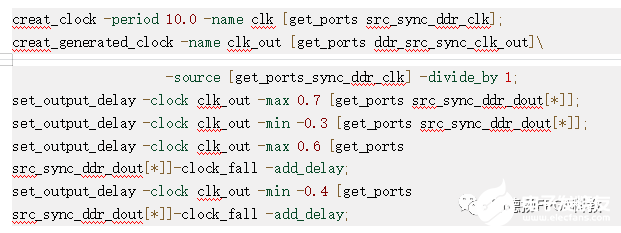

如上圖6要求上升沿建立時(shí)間tsu_r為0.7ns,上升沿的保持時(shí)間thd_r為0.3ns,下降沿的建立時(shí)間tsu_f為0.6ns,下降沿的保持時(shí)間thd_f為0.4ns。進(jìn)行IO約束之前,一般都會(huì)先約束一個(gè)生成時(shí)鐘,目的在于告訴綜合軟件該接口信號(hào)以哪個(gè)時(shí)鐘信號(hào)為標(biāo)準(zhǔn),便于后續(xù)約束直接使用。根據(jù)理論知識(shí),如果時(shí)鐘線與數(shù)據(jù)信號(hào)線的PCB走線做了等長(zhǎng)處理,那么源同步的最大延遲為下游器件的建立時(shí)間,最小延遲為0減去下游器件的保持時(shí)間。所以該DDR上升沿最大延遲0.7ns,最小延遲為0-0.3ns=0.3ns,下降沿最大延遲0.6ns,最小延遲是-0.4ns。上述約束轉(zhuǎn)換成TCL代碼如下所示:

注意這個(gè)clock_for下降沿的時(shí)候,要加上-add_delay。上面的六句約束中的前面兩句時(shí)鐘約束不是一定存在的,這兩句與前面的時(shí)鐘約束方式是一樣的,后面四句set_output_delay用于約束輸出接口信號(hào)所對(duì)應(yīng)的最大和最小輸出延遲,帶有clock for的表示以時(shí)鐘的下降沿作為參考點(diǎn),從而完成對(duì)DDR輸出接口信號(hào)的約束。

有的讀者會(huì)注意到input delay 有個(gè)什么叫中心對(duì)齊的,為什么這里就沒(méi)有了?因?yàn)?input delay 是靠測(cè)量的方式去得到的,而output delay是查數(shù)據(jù)手冊(cè)的方式獲得的數(shù)據(jù)。那么他的邊緣這個(gè)點(diǎn)的時(shí)候,就不不可能會(huì)抖動(dòng)。在下降沿的時(shí)候,在之前會(huì)穩(wěn)定,穩(wěn)定多久,之后會(huì)穩(wěn)定多久,因此他一定是這么穩(wěn)這樣一個(gè)情況的啊,他會(huì)把這個(gè)實(shí)際參數(shù)要求給你啊,所以沒(méi)有什么邊緣對(duì)齊和中心對(duì)齊的情況。我們從查數(shù)據(jù)手冊(cè)就會(huì)查到這幾個(gè)參數(shù),然后進(jìn)行配置就可以了啊。還有一點(diǎn)就是對(duì)于我們的板級(jí)延時(shí)的一般情況下呢,如果我們硬件做的好的板,這件事是不需要考慮的。也就是說(shuō)我們的output delay 一般呢就是設(shè)置它的鑒定時(shí)間啊,就是從手冊(cè)里面得到它鑒定時(shí)間和保質(zhì)時(shí)間這兩個(gè)參數(shù)。然后根據(jù)它公式直接就是配置就可以了啊,所以它output delay 的方式相對(duì)比較簡(jiǎn)單。

第5節(jié) 總結(jié)與建議

根據(jù)經(jīng)驗(yàn),按照順序去索引,找到對(duì)應(yīng)的情況,按要求進(jìn)行約束。比如說(shuō)這個(gè)端口是屬于上面三種情況中的哪一種,就按照那一種進(jìn)行配置,進(jìn)行約束就可以了。

input delay 、output delay就是告訴綜合工具現(xiàn)在的實(shí)際情況。告訴綜合軟件FPGA下游器件的情況、要求是什么,綜合軟件得知這些參數(shù)后,結(jié)合自身的參數(shù),在對(duì)設(shè)計(jì)進(jìn)行布局、布線時(shí)就會(huì)去考慮滿足下游器件的建立時(shí)間和保持時(shí)間要求。如果延遲時(shí)間過(guò)長(zhǎng),可以通過(guò)減小內(nèi)部走線的延遲,或者采用更加接近芯片管腳的觸發(fā)器去實(shí)現(xiàn)設(shè)計(jì),減小輸出延遲來(lái)達(dá)到目的。如果延遲過(guò)短導(dǎo)致下游器件保持時(shí)間不滿足,綜合軟件可以通過(guò)增加走線延遲等增大輸出延遲時(shí)間的方式滿足下游器件保持時(shí)間的要求。總之,只要添加合理的約束,告知綜合軟件下游器件的延遲要求,綜合軟件就可以通過(guò)調(diào)節(jié)內(nèi)部觸發(fā)器的布局、走線來(lái)滿足下游器件的建立時(shí)間和保持時(shí)間的要求,從而達(dá)到約束的目的。這就是 output delay 一個(gè)配置方式,相對(duì)比較簡(jiǎn)單。

審核編輯:湯梓紅

-

dac

+關(guān)注

關(guān)注

43文章

2386瀏覽量

193149 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132920 -

時(shí)序約束

+關(guān)注

關(guān)注

1文章

118瀏覽量

13637

發(fā)布評(píng)論請(qǐng)先 登錄

VIVADO時(shí)序約束及STA基礎(chǔ)

FPGA時(shí)序約束之衍生時(shí)鐘約束和時(shí)鐘分組約束

時(shí)序約束與時(shí)序分析 ppt教程

時(shí)序約束用戶指南

FPGA時(shí)序約束分析余量

時(shí)序約束中如何精確找到匹配的template?

FPGA設(shè)計(jì)之時(shí)序約束

詳解FPGA的時(shí)序input delay約束

FPGA的時(shí)序input delay約束

創(chuàng)建輸入輸出接口時(shí)序約束的竅門(mén)

set_output_delay的本質(zhì)是什么?淺談set_ouput_delay時(shí)序

時(shí)序約束連載01~output delay約束

時(shí)序約束連載01~output delay約束

評(píng)論