如果您已經在使用全新速度文件運行時序,而且 OSERDES CLK 和 CLKDIV 或者 IDDR CLK 和 CLK_B 之間有歪斜違規,接下來幫助解決歪斜違規問題的步驟已在本答復記錄中歸檔。

提供幾個解決方案:

推薦的解決方案:將您的項目遷移至 Vivado 2016.4,將時鐘拓撲更新至本答復記錄所描述的推薦拓撲并運行正常綜合及實現流程。

Vivado 2016.4 可在時序分析中自動報告 OSERDES 和 IDDR 的歪斜檢查情況。

第二種解決方案:更新時鐘拓撲后為您的項目繼續使用較早的 Vivado 版本,包括運行綜合及實現方案。 使用本答復記錄附帶的 Tcl 腳本 (reportIOSERDES.tcl) 報告有關 OSERDES 及 IDDR 的歪斜檢查。 使用 Vivado 2016.4 在已布線的 DCP 上運行時序簽收 (report_timing_summary),并修復剩余的歪斜違規問題(查看(68266))。

第三種解決方案:升級時鐘拓撲后,繼續使用帶有相應速度文件補丁的較早 Vivado 版本(僅限于某些 Vivado 版本,按需提供),包括運行綜合及實現方案。 使用本答復記錄附帶的 Tcl 腳本 (reportIOSERDES.tcl) 報告有關 OSERDES 及 IDDR 的歪斜檢查。

OSERDES CLK 至 CLKDIV 歪斜

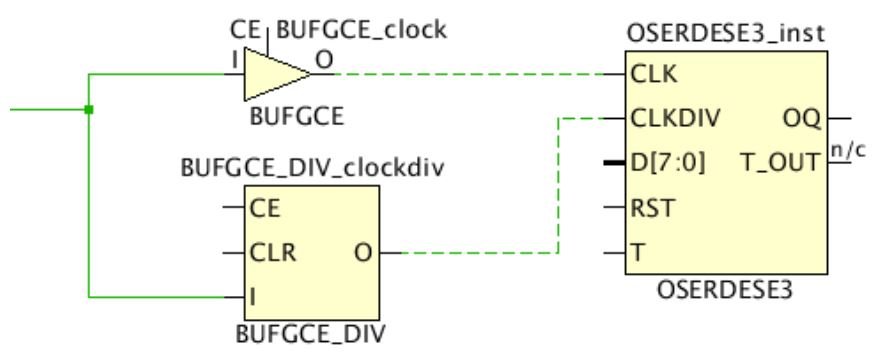

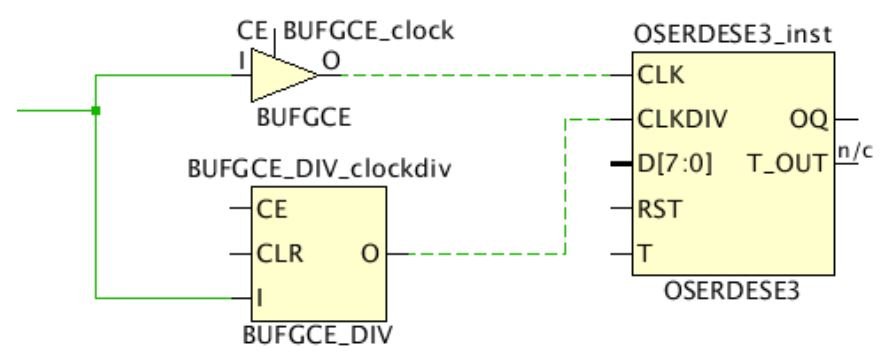

OSERDESE3 的最佳時鐘拓撲如下圖所示。

MMCME3 的 CLKOUT 應并行驅動兩個 BUFGCE_DIV,這可使用一個 BUFGCE_DIV 的分頻功能創建較慢的 CLKDIV。

注意,也不一定就需要驅動高速時鐘 (CLK) 的全局緩沖器為 BUFGCE_DIV 單元。如果缺乏 BUFGCE_DIV,它也可以是 BUFGCE。

使用 MMCME3 的多組輸出創建 CLK 和 CLKDIV 時,請查看確保符合歪斜要求。

圖:推薦的時鐘拓撲

請注意:因為 BUFGCE_DIV 正在使用被下分頻的較高頻率時鐘。

因此,架構邏輯必須使用圖(支持 BUFGCE_DIV 的架構時鐘)中所示的 BUFGCE_DIV 驅動。

圖:支持 BUFGCE_DIV 的架構時鐘

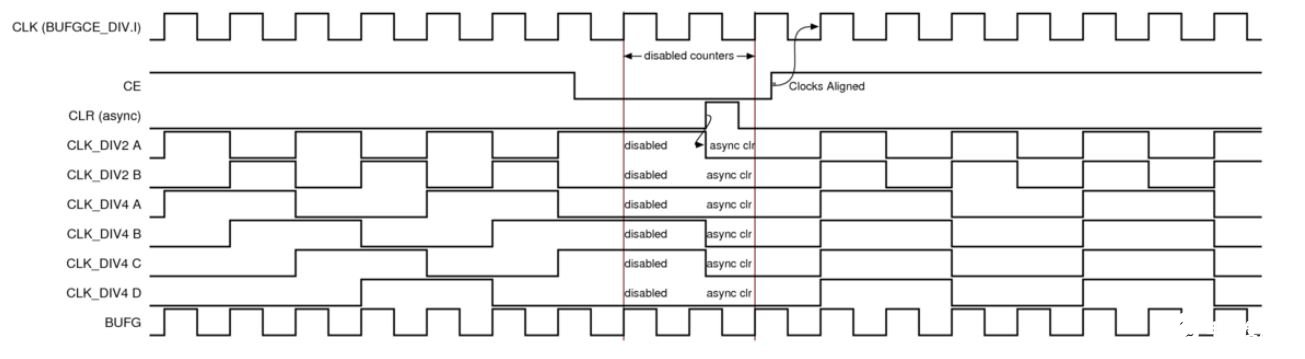

如圖所示:BUFGCE_DIV 對齊,BUFGCE_DIVIDE = 2 或者 4 個計數器可以在不同的時間啟動。

CLK_DIV2 A 和 CLK_DIV2 B 進行 2 分頻時出現了兩個對齊。同樣,進行 4 分頻時,CLK_DIV4 A/B/C/D 出現了 4 個可能的對齊。

計數器可通過使用 CLR 和 CE 輸入與既定的時鐘邊緣對齊。

圖:BUFGCE_DIV 對齊

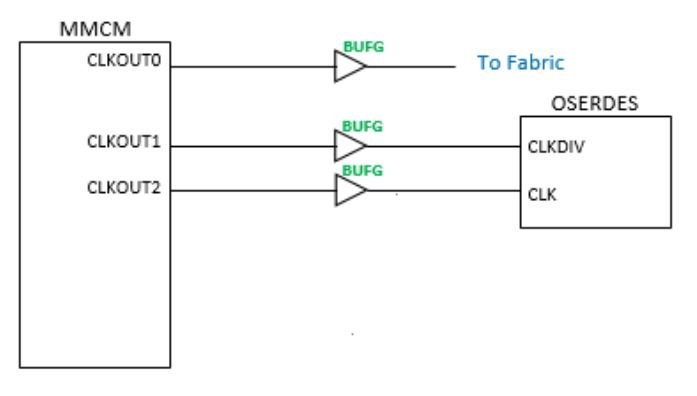

此外,如果您需要 MMCM 輸出為相位對齊(就是 CLKOUTx_PHASE)而且無法應用 correctcontrols 控制圖(BUFGCE_DIV 對齊)的時序,您可以使用 aseparate BUFG 時鐘緩沖器進行架構連接。

在支持 MMCM 時鐘輸出的架構時鐘使用 3 個 MMCM 輸出的圖中。CLKOUT0 可驅動架構邏輯(另外一個 MMCM CLKOUT1)來驅動 OSERDES CLKDIV 并驅動另外一個 MMCM CLKOUT2 來驅動 OSERDES CLK。

OSERDES 的 CLK 及 CLKDIV 端口由只連接至 ERDES 的 BUFG 驅動,將具有類似的加載/布線。此外,只要布線終點類似,CLKOUT1 和 CLKOUT2 也可用于其它組件原語(ISERDES、IDELAY、ODELAY、IDELAYCTRL)。

圖:支持 MMCM 時鐘輸出的架構時鐘

在 支持 MMCM 時鐘輸出的架構時鐘圖中, 時鐘輸出分頻設置將是 DATA_WIDTH 的比率,這樣:

CLKOUT0_DIVIDE_F = CLKOUT2_DIVIDE * DATA_WIDTH / 2

CLKOUT1_DIVIDE = CLKOUT2_DIVIDE * DATA_WIDTH / 2

輸出來自 MMCM,因此實現既定相移時,MMCM 只會鎖死,在這種情況下可以由 CLKOUT__PHASE 定義。

CLOCK_DELAY_GROUP

如果設計仍然無法滿足要求,下一步就得嘗試減少 CLK 與 CLKDIV 引腳之間的歪斜,將一個 CLOCK_DELAY_GROUP 分配給網絡。

這可讓 Vivado 實現工具平衡兩個時鐘網絡。下面是 CLOCK_DELAY_GROUP 的一個示例:

set_property CLOCK_DELAY_GROUP SERDES_X2Y2 [get_nets of [get_pins BUFGCE_DIV_clk_inst/O]]

set_property CLOCK_DELAY_GROUP SERDES_X2Y2 [get_nets of [get_pins BUFGCE_DIV_clkdiv_inst/O]]

USER_CLOCK_ROOT

除了 CLOCK_DELAY_GROUP 屬性外,您還可使用 USER_CLOCK_ROOT 屬性強制對時鐘緩沖器驅動的時鐘進行時鐘根定位。查看以下 USER_CLOCK_ROOT 示例:

set_property USER_CLOCK_ROOT X2Y3 [get_nets of [get_pins BUFGCE_DIV_clk_inst/O]]

set_property USER_CLOCK_ROOT X2Y3 [get_nets of [get_pins BUFGCE_DIV_clkdiv_inst/O]]

ISERDES CLK 至 CLKDIV 歪斜:

對 ISERDES CLK 和 CLKDIV 沒有歪斜要求,但就 OSERDES 而言,所推薦的時鐘拓撲將是相同的。

使用一個并列驅動兩個 BUFGCE_DIV 的 MMCM CLKOUT,這可使用一個 BUFGCE_DIV 的分頻功能創建更慢的 CLKDIV。

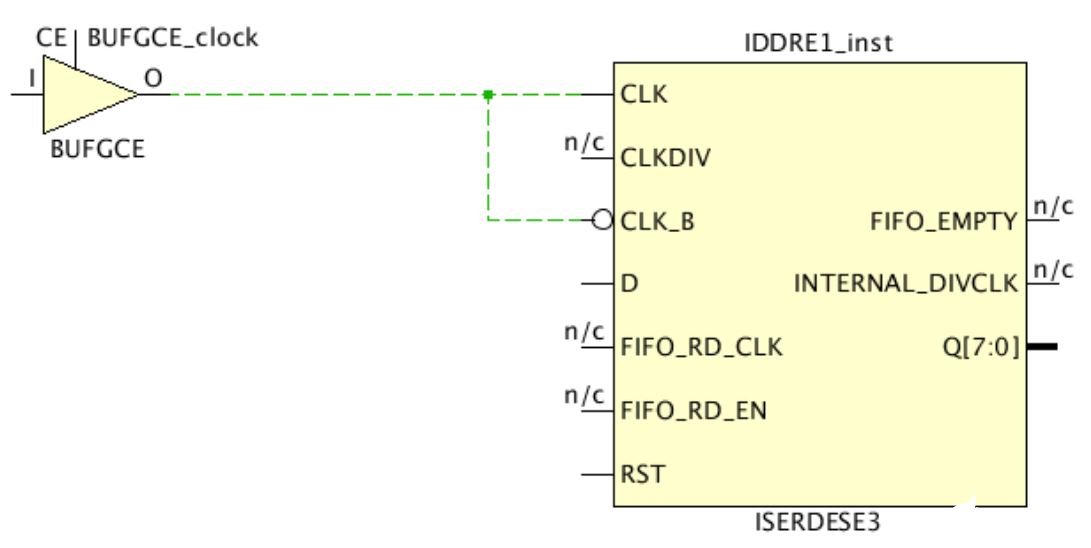

IDDRE1 C 至 CB 以及 ISERDES CLK 至 CLK_B 歪斜

IDDR(和 ISERDES)CLK 和 CLK_B 的最佳時鐘拓撲就是使用相同的網絡驅動兩個引腳并使用局部求逆創建反相時鐘。查看下圖示例。

查看(68331),了解有關 Vivado 時序歪斜檢查的詳細信息,解決有關專屬時鐘組約束的歪斜檢查問題。

審核編輯:湯梓紅

-

緩沖器

+關注

關注

6文章

2048瀏覽量

46957 -

計數器

+關注

關注

32文章

2291瀏覽量

96334 -

時鐘

+關注

關注

11文章

1895瀏覽量

133128 -

Vivado

+關注

關注

19文章

834瀏覽量

68647

發布評論請先 登錄

基于LM12CLK的100W音頻放大器電路圖

FPGA設計之Verilog中clk為什么要用posedge而不用negedge?

如何應用CLK和RSTn?

clk的延時函數最小延時是多少?

時鐘抖動(CLK)和相位噪聲之間的轉換

CLK233型金屬化聚酯薄膜電容器

使用51單片機實現ADC0808A-D虛擬CLK的仿真文件免費下載

使用51單片機實現ADC0808查詢方式AD ALE輸出CLK的仿真文件

UG-371:AD7492 1.25 MSPS評估板,16 mW內部REF和CLK,12位并行ADC

STM8L151C8單片機學習例程(2)——CLK切換

CLK-104a/b 板使用 Renesas RF-PLL 和 RF-Synthesizer 解決方案手冊

CLK-104a/b 板使用 Renesas RF-PLL 和 RF-Synthesizer 解決方案手冊

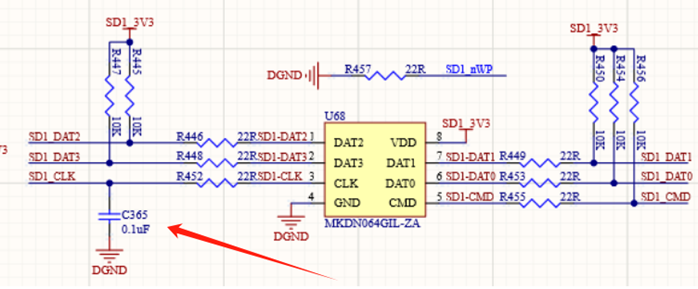

SD NAND的CLK引腳的注意事項和走線規范

如何減少OSERDES的CLK-CLKDIV與IDDR的CLK及CLK-CLK_B之間的歪斜

如何減少OSERDES的CLK-CLKDIV與IDDR的CLK及CLK-CLK_B之間的歪斜

評論