器件中的高功耗雖然是可以容忍的,但是在設(shè)計(jì)過(guò)程中,我們往往都在追求低功耗實(shí)現(xiàn)。上篇文章中,小編對(duì)MCU的低功耗設(shè)計(jì)有所解讀。為增進(jìn)大家對(duì)功耗的了解程度,本文將對(duì)寄存器傳輸級(jí)低功耗設(shè)計(jì)方法予以介紹。

除了芯片的速度和面積等,人們對(duì)低功耗的期望也越來(lái)越高,因而在IC設(shè)計(jì)中加入低功耗設(shè)計(jì)非常必要。寄存器傳輸級(jí)的低功耗設(shè)計(jì)對(duì)降低整個(gè)芯片的功耗作用非常顯著,本文討論的三種寄存器傳輸級(jí)低功耗設(shè)計(jì)方法,經(jīng)驗(yàn)證對(duì)動(dòng)態(tài)功耗的降低很有效。

自集成電路問(wèn)世以來(lái),設(shè)計(jì)者在單個(gè)芯片上集成的晶體管的數(shù)量呈現(xiàn)出令人驚訝的增長(zhǎng)速度。近30年,集成電路的發(fā)展一直遵循著“摩爾定律”:集成在芯片上的晶體管的數(shù)量每18個(gè)月就翻一番,芯片成本也相應(yīng)下降。

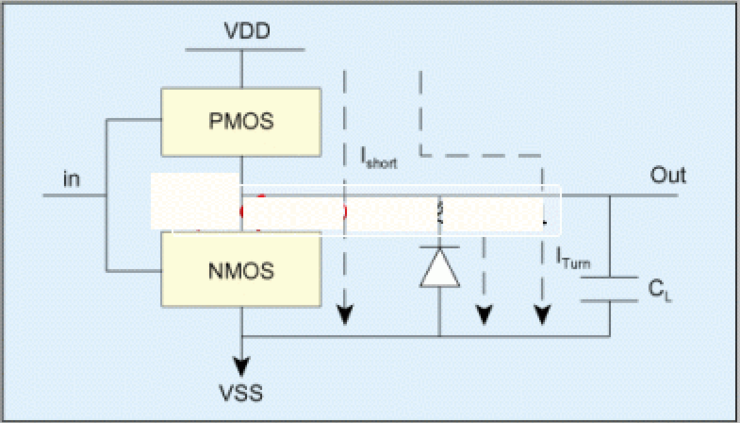

圖1:CMOS電路功耗的主要來(lái)源是動(dòng)態(tài)功耗,由開關(guān)電流和短路電流造成。

在半導(dǎo)體工藝水平不斷進(jìn)步的同時(shí),以電池供電的手持設(shè)備和膝上電腦也迅速普及,系統(tǒng)的功耗有時(shí)已經(jīng)成為系統(tǒng)設(shè)計(jì)首要考慮的因素,因此,低功耗設(shè)計(jì)成為發(fā)展移動(dòng)系統(tǒng)必然要解決的問(wèn)題。

集成電路的低功耗設(shè)計(jì)分為系統(tǒng)級(jí)、寄存器傳輸級(jí)、門級(jí)、電路級(jí)四個(gè)層次,而在這其中,寄存器傳輸級(jí)的低功耗設(shè)計(jì)對(duì)優(yōu)化整個(gè)系統(tǒng)功耗的貢獻(xiàn)達(dá)到20%-50%,這是非常巨大的比例。因而,在寄存器傳輸級(jí)進(jìn)行低功耗設(shè)計(jì)是非常值得,也是很有必要的。

集成電路中功耗的來(lái)源

目前,CMOS工藝在集成電路特別是數(shù)字IC中應(yīng)用得很普遍。由于CMOS電路在輸入穩(wěn)定的時(shí)候總有一個(gè)管子截止,所以它的靜態(tài)功耗在理想情況下應(yīng)該是零,但這并不代表靜態(tài)功耗真的為零,實(shí)際上CMOS電路的靜態(tài)功耗就是指電路中的漏電流(這里不考慮亞閾值電流)。

CMOS電路功耗的主要來(lái)源是動(dòng)態(tài)功耗,它由兩部分組成:開關(guān)電流和短路電流。

所以,整個(gè)CMOS電路的功耗為:其中,PTurn是開關(guān)電流ITurn產(chǎn)生的動(dòng)態(tài)功耗;Pshort是動(dòng)態(tài)情況下P管和N管同時(shí)導(dǎo)通時(shí)的短路電流Ishort產(chǎn)生的動(dòng)態(tài)功耗;而Pleakage 是由擴(kuò)散區(qū)和襯底之間的反向偏置漏電流Ileakage產(chǎn)生的靜態(tài)功耗。如圖1所示。

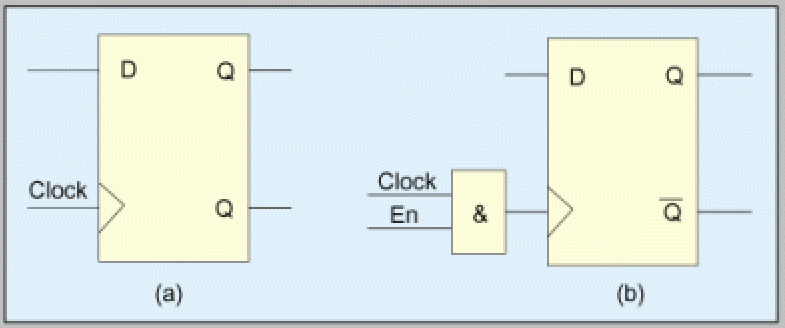

圖2a:傳統(tǒng)的設(shè)計(jì)。圖2b:增加了門控時(shí)鐘的設(shè)計(jì)。

在這三項(xiàng)中PTurn大約占電路功耗的80% ,因而這里就只考慮開關(guān)電流ITurn所產(chǎn)生的動(dòng)態(tài)功耗PTurn。ITurn是這樣產(chǎn)生的:在CMOS電路,當(dāng)輸入為“0”時(shí),PMOS導(dǎo)通,電源通過(guò)PMOS向負(fù)載電容充電;而當(dāng)電路輸入為“1” 時(shí),負(fù)載電容又會(huì)通過(guò)NMOS向地放電。ITurn就是不斷對(duì)負(fù)載電容充放電所產(chǎn)生的開關(guān)電流。

一個(gè)CMOS反相器由開關(guān)電流引起的平均動(dòng)態(tài)功耗是:PTurn=CLVDD2f其中,CL是負(fù)載電容,VDD是電路的電壓,f是時(shí)鐘頻率。所以,要想降低電路的功耗就應(yīng)該降低電路的電壓和頻率。

寄存器傳輸級(jí)的低功耗設(shè)計(jì)

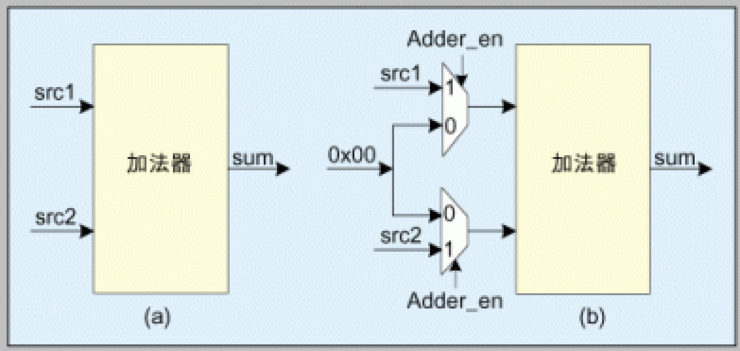

圖3a:最基本的加法器設(shè)計(jì)。圖3b:采用操作數(shù)隔離方法設(shè)計(jì)的加法器。

寄存器傳輸級(jí)的低功耗設(shè)計(jì)方法有很多種,本文只列舉三種最為常用的設(shè)計(jì)方法:門時(shí)鐘、操作數(shù)隔離及存儲(chǔ)器分區(qū)訪問(wèn)。

1.門控時(shí)鐘

從上面的討論知道,CMOS電路的功耗是和頻率有著密切關(guān)系的,因此動(dòng)態(tài)的關(guān)閉處于空閑狀態(tài)的時(shí)鐘具有明顯的節(jié)電效果。

圖2a是傳統(tǒng)的設(shè)計(jì):系統(tǒng)的時(shí)鐘直接接到D觸發(fā)器的時(shí)鐘輸入端,不管什么情況,只要輸入的Clock翻轉(zhuǎn),觸發(fā)器就會(huì)工作,整個(gè)系統(tǒng)也一直不斷的運(yùn)行。而圖2b是增加了門控時(shí)鐘的設(shè)計(jì):當(dāng)系統(tǒng)正常工作時(shí),譯碼出來(lái)的En信號(hào)為高,則觸發(fā)器可以正常鎖存數(shù)據(jù);當(dāng)系統(tǒng)處于空閑狀態(tài)時(shí),把En信號(hào)清零,這樣,由于給觸發(fā)器的Clock一直保持零,不會(huì)發(fā)生翻轉(zhuǎn),所以觸發(fā)器不會(huì)鎖存新的數(shù)據(jù),整個(gè)系統(tǒng)被掛起,系統(tǒng)將進(jìn)入低功耗模式。

在電路中加入門控時(shí)鐘很容易,可以用Verilog直接在描述中加入,也可以通過(guò)Synopsys的工具PowerCompile自動(dòng)加入。通過(guò)加入門控時(shí)鐘,系統(tǒng)可以有選擇的停止不相關(guān)模塊的時(shí)鐘,以最大程度的節(jié)省動(dòng)態(tài)功耗。

2.操作數(shù)隔離

這種方法主要是對(duì)系統(tǒng)中的算術(shù)、邏輯運(yùn)算模塊進(jìn)行低功耗設(shè)計(jì),其主要思想就是:在不進(jìn)行算術(shù)、邏輯運(yùn)算的時(shí)候,使這些模塊的輸入保持“0”,不讓操作數(shù)進(jìn)來(lái),輸出結(jié)果不會(huì)翻轉(zhuǎn);而如果進(jìn)行這方面的運(yùn)算時(shí),再將它們打開。

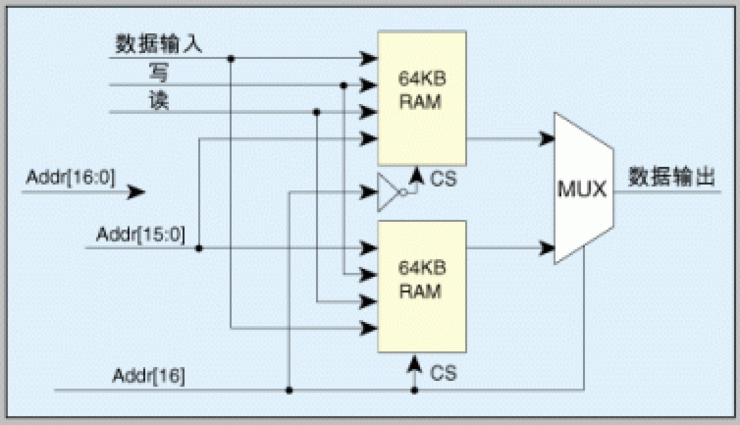

圖4:存儲(chǔ)器分塊訪問(wèn)實(shí)例。

這種方法在很多人看來(lái)是理所當(dāng)然的,認(rèn)為就應(yīng)該是這樣設(shè)計(jì)。然而在實(shí)際中,設(shè)計(jì)者一方面關(guān)心模塊的功能,另一方面迫于設(shè)計(jì)時(shí)間的壓力,所以很多設(shè)計(jì)中的細(xì)節(jié)沒(méi)有考慮。如圖3a,一個(gè)加法器的兩個(gè)輸入端沒(méi)有經(jīng)過(guò)任何邏輯直接進(jìn)入加法器,系統(tǒng)不管是否需要加法運(yùn)算,加法器都一直工作著,輸出不斷翻轉(zhuǎn)著,這對(duì)系統(tǒng)的動(dòng)態(tài)功耗是很大的浪費(fèi),而且數(shù)據(jù)總線越寬浪費(fèi)的功耗越多;圖3b 則用操作數(shù)隔離的方法進(jìn)行設(shè)計(jì):當(dāng)系統(tǒng)不需要加法運(yùn)算的時(shí)候,Adder_en信號(hào)為“0”,則加法器的兩個(gè)輸入端都保持“0”, 其輸出不會(huì)發(fā)生任何翻轉(zhuǎn),不會(huì)產(chǎn)生動(dòng)態(tài)功耗,而如果需要進(jìn)行加法運(yùn)算時(shí),Adder_en變成“1”,加法器正常工作。

當(dāng)對(duì)系統(tǒng)里所有的算術(shù)、邏輯運(yùn)算單元都用上這種方法必然會(huì)對(duì)系統(tǒng)的動(dòng)態(tài)功耗有很大的優(yōu)化,在芯片面積方面,如圖3b所示的,所增加的邏輯僅僅是幾個(gè)多路器而已。

3.存儲(chǔ)器分塊訪問(wèn)

一個(gè)系統(tǒng)里少不了存儲(chǔ)器,存儲(chǔ)器的功耗在整個(gè)系統(tǒng)里所占的比例不可忽視。因而降低存儲(chǔ)器的功耗,對(duì)于整個(gè)芯片系統(tǒng)的功耗優(yōu)化很有幫助。

這里提出一種叫做存儲(chǔ)器分塊訪問(wèn)的方法來(lái)降低存儲(chǔ)器的功耗。主要思想是:將系統(tǒng)所需要一定容量的存儲(chǔ)器分成兩塊,然后用高位地址線進(jìn)行片選譯碼。結(jié)合下面的實(shí)例:

假設(shè)一個(gè)系統(tǒng)需要128K的RAM,如圖4所示,我們選用兩塊64KB的RAM。CPU給出了17位地址線,其中低16位地址線直接提供給兩個(gè)RAM,最高位地址線接到下面RAM的片選端CS,而這根地址線經(jīng)過(guò)一個(gè)反相器接到另一個(gè)RAM的片選端。通過(guò)這種方法,不管從CPU 出來(lái)的什么樣的地址,則每次只會(huì)選中一個(gè)64KB的RAM。如果采用單塊128KB的RAM,則每次都要選中一塊128KB的RAM。眾所周知,一塊64KB RAM的功耗要遠(yuǎn)小于一塊128KB RAM的功耗。這樣從存儲(chǔ)器這一方面,又為系統(tǒng)節(jié)省了功耗。

功耗和面積永遠(yuǎn)是相矛盾的,如果想要降低系統(tǒng)的功耗,必然要加上一些控制邏輯來(lái)進(jìn)行功耗優(yōu)化,而這部分邏輯會(huì)增加芯片的面積,所以在功耗和面積之間就要有個(gè)折衷。上面的三種寄存器傳輸級(jí)的低功耗設(shè)計(jì),不會(huì)增加很多邏輯,因而對(duì)芯片面積的影響不大。而經(jīng)過(guò)了這三種低功耗設(shè)計(jì),使整個(gè)系統(tǒng)動(dòng)態(tài)功耗的改善很明顯。例如,使用功耗仿真工具powermill對(duì)一款SIM卡芯片設(shè)計(jì)進(jìn)行管級(jí)功耗仿真,這里采用的是華杰的0.25um的標(biāo)準(zhǔn)單元庫(kù),表1是優(yōu)化前后功耗及芯片面積的對(duì)比。

可以看到,經(jīng)過(guò)低功耗設(shè)計(jì)后的芯片平均動(dòng)態(tài)電流比優(yōu)化前降了16%,然而優(yōu)化前后芯片的面積沒(méi)有發(fā)生改變,因而,上面的三種設(shè)計(jì)方法對(duì)于降低系統(tǒng)動(dòng)態(tài)功耗是非常有效的。

審核編輯:湯梓紅

-

寄存器

+關(guān)注

關(guān)注

31文章

5429瀏覽量

123816 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7643瀏覽量

166738 -

晶體管

+關(guān)注

關(guān)注

77文章

9997瀏覽量

141069 -

低功耗

+關(guān)注

關(guān)注

11文章

2763瀏覽量

104685

發(fā)布評(píng)論請(qǐng)先 登錄

【KL25】低功耗定時(shí)器之寄存器操作

STM32低功耗

430低功耗問(wèn)題

Stm32的低功耗模式介紹

可以在低功耗模式下使用高通濾波器讀取REFERENCE寄存器嗎

寄存器傳輸級(jí)低功耗設(shè)計(jì)方法

MAX11120-MAX11128低功耗,逐次逼近寄存器串行ADC

在學(xué)習(xí)低功耗設(shè)計(jì)看看如何解決寄存器傳輸功耗問(wèn)題

芯片RTL設(shè)計(jì)中如何做到低功耗設(shè)計(jì)

MCU學(xué)習(xí)筆記_STM32低功耗模式概述

STM32超低功耗進(jìn)階之電源管理庫(kù)函數(shù)(一)

門控時(shí)鐘實(shí)現(xiàn)低功耗的原理

寄存器陣列低功耗設(shè)計(jì)方案

在學(xué)習(xí)低功耗設(shè)計(jì)?看看如何解決寄存器傳輸功耗問(wèn)題

在學(xué)習(xí)低功耗設(shè)計(jì)?看看如何解決寄存器傳輸功耗問(wèn)題

評(píng)論