隨著信號(hào)速率-AMI模型在信號(hào)完整性仿真中應(yīng)用越來(lái)越多,本文主要介紹了IBIS-AMI模型的基礎(chǔ)知識(shí)和建模方案。IBIS-AMI模型建模一般采用SystemVue或者ADS這兩個(gè)工具都能分別完成。

IBIS 模型

IBIS模型出現(xiàn)之前,系統(tǒng)仿真使用的模型主要是Spice模型,SPICE (Simulation Program with IntegratedCircuit Emphasis)是一種通用的電路模擬語(yǔ)言,其對(duì)應(yīng)的網(wǎng)表文件可以作為用于描述器件內(nèi)部實(shí)際電氣連接的器件模型。SPICE模型包含詳細(xì)的晶體管結(jié)構(gòu)和具體的工藝技術(shù),因此模型精度很高,但與此同時(shí),由于其包含有過(guò)多有價(jià)值的信息,多數(shù)芯片廠(chǎng)商往往不會(huì)提供SPICE模型給客戶(hù)。另外,SPICE模型是電路級(jí)仿真,其仿真時(shí)間與電路復(fù)雜度直接相關(guān),在芯片集成度越來(lái)越高、電路越來(lái)越復(fù)雜的今天,SPICE模型仿真往往計(jì)算量巨大、需要耗費(fèi)大量時(shí)間,只適用于電路級(jí)的設(shè)計(jì)者使用。

為了解決這些問(wèn)題, IBIS模型應(yīng)運(yùn)而生了

IBIS (I/O Buffer Information Specification) 是一個(gè)公開(kāi)的且已經(jīng)成為行業(yè)標(biāo)準(zhǔn)的數(shù)字電路輸入輸出建模規(guī)范。它是基于I/V、V/T曲線(xiàn)的用于描述芯片I/OBuffer行為級(jí)特性的模型,能夠反映芯片驅(qū)動(dòng)和接收的電氣特性。芯片廠(chǎng)商很容易便可以在不透露知識(shí)產(chǎn)權(quán)的同時(shí)提供給客戶(hù)IBIS模型,以便在IBIS兼容仿真器(如ADS)中使用。并且與等效電路SPICE模型相比,IBIS的仿真速度要快的多。

為了建立統(tǒng)一的IBIS 模型,EDA廠(chǎng)商、IC供應(yīng)商和最終用戶(hù)成立了一個(gè)IBIS格式制定委員會(huì),以推出并不斷修訂IBIS模型規(guī)范。

IBIS 模型雖然強(qiáng)大,但是也不能解決數(shù)字電路仿真中出現(xiàn)的所有問(wèn)題。高速串行總線(xiàn)在使用過(guò)程中經(jīng)常會(huì)出現(xiàn)一類(lèi)問(wèn)題:由于鏈路較長(zhǎng)或者由于頻率較高,而造成信號(hào)衰減過(guò)大,從而導(dǎo)致在接收端無(wú)法正確判別信號(hào),所以這類(lèi)SerDes架構(gòu)的串行總線(xiàn)芯片都會(huì)有集成均衡或加重電路,尤其是接收端通常包含較復(fù)雜的均衡電路。而普通的IBIS模型無(wú)法對(duì)這樣復(fù)雜的均衡算法電路進(jìn)行描述,

為了解決高速串行仿真在速率較高時(shí)帶來(lái)的問(wèn)題,從IBIS 規(guī)范5.0開(kāi)始,定義了新的IBIS AMI (Algorithmic Modeling Interface)模型,來(lái)實(shí)現(xiàn)IBIS模型無(wú)法描述的均衡算法功能。

AMI模型

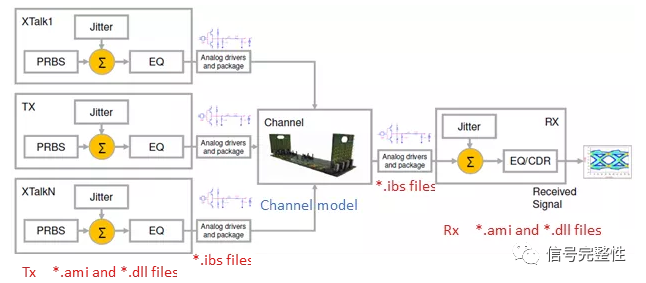

AMI(Algorithimic Model Interface)模型是IBIS協(xié)會(huì)制定的一種模型分析方法。在這一個(gè)分析方法當(dāng)中,芯片廠(chǎng)商可以利用C++代碼建立模型,描述芯片內(nèi)部功能電路的行為,然后將代碼編譯為動(dòng)態(tài)鏈接庫(kù)(.dll),從而保護(hù)芯片內(nèi)部設(shè)計(jì)的知識(shí)產(chǎn)權(quán)。對(duì)系統(tǒng)集成商而言,一旦從芯片廠(chǎng)商取得AMI模型,其開(kāi)發(fā)工程師便可以結(jié)合自己設(shè)計(jì)的通道模型搭建成高速數(shù)字傳輸系統(tǒng),通過(guò)軟件仿真來(lái)估算系統(tǒng)的眼圖(Eye Pattern)或者是誤碼率(BER),仿真時(shí)間只需數(shù)分鐘到數(shù)個(gè)小時(shí)便可完成。實(shí)踐證明使用IBIS AMI進(jìn)行仿真的結(jié)果與實(shí)際測(cè)量通常具有相當(dāng)高的吻合度,因而使用AMI模型進(jìn)行系統(tǒng)仿真儼然已經(jīng)變成整個(gè)產(chǎn)業(yè)的標(biāo)準(zhǔn)分析流程。

IBIS AMI 模型特點(diǎn)

與傳統(tǒng)模型相比,IBIS AMI模型具有以下優(yōu)點(diǎn),更符合芯片廠(chǎng)商和硬件設(shè)計(jì)者的需求:

·兼容性:不同半導(dǎo)體芯片廠(chǎng)商生成的模型可以在同一電路中仿真。

·可移植性:相同的模型可以用不同的仿真軟件來(lái)仿真分析。

· 高效率:10000000 bit的仿真可以在10 min或者更短的時(shí)間內(nèi)完成。

·靈活性:模型支持統(tǒng)計(jì)和時(shí)域(bit-by-bit)分析模式。

·可優(yōu)化:模型提供仿真控制參數(shù)(如抽頭系數(shù)等),用戶(hù)可以通過(guò)電路仿真器對(duì)各個(gè)參數(shù)進(jìn)行掃描,優(yōu)化,改善系統(tǒng)性能。

·知識(shí)產(chǎn)權(quán)保護(hù): 芯片廠(chǎng)家只提供模型算法部分的加密動(dòng)態(tài)鏈接庫(kù)文件,以避免逆向設(shè)計(jì)。

IBIS AMI 建模挑戰(zhàn)

IBIS AMI 模型由描述電氣特性的傳統(tǒng)的IBIS模型文件(*.ibs)、包含編譯后算法的動(dòng)態(tài)鏈接庫(kù)文件(*.dll/*.so)以及參數(shù)描述文檔(*.ami)三個(gè)文件共同構(gòu)成。

*.ibs 文件:

○聲明對(duì)應(yīng)的AMI 參數(shù)文件和算法可執(zhí)行文件*.dll,關(guān)鍵字為:

[Algorithmic Model]

[End Algorithmic Model]

○包含除均衡外的發(fā)射機(jī)特性:輸出電壓擺幅、輸出阻抗、轉(zhuǎn)換速度、輸出寄生參數(shù)等。

○包含除均衡外的接收機(jī)特性:輸入負(fù)載阻抗、寄生參數(shù)等。

*.ami 參數(shù)定義文件:

○[Reserved_Parameters]關(guān)鍵字中定義模型的處理流程,如:

Init_Returns_Impluse:是否有算法模型等效LTI沖激響應(yīng)(若為T(mén)RUE,可用于統(tǒng)計(jì)模式)。

GetWave_Exists:若為T(mén)RUE,算法模型為 NLTV, 可通過(guò)AMI_GetWave 函數(shù)生成輸出信號(hào)。

使用Tx_Jitter、Rx_Clock_PDF加入抖動(dòng)參數(shù)等。

○[Model_Specific] 關(guān)鍵字中把仿真器的參數(shù)傳遞給相應(yīng)的可執(zhí)行模塊。

*.dll/*.so 算法可執(zhí)行文件:編譯后的算法文件(不可讀),是真正用于信號(hào)處理的文件。Windows系統(tǒng)中使用*.dll文件,Linux系統(tǒng)中使用*.so文件。

IBIS AMI模型的建模對(duì)芯片設(shè)計(jì)人員來(lái)說(shuō)具有一定的挑戰(zhàn):需要同時(shí)具備電路知識(shí)、高速信號(hào)傳輸知識(shí)及仿真能力,以及編程能力。產(chǎn)品往往覆蓋多種協(xié)議,如PCIe, USB, SAS, SATA, HDMI等等。并且隨著產(chǎn)品的更新?lián)Q代,設(shè)計(jì)人員需要不斷地更新設(shè)計(jì),同時(shí)保證每個(gè)模型的準(zhǔn)確度,這也需要花費(fèi)大量的時(shí)間和資源。

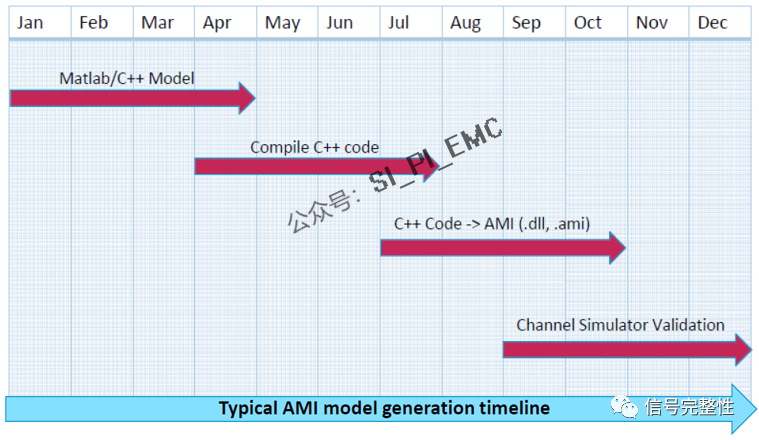

特別是對(duì)于沒(méi)有建模經(jīng)驗(yàn)的供應(yīng)商而言,第一個(gè)IBIS AMI模型的建立往往需要花費(fèi)半年到一年的時(shí)間才能得到第一代模型。而模型發(fā)布前還需要進(jìn)行反復(fù)的驗(yàn)證和測(cè)試,以確保模型精度。傳統(tǒng)的IBIS AMI建模周期如下圖所示:

傳統(tǒng)的IBIS AMI建模周期

對(duì)于系統(tǒng)工程師,及芯片廠(chǎng)商的客戶(hù)而言,相比于芯片的獲取,則可能需要等待較長(zhǎng)的時(shí)間才能獲取到對(duì)應(yīng)的精確的AMI模型。

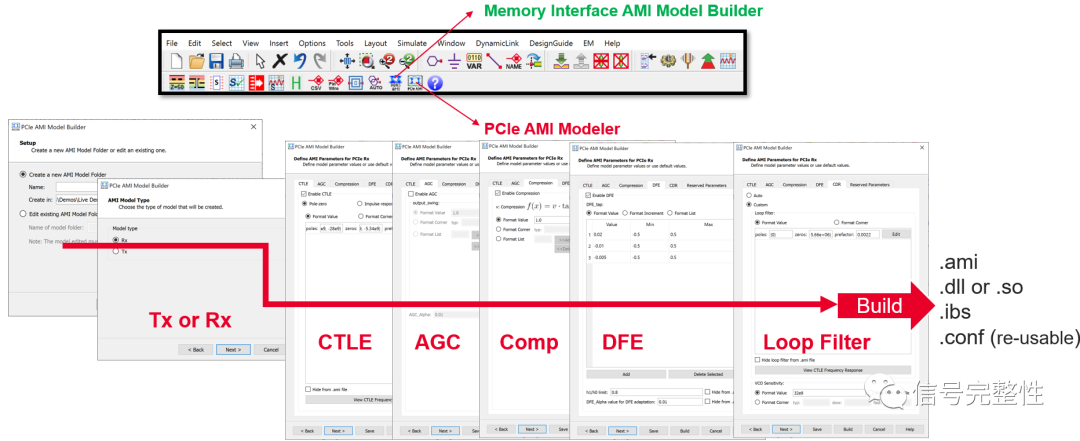

目前市場(chǎng)上能提供AMI模型建立以及測(cè)試工具的廠(chǎng)商很少,是德科技的 SystemVue以及 ADS是目前市場(chǎng)上被廣泛采用的工具。SytemVue提供了圖形化的界面以及豐富的模型庫(kù),芯片廠(chǎng)商可以在模型庫(kù)里面挑選適當(dāng)?shù)脑罱ㄗ约旱陌l(fā)射/接收電路架構(gòu),隨后即可以自動(dòng)編譯出AMI模型。ADS是業(yè)界高度認(rèn)可的高速數(shù)字電路系統(tǒng)仿真平臺(tái),同時(shí)也是支持AMI模型非常完整的工具。最新的ADS也能支持IBIS-AMI模型的建模。

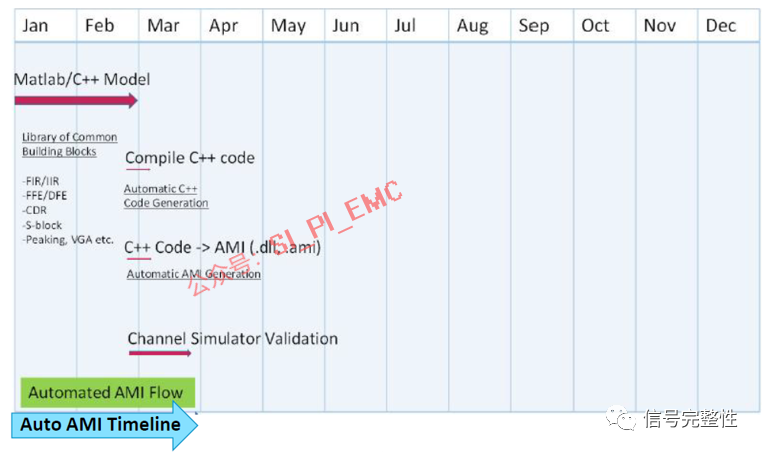

芯片廠(chǎng)商可以通過(guò)SystemVue以及ADS來(lái)加速AMI模型算法的開(kāi)發(fā)以及驗(yàn)證測(cè)試工作。系統(tǒng)集成商也可以方便的使用這兩種工具進(jìn)行仿真以及測(cè)試,從而使得建模周期大大縮短:

使用PathWave SystemVue和PathWave ADS 縮短IBIS AMI建模周期

基于PathWave SystemVue的IBIS AMI 建模流程

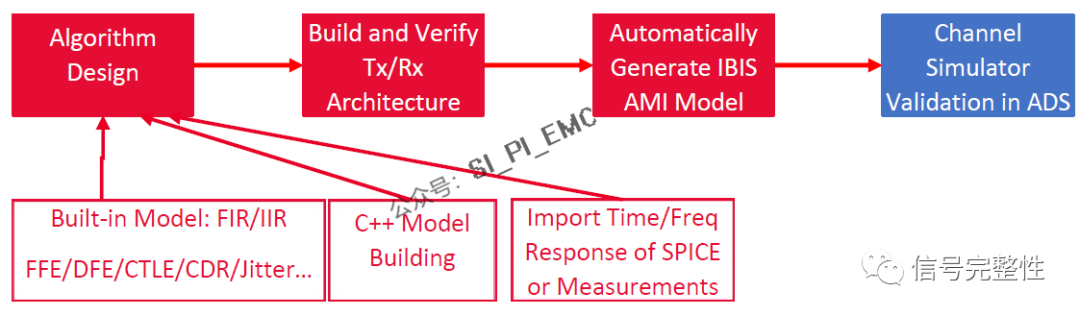

PathWave System Design, 即原SystemVue軟件,是專(zhuān)業(yè)的電子系統(tǒng)級(jí)仿真軟件,能夠?yàn)镾erDes/DDR集成電路(IC)提供常用均衡算法及其他數(shù)字信號(hào)處理模塊,一旦算法設(shè)計(jì)并優(yōu)化完成,PathWave System Design即可自動(dòng)生成通用的IBIS AMI模型。用戶(hù)可將其導(dǎo)入通道仿真工具(如PathWave ADS)進(jìn)行進(jìn)一步的驗(yàn)證,或提供給客戶(hù),幫助他們?cè)O(shè)計(jì)包含有芯片特性的系統(tǒng)。

PathWave SystemVue提供一套自動(dòng)化IBIS AMI建模流程,基于圖形界面設(shè)計(jì)。用戶(hù)可以使用軟件內(nèi)建的常用算法模型,來(lái)快速對(duì)Tx/Rx中所需的Pre-shoot/De-emphasis(預(yù)加重/去加重)、CTLE(ContinuousTime Linear Equalizer,連續(xù)時(shí)間線(xiàn)性均衡)、Adaptive DFE(Adaptive Decision Feedback Equalizer,自適應(yīng)判決反饋均衡)以及CDR(Clock Data Recovery時(shí)鐘數(shù)據(jù)恢復(fù))等進(jìn)行建模。同時(shí),用戶(hù)也可以導(dǎo)入自定義的C/C++代碼或SPICE仿真或?qū)嶋H測(cè)量得到的電路時(shí)域/頻域響應(yīng)等,來(lái)更精確地對(duì)芯片實(shí)際算法結(jié)構(gòu)進(jìn)行建模。經(jīng)過(guò)仿真驗(yàn)證后,用戶(hù)即可使用軟件提供的建模工具自動(dòng)編譯生成所需的AMI文件,以便提供給通道仿真工具(如ADS)進(jìn)行進(jìn)一步的驗(yàn)證。

IBIS AMI建模實(shí)例——SerDes模型庫(kù)及AMI 建模工具

AMI模型設(shè)計(jì)工具用于高速數(shù)字IC常用的信號(hào)處理算法設(shè)計(jì),可以在不使用AMI模型的情況下對(duì)SerDes鏈路進(jìn)行架構(gòu)優(yōu)化,同時(shí)也是用于建立IBIS AMI模型的必要模型庫(kù)。是高性能SerDes設(shè)計(jì)所必需的評(píng)估手段,幫助高速數(shù)字電路設(shè)計(jì)工程師利用物理層的信號(hào)處理手段以達(dá)到最大的互聯(lián)性能。其中也包括光纖通信中的 SerDes模型。

主要特性

·快速優(yōu)化信號(hào)處理過(guò)程。同時(shí)支持算法設(shè)計(jì)、驗(yàn)證及建模。

·在實(shí)施時(shí)無(wú)需經(jīng)歷麻煩和耗時(shí)的迭代過(guò)程。將經(jīng)過(guò)優(yōu)化的算法模型作為一個(gè)可執(zhí)行的規(guī)范,一次就成功地實(shí)施經(jīng)過(guò)優(yōu)化的體系結(jié)構(gòu)。

· AMI 是基于產(chǎn)品和架構(gòu)的模型。基于此工具能支持快速、精確、自動(dòng)化地建立模型,避免了將敏感 IP 透露出去的危險(xiǎn)。IBIS AMI 封裝程序可以確保標(biāo)準(zhǔn)一致性。

·無(wú)所有權(quán)加密。無(wú)需驗(yàn)證和保有多個(gè)版本。AMI 模型設(shè)計(jì)工具提供了“一次編程,隨處可用”的功能。

·生成您需要發(fā)給客戶(hù)的所有格式的文件:*.ibs、*.ami、*.dll(Windows 可執(zhí)行)、*.so(Linux的交叉編譯共享對(duì)象)。

·除了傳統(tǒng)的Tx/Rx模型外,還可對(duì)中間通道中繼器(Retimer/Redriver)和光纖通信鏈路進(jìn)行建模。

·可與常用示波器眼圖分析軟件(FlexDCA)進(jìn)行互操作,以便在同樣的眼圖分析算法下比對(duì)軟件仿真與硬件測(cè)試的結(jié)果。

·提供豐富的均衡算法,可取代大量編程工作。包括Blind/Adaptive FFE(預(yù)加重/去加重), CTLE線(xiàn)性時(shí)間均衡, CDR時(shí)鐘數(shù)據(jù)恢復(fù) (可調(diào)整其中PLL, VCO各項(xiàng)參數(shù)),Blind/Adaptive DFE判決反饋均衡等復(fù)雜算法,也支持導(dǎo)入時(shí)域/頻域響應(yīng)、自定義C++算法。可基于算法模型靈活設(shè)計(jì)所需功能,如非線(xiàn)性放大器等。

·支持添加抖動(dòng)參數(shù)或抖動(dòng)模型。

·支持靈活的畫(huà)圖方式,可對(duì)任意節(jié)點(diǎn)處的結(jié)果進(jìn)行時(shí)域/頻域畫(huà)圖,也可對(duì)數(shù)據(jù)進(jìn)行后處理。

·支持導(dǎo)入通道S參數(shù),通道沖激響應(yīng)/階躍響應(yīng)等以用于鏈路仿真驗(yàn)證。

·對(duì)于DDR5,提供獨(dú)家的方式支持DQ和DQS輸入。

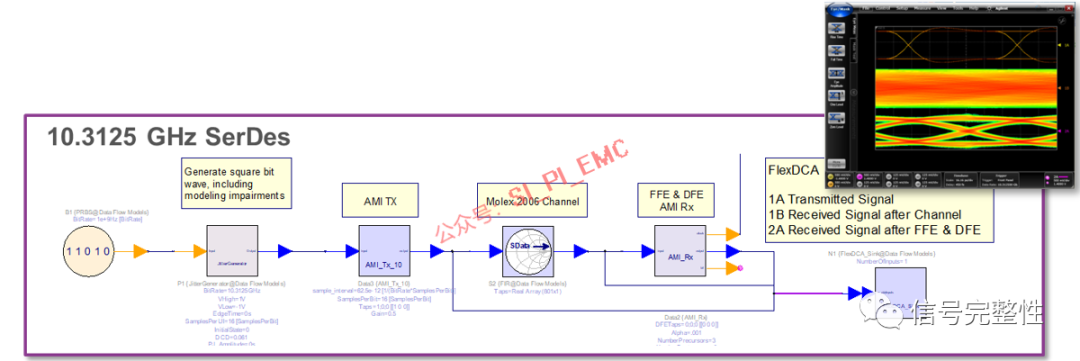

10.3125GHz SerDes 鏈路及模型示例:

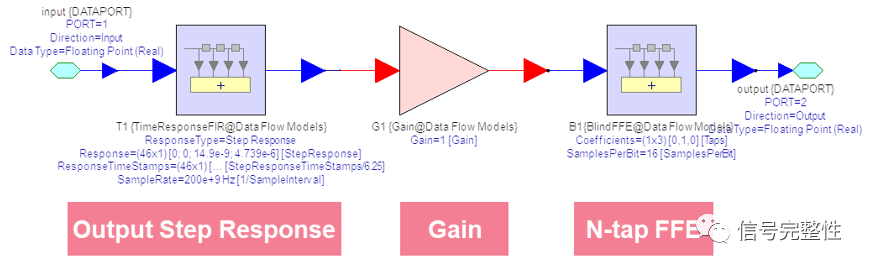

發(fā)射機(jī)模型架構(gòu)示例:

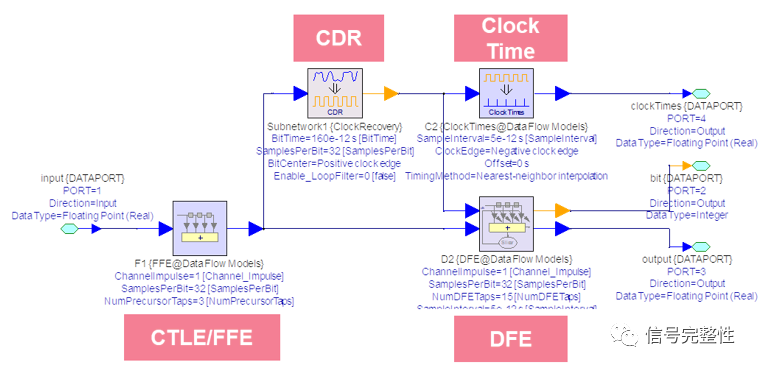

接收機(jī)模型架構(gòu)示例:

DDR5 IBIS-AMI建模

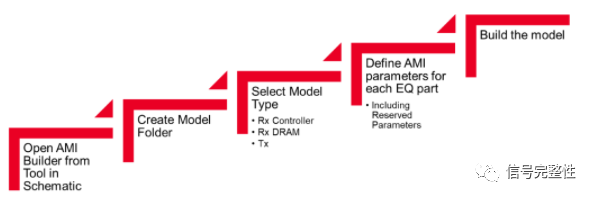

相較于串行總線(xiàn),傳輸鏈路較短且損耗較低的DDR技術(shù)以往似乎一直沒(méi)有用到均衡,但隨著DDR5速率的提高(3200MTs ~ 8400MTs),愈發(fā)嚴(yán)重的碼間干擾(ISI)等問(wèn)題使得眼圖難以張開(kāi),因此DFE等有效降低ISI的均衡算法也將應(yīng)用于DDR5產(chǎn)品中。因此IBIS AMI 模型也將用于DDR5的仿真中。在A(yíng)DS中能快速的建立DDR5的IBIS-AMI模型。其基本的建模流程如下:

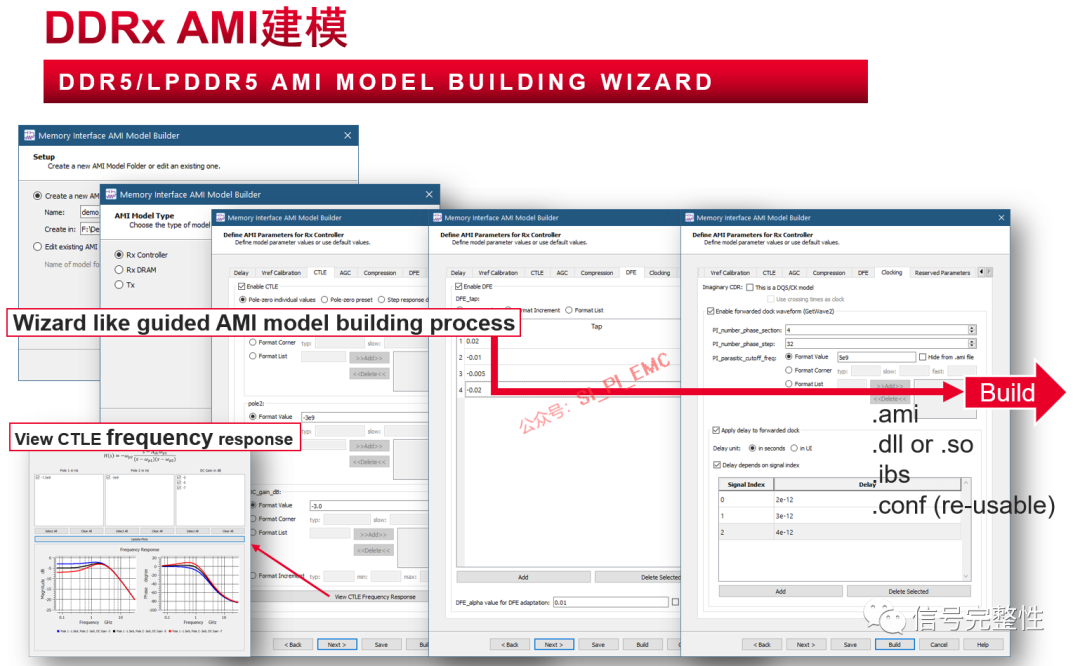

DDR5 AMI 建模向?qū)缦聢D所示:

以Rx DRAM為例,包含如下功能選項(xiàng)(均參數(shù)可控),其中對(duì)時(shí)鐘的處理與SystemVue所提供的方法一致,即可以DQS作為時(shí)鐘觸發(fā),若不以DQS作為時(shí)鐘,也可選擇與SerDes類(lèi)似的方法,使用內(nèi)部CDR恢復(fù)時(shí)鐘數(shù)據(jù):

·Delay :(on signal index)為不同的信號(hào)線(xiàn)設(shè)置不同的delay參數(shù)。

·Vref Calibration:用于校準(zhǔn)DC Offset,使之符合芯片中實(shí)際的DC Offset值。

·CTLE連續(xù)時(shí)間線(xiàn)性均衡

o Pole-zero 以零極點(diǎn)作為輸入設(shè)置(也可設(shè)置多組參數(shù)供使用者選擇)。

o Step/impulse response 輸入仿真或測(cè)量得到的時(shí)域響應(yīng)。

·AGC:output swing 實(shí)現(xiàn)信號(hào)可控增益。

·Compression:Non-linearity 模擬芯片中的電路非線(xiàn)性行為。

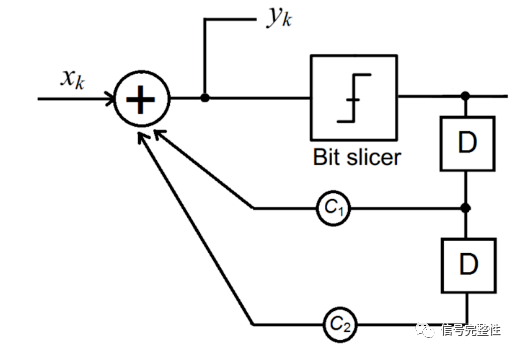

·DFE (adaptive)自適應(yīng)判決反饋均衡

oInitial taps

oDFE_alphafor adaptation

·Clocking

oUse CDR if DQS/CK

o If not DQS/CK, support DQS as forwarded clock (當(dāng)進(jìn)行Controller建模時(shí),增加Phase Interpolation 相位插值功能,以找到最佳時(shí)鐘相位。)

oSupport delay

·Reserved Parameters

審核編輯:劉清

-

仿真器

+關(guān)注

關(guān)注

14文章

1034瀏覽量

85066 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1438瀏覽量

96498 -

SPICE

+關(guān)注

關(guān)注

6文章

190瀏覽量

43428 -

IBIS

+關(guān)注

關(guān)注

1文章

55瀏覽量

20164 -

AMI

+關(guān)注

關(guān)注

0文章

49瀏覽量

22039

原文標(biāo)題:高速串行總線(xiàn)的IBIS-AMI建模詳解

文章出處:【微信號(hào):SI_PI_EMC,微信公眾號(hào):信號(hào)完整性】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于HyperLynx VX.2.4的IBIS-AMI仿真測(cè)試臺(tái)構(gòu)建方案

IBIS 模型

視頻: Artix-7 FPGA:如何在大批量應(yīng)用中使用高速SerDes

申請(qǐng)TI Keystone DSP PCIe SerDes IBIS-AMI Models。

高速互連IBIS仿真模型概述

WEBENCH接口設(shè)計(jì)工具助力IBIS-AMI通道仿真

如何對(duì)系統(tǒng)進(jìn)行最佳建模

高速串行總線(xiàn)與并行總線(xiàn)的差別是什么?

IBIS建模對(duì)電路板原型設(shè)計(jì)的重要性

Agilent推出ADS 2010支持IBIS-AMI 模型

有關(guān)IBIS 6.1的知識(shí)信息簡(jiǎn)介

TI Keystone DSP Hyperlink SerDes IBIS-AMI型號(hào)

TDP1204 IBIS-AMI模型用戶(hù)指南

TDP0604 IBIS-AMI模型用戶(hù)指南

高速串行總線(xiàn)-IBIS-AMI模型建模詳解

高速串行總線(xiàn)-IBIS-AMI模型建模詳解

評(píng)論