什么是時鐘電路?什么是脈沖?時鐘電路是如何生成脈沖的?

時鐘電路是一種電路,它產生的周期性的信號被用作計算機系統的基準。時鐘電路產生的信號被稱為時鐘脈沖或時鐘信號。在計算機系統中,時鐘信號用于同步各種硬件部件的操作,使它們在正確的時間執行指定的任務。

脈沖是一種短暫的交流電信號,它的電壓在很短的時間內突然變化,然后再恢復原來的電壓水平。脈沖通常用于傳輸數字信號,因為它們可以很容易地轉換成數值的0或1。脈沖的頻率越高,傳輸數字數據的速度就越快。

時鐘電路可以用不同的方式生成脈沖。其中一個常用的方法是使用RC電路。RC電路由單個電阻和單個電容組成,它們被連接在一起形成一個簡單的電路。當電路被通電時,電容器開始充電,電阻緩慢地放電。當電容充滿電并且開始向電阻放電時,電路中的電壓開始下降。當電壓下降到某個閾值時,電容開始重新充電。這個過程不斷重復,產生一個周期性的脈沖。

另一種常用的方法是使用晶振。晶振是一種含有晶體的電路,晶體能夠產生穩定的振蕩。晶振通常由晶體管和電容組成的電路組成。電容被用來調節電路的頻率,晶體管將電路中的能量轉換成振蕩能量,從而產生時鐘脈沖。

時鐘電路還可以使用數字電路來生成脈沖。數字電路中的邏輯門可以根據不同的輸入產生不同的輸出。當邏輯門的輸入發生變化時,它們可以立即輸出一個脈沖。這種方式可以實現非常高速的脈沖產生,因為邏輯門可以在很短的時間內響應輸入信號。

除了上述方法,還有其他一些方法可以產生時鐘脈沖。例如,使用LC電路、放大器等。不同的方法適用于不同類型的應用,因此設計時鐘電路需要根據具體的應用需求選擇不同的方法。

總的來說,時鐘電路是計算機系統中至關重要的組成部分。它產生穩定的時鐘脈沖,用于同步各種硬件部件的操作,從而保證計算機系統的正確,高效運行。時鐘電路的設計方法多種多樣,設計師們需要結合具體應用需求,選擇合適的設計方法。

-

RC電路

+關注

關注

2文章

165瀏覽量

30887 -

脈沖信號

+關注

關注

6文章

402瀏覽量

37615 -

時鐘電路

+關注

關注

10文章

243瀏覽量

51347

發布評論請先 登錄

使用LTC2500 芯片的同步功能時,可以把MCLK時鐘停止后,發一個SYNC同步脈沖嗎?

電容在時鐘電路中的應用有哪些

時鐘電路與晶振電路兩者的區別有哪些

時序約束一主時鐘與生成時鐘

視頻時鐘合成芯片怎么用

脈沖變壓器的驅動電路有哪些

脈沖變壓器的并聯電路是什么

如何處理時鐘電路的常見故障

時鐘抖動和時鐘偏移的區別

使用FPGA產生一個5MHz的時鐘信號,怎樣把脈沖信號疊加到時鐘信號上?

三相橋式整流電路的脈沖采用什么脈沖和什么脈沖

晶振頻率、脈沖、時鐘周期與機械周期的關系

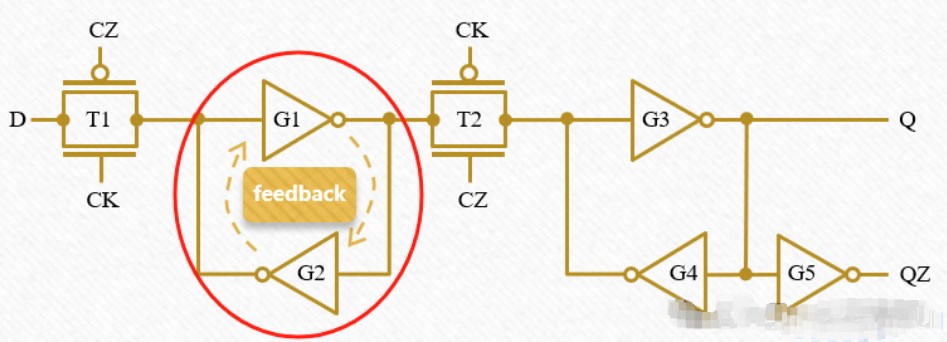

基于D觸發器的音頻信號發生器電路圖 D觸發器的工作原理和脈沖特性

什么是時鐘電路?什么是脈沖?時鐘電路是如何生成脈沖的?

什么是時鐘電路?什么是脈沖?時鐘電路是如何生成脈沖的?

評論