邏輯電平是數(shù)字電子系統(tǒng)中的關(guān)鍵概念之一。它決定了信號(hào)被認(rèn)定為高電平還是低電平,并進(jìn)一步影響著數(shù)字電路的正確操作。

邏輯電平是用來(lái)表示數(shù)字信號(hào)狀態(tài)的電壓水平。在數(shù)字電子系統(tǒng)中,常用的邏輯電平有高電平(通常表示為“1”)和低電平(通常表示為“0”)。這兩個(gè)電平分別對(duì)應(yīng)于二進(jìn)制的“1”和“0”,代表著不同的邏輯狀態(tài)。邏輯電平的穩(wěn)定性對(duì)于正確地識(shí)別和處理數(shù)字信號(hào)至關(guān)重要。

01

TTL邏輯電平

/ TTL

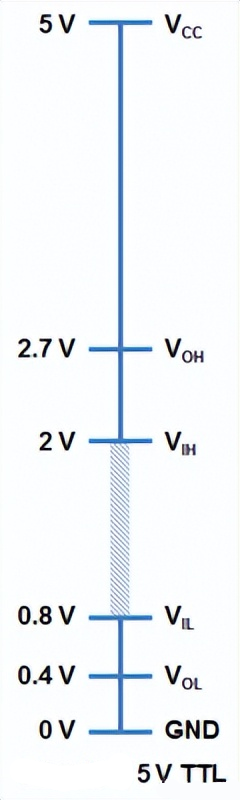

TTL(Transistor-Transistor Logic)邏輯電平是早期廣泛使用的數(shù)字邏輯家族之一。TTL電平基于晶體管的飽和區(qū)和截止區(qū)之間的轉(zhuǎn)換。在TTL電路中,高電平被定義為2V至5V的電壓范圍,低電平則為0V至0.8V。

輸入高電平(VIH):當(dāng)輸入電平高于VIH,則認(rèn)為輸入電平為高電平。

輸入低電平(VIL):當(dāng)輸入電平低于VIL,則認(rèn)為輸入電平為低電平。

輸出高電平(VOH):邏輯門的輸出為高電平時(shí),電壓必須大于此值。

輸出低電平(VOL):邏輯門的輸出為低電平時(shí),電壓必須小于此值。

閾值電平(VT):電路剛好能翻轉(zhuǎn)時(shí)的電平。

一般情況下:VOH>VIH>VT>VIL>VOL

TTL邏輯電平的主要特點(diǎn)

①高噪聲容忍度

TTL邏輯電平對(duì)噪聲的抵抗能力較強(qiáng),可以正常工作在高噪聲環(huán)境下。

②快速開(kāi)關(guān)速度

TTL家族具有較高的開(kāi)關(guān)速度,適用于需要高速操作的場(chǎng)景。

③相對(duì)較高的功耗

由于其特殊的電路結(jié)構(gòu),TTL電路通常消耗較高的功率。

02

CMOS邏輯電平

/ CMOS

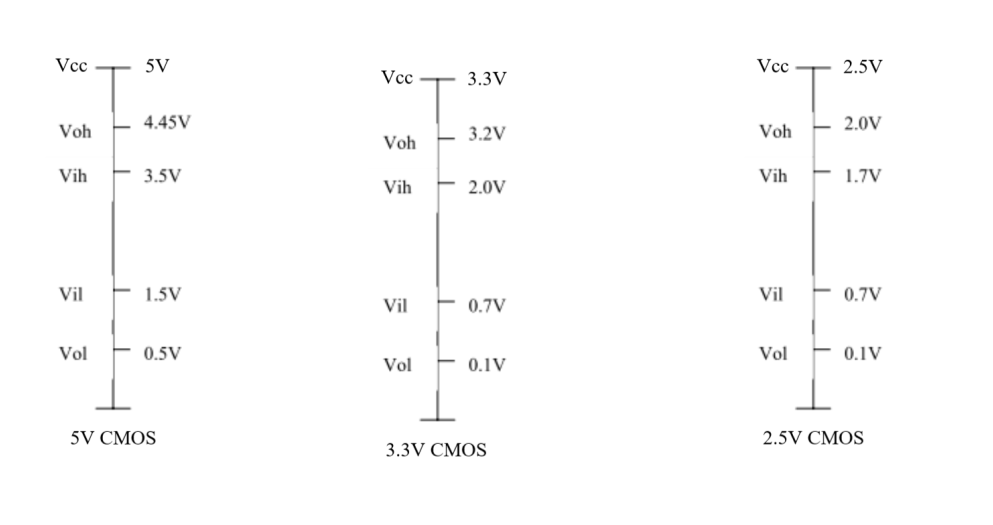

CMOS(Complementary Metal-Oxide-Semiconductor)邏輯電平是現(xiàn)代數(shù)字電子系統(tǒng)中常用的一種邏輯電平。CMOS邏輯電平通過(guò)晶體管的導(dǎo)通和截止來(lái)實(shí)現(xiàn)信號(hào)的切換。CMOS電平具有很寬的噪聲容限。

輸出 L:<0.1*Vcc;H:>0.9*Vcc

輸入 L:<0.3*Vcc ;H:>0.7*Vcc

CMOS邏輯電平的特點(diǎn)

① 低功耗

相對(duì)于TTL電路,CMOS電路的功耗較低,使其成為許多便攜式設(shè)備中的理想選擇。

② 高抗噪聲性能

CMOS邏輯電平對(duì)噪聲的容忍度也較高,可以在噪聲環(huán)境中保持良好的信號(hào)完整性。

③ 較寬的工作電壓范圍

CMOS電路可以在較寬的電壓范圍內(nèi)正常工作,提供了更大的設(shè)計(jì)靈活性。

通常,在電路中會(huì)遇到TTL電路和CMOS電路混合使用的情況,由于這些電路之間的電源電壓、輸入/輸出電平及負(fù)載能力等參數(shù)不盡相同,因此它們之間的連接需要通過(guò)電平轉(zhuǎn)換電路,使前級(jí)器件的輸出邏輯電平滿足后級(jí)器件對(duì)輸入電平的要求。

當(dāng)不同邏輯電平之間需要進(jìn)行轉(zhuǎn)換時(shí),我們可以使用電平轉(zhuǎn)換電路。

① TTL驅(qū)動(dòng)CMOS電路

當(dāng)它們使用相同的電源電壓時(shí),可采用外接上拉電阻的方式提高TTL的驅(qū)動(dòng)能力;當(dāng)使用不同的電源電壓時(shí),必須采用電平轉(zhuǎn)換電路。如3.3V TTL驅(qū)動(dòng)5V CMOS:高電平輸出大于2.4V,如果落在2.4V至3.5V之間,CMOS電路不能檢測(cè)到高電平,需要進(jìn)行電平轉(zhuǎn)換。

② CMOS驅(qū)動(dòng)TTL電路

3.3V/5V CMOS可以直接驅(qū)動(dòng)3.3V/5V TTL。3.3V CMOS驅(qū)動(dòng)5V CMOS:高電平輸出3.3V,CMOS電路不能檢測(cè)到高電平,需要進(jìn)行電平轉(zhuǎn)換。

如果是其它電平,請(qǐng)參考TTL與CMOS電平規(guī)范判斷是否需要進(jìn)行電平轉(zhuǎn)換。另外,5V TTL和5V CMOS電平已經(jīng)不常用了,因?yàn)樗鼈冚斎?輸出電平差距較大。

03

常見(jiàn)電平轉(zhuǎn)換方式

/ 電平轉(zhuǎn)換

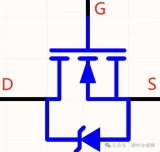

① 晶體管+上拉電阻

該方法是使用一個(gè)雙極型三極管或MOS管,C/D極接一個(gè)上拉電阻到正電源,輸出電平大致就是正電源電平。

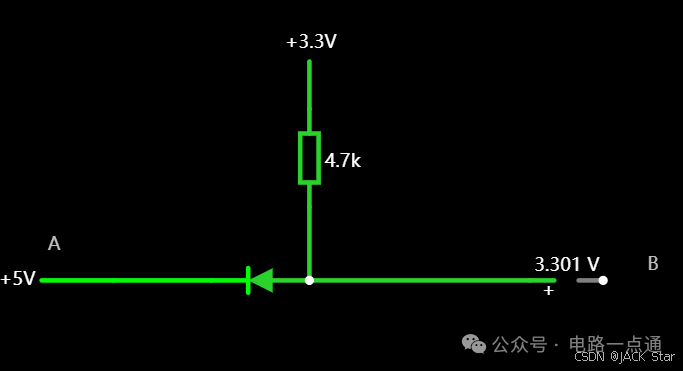

② OC/OD器件+上拉電阻

該方法適用于器件輸出剛好是OC/OD的場(chǎng)合。OC門即集電極開(kāi)路門電路;OD門即漏極開(kāi)路門電路。

③ 專用電平轉(zhuǎn)換芯片

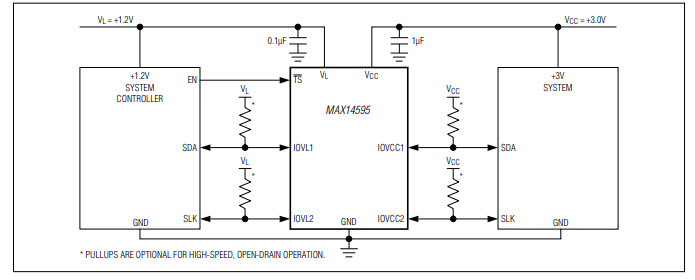

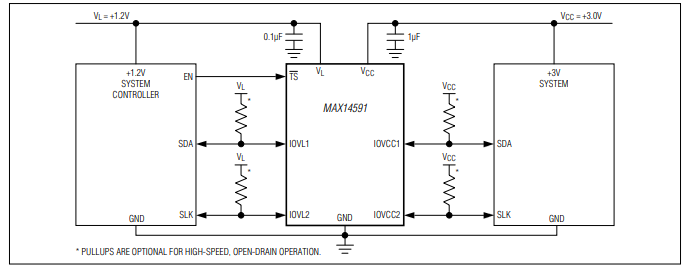

這是最通用的電平轉(zhuǎn)換方法,有些芯片不僅可以用作升壓/降壓,還能允許兩邊電源不同步,但價(jià)格也比較昂貴。如非必要,可以嘗試后面兩種方法。

④ 電阻分壓

最簡(jiǎn)單的降低電平的方法。如5V電平經(jīng)過(guò)1.6k+3.3k電阻分壓后就變成3.3V。但這種方法缺點(diǎn)也很明顯,功耗較大、驅(qū)動(dòng)能力不強(qiáng),帶載能力差。

⑤ 限流電阻

若是覺(jué)得使用兩個(gè)電阻太多,有時(shí)還可以只串聯(lián)一個(gè)限流電阻,保證輸入保護(hù)電流不超過(guò)電源極限就可以了。

⑥ 74xHCT系列芯片升壓(3.3V→5V)

直接使用芯片進(jìn)行電平轉(zhuǎn)換,速率快、驅(qū)動(dòng)能力強(qiáng)、成本高。凡是輸入與5V TTL電平兼容的5V CMOS器件都可以用作3.3V→5V電平轉(zhuǎn)換。這是因?yàn)?.3V CMOS的電平可以剛好與5V TTL電平兼容,而CMOS的輸出電平總是接近電源電平。

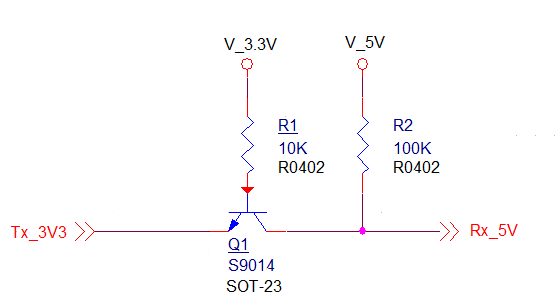

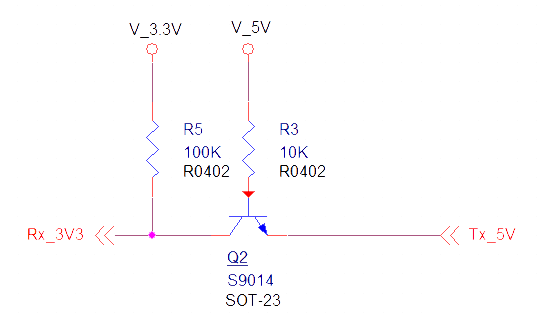

參考示例:

① 3.3V→5V電平轉(zhuǎn)換

如上圖,R1與Q1組成OC門,配合R2上拉至5V,以此實(shí)現(xiàn)電平轉(zhuǎn)換。Tx輸出0V,Q1導(dǎo)通,Rx端為0.3V左右;Tx輸出3.3V,Q1截止,RX端為5V,完成電平轉(zhuǎn)換功能。

② 5V→3.3V電平轉(zhuǎn)換

R3與Q2組成OC門,配合R5上拉至3.3V,實(shí)現(xiàn)電平轉(zhuǎn)換。Tx輸出0V,Q2導(dǎo)通,Rx端為0.3V左右;Tx輸出5V,Q2截止,RX端為3.3V,完成電平轉(zhuǎn)換功能。

邏輯電平作為數(shù)字電子系統(tǒng)中的核心概念,決定了信號(hào)的正確解讀和處理。本文簡(jiǎn)單介紹了不同邏輯電平之間進(jìn)行轉(zhuǎn)換的常見(jiàn)方案,至于其他的轉(zhuǎn)換方式,感興趣的朋友可以自行研究。

-

電平

+關(guān)注

關(guān)注

5文章

367瀏覽量

40452 -

電子系統(tǒng)

+關(guān)注

關(guān)注

0文章

458瀏覽量

31589 -

邏輯電平

+關(guān)注

關(guān)注

0文章

185瀏覽量

14722

發(fā)布評(píng)論請(qǐng)先 登錄

MAX14595高速、漏極開(kāi)路邏輯電平轉(zhuǎn)換器技術(shù)手冊(cè)

MAX14591高速、漏極開(kāi)路邏輯電平轉(zhuǎn)換器技術(shù)手冊(cè)

MAX14611 4通道雙向邏輯電平轉(zhuǎn)換器技術(shù)手冊(cè)

有幾種電平轉(zhuǎn)換電路,適用于不同的場(chǎng)景

電平轉(zhuǎn)換電路設(shè)計(jì)原理和常見(jiàn)問(wèn)題及解決辦法

《電子懶人的基礎(chǔ)硬件電路圖講解》

TTL電平電路的故障排查方法

使用TTL電平時(shí)的常見(jiàn)問(wèn)題

TTL電平與高電平信號(hào)的轉(zhuǎn)換

TTL電平與CMOS電平的區(qū)別是什么

電平轉(zhuǎn)換電路的實(shí)現(xiàn)原理及電路圖分享

高電平輸入和低電平輸入是什么意思

通過(guò)電平轉(zhuǎn)換實(shí)現(xiàn)窄帶IoT實(shí)現(xiàn)

邏輯電平輸出是什么意思

利用TXH實(shí)現(xiàn)高電壓電平轉(zhuǎn)換

什么是邏輯電平?如何實(shí)現(xiàn)電平轉(zhuǎn)換?(原理講解+電路圖)

什么是邏輯電平?如何實(shí)現(xiàn)電平轉(zhuǎn)換?(原理講解+電路圖)

評(píng)論