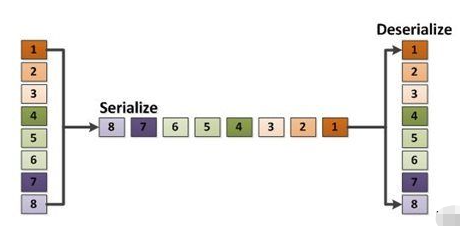

串行解串器 (Serializer/Deserializer, SerDes)的特點為數據與時鐘在同一信道中傳輸,在接收端通過時鐘數據恢復技術(CDR)提取數據中所包含的時鐘信息并以此時鐘采樣接收到的數據。當前,絕大部分高速信號傳輸使用SerDes 結構。

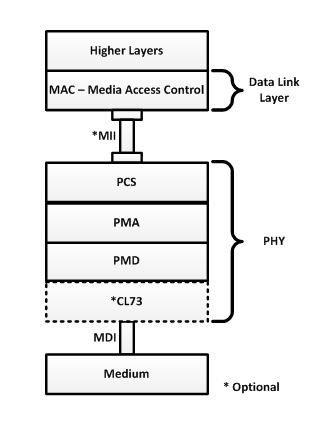

SerDes 的發送端(TX)包括并串轉換器、編碼器、發送端均衡、驅動器等部分,SerDes 的接收端(RX)包括接收端衰減器 (ATT)、接收端均衡、時鐘數據恢復、解碼器、串并轉換等。目前SerDes 主要有并行時鐘 SerDes 方案(Parallel Clock SerDes)、嵌入式時鐘SerDes 架構 (Embedded Clock SerDes)、8bit/10bit SerDes 方案、位交織SerDes 方案(Bit Interleaved SerDes)四種實現方案。

并行時鐘 SerDes 方案中時鐘與數據分離,數據與控制/地址位信號分別傳輸,其中數據與時鐘信號分別通過特定線傳輸,常用于低速傳輸。其優點在于不需要時鐘數據恢復電路,電路簡單,對抖動要求低;其缺點在于需要額外的時鐘線,且時鐘線會造成電磁輻射(EMI)及串擾,因此無法在高速鏈路上使用。目前采用該種 SerDes 的有 DDR 等。

嵌入式時鐘 SerDes 架構是標準 SerDes 架構,即時鐘嵌入數據信號中并在接收端通過 CDR 恢復。優點在于消除了單獨時鐘線引起的電磁干擾和串擾的影響,且減少了時鐘線對 PCB 布局的影響;缺點在于遠端時鐘恢復對抖動要求高,PCle、USB 3.0、USB 3. 1、SATA 均采用此種 SerDes 方案。

8bit/10bit SerDes 方案,即在串行數據中添加額外編碼來平衡直流分量,降低CDR 壓力。其編碼不一定是 8bit/10bit,也有更高效率的編碼,比如 PCle3.0的 128bit/ 132bit 編碼。優點在于插入的位可防止長“1”或“0”碼型,從而能夠始終讓 CDR 接收到 0/1 跳變保證其正常工作;缺點在于插入的位會造成無效冗余,比如 8bit/10bit 編碼的冗余可達到 20%。

位交織 SerDes 方案是指將多個低速串行數據拼接成一條高速串行數據。其優點在于能提高速率且減少數據傳輸通道數,有利于 PCB 的布局及降低串擾;缺點在于需要額外的時鐘、選擇器和 CDR 電路。12Gbit/s XAUI (XAUIx4)就是通過這種架構實現的。

由于數據傳輸速度的不斷提高,所以開發出了 SerDes 結構。早期信號傳輸速度僅為 kbit/s~ Mbit/s 時,并行接口足以處理此類型傳輸。然而伴隨工藝的更新和傳輸速率的增長,高速信號特別是時鐘信號對其他傳輸線造成的串擾(Crosstalk)日益嚴重并影響傳輸質量;同時,應用產品的小型化也需要減少并行走線:因此,使用串行走線并不需要單獨時鐘線的 Ser Des 結構成為最好選擇。

SerDes 架構是目前民用高速接口協議的主流選擇。目前國內外各大公司均采用SerDes 架構來實現高速接口產品,如Synopsys 的 USB/PCIe/SATA 等IPIP、華為的 10Gbit/s 企業級 SerDes Xilinx 在2011 年推出的 26Gbit/s SerDes 等。

-

編碼器

+關注

關注

45文章

3792瀏覽量

137870 -

高速接口

+關注

關注

1文章

58瀏覽量

14981 -

解串器

+關注

關注

1文章

142瀏覽量

14155 -

串行解串器

+關注

關注

0文章

8瀏覽量

6815

原文標題:串行/解串器,串列/解串器,SerDes

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

簡單認識串行解串器

簡單認識串行解串器

評論