什么叫與邏輯陣列

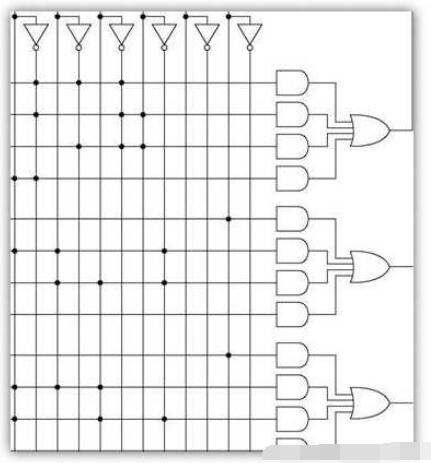

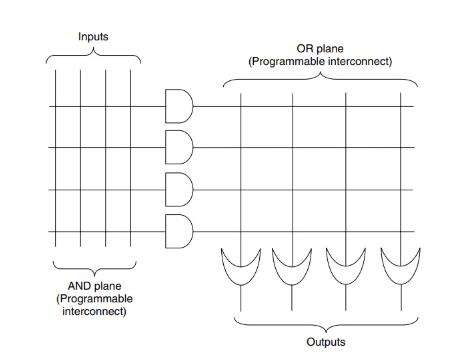

與邏輯陣列(AND Logic Array),又稱為與陣列或與門陣列,是一種數(shù)字邏輯電路的實(shí)現(xiàn)方式。它基于多個(gè)與門(AND gate)的集合,用于執(zhí)行與門的邏輯運(yùn)算。

與邏輯陣列由多個(gè)輸入引腳、與門和輸出引腳組成。每個(gè)與門具有兩個(gè)或更多的輸入引腳和一個(gè)輸出引腳。它的輸出引腳連接到輸出引腳,而每個(gè)輸入引腳都可以連接到輸入信號(hào)。與邏輯陣列將輸入信號(hào)通過與門的邏輯運(yùn)算來產(chǎn)生輸出結(jié)果。

在一個(gè)與邏輯陣列中,輸出引腳的值取決于輸入引腳的狀態(tài)以及與門的邏輯關(guān)系。當(dāng)且僅當(dāng)所有的輸入引腳都為高電平(通常表示為1)時(shí),與門的輸出引腳才會(huì)為高電平;否則,輸出引腳將為低電平(通常表示為0)。因此,與邏輯陣列可以實(shí)現(xiàn)多個(gè)輸入信號(hào)之間的“與”邏輯運(yùn)算。

與邏輯陣列通常被用于構(gòu)建更復(fù)雜的邏輯電路,如組合邏輯電路和時(shí)序邏輯電路。通過組合不同數(shù)量和類型的與門,可以實(shí)現(xiàn)各種復(fù)雜的邏輯功能,如加法器、計(jì)數(shù)器、多路選擇器等。

與邏輯陣列的點(diǎn)有什么用

在與邏輯陣列中,與邏輯門的輸入引腳通常通過開關(guān)或編程連線與輸入信號(hào)相連接。而與邏輯陣列的點(diǎn)則是指它們與邏輯門輸入引腳的連接點(diǎn)。

與邏輯陣列的點(diǎn)在邏輯電路的設(shè)計(jì)和實(shí)現(xiàn)中具有重要的作用。以下是一些與邏輯陣列點(diǎn)的常見用途:

1. 連接輸入信號(hào):與邏輯陣列的點(diǎn)用于將輸入信號(hào)與邏輯門的輸入引腳相連接。這樣,輸入信號(hào)可以傳遞到與門中進(jìn)行邏輯運(yùn)算。

2. 配置邏輯功能:通過選擇與邏輯陣列點(diǎn)的連接方式,可以配置邏輯功能。根據(jù)特定的邏輯運(yùn)算需求,可以將適當(dāng)數(shù)量的與門連接在一起,以實(shí)現(xiàn)所需的邏輯運(yùn)算。

3. 反饋與觸發(fā):與邏輯陣列點(diǎn)還可以用于實(shí)現(xiàn)邏輯電路的反饋和觸發(fā)功能。通過將與門的輸出連線連接到與邏輯陣列點(diǎn),可以實(shí)現(xiàn)邏輯電路中的狀態(tài)存儲(chǔ)和時(shí)序邏輯功能。

4. 連接輸出引腳:與邏輯陣列的輸出點(diǎn)用于連接邏輯門的輸出引腳,以將邏輯運(yùn)算的結(jié)果傳遞到其他部分的電路中。

與邏輯陣列的點(diǎn)是用于連接輸入信號(hào)、配置邏輯功能、實(shí)現(xiàn)反饋和觸發(fā)以及連接輸出引腳的關(guān)鍵位置。它們使得與邏輯陣列能夠?qū)崿F(xiàn)各種邏輯運(yùn)算,并與其他部分的邏輯電路進(jìn)行正常的交互和連接。

審核編輯:黃飛

-

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43306 -

邏輯運(yùn)算

+關(guān)注

關(guān)注

0文章

57瀏覽量

9952 -

數(shù)字邏輯電路

+關(guān)注

關(guān)注

0文章

106瀏覽量

16097 -

and

+關(guān)注

關(guān)注

0文章

32瀏覽量

7523

發(fā)布評(píng)論請先 登錄

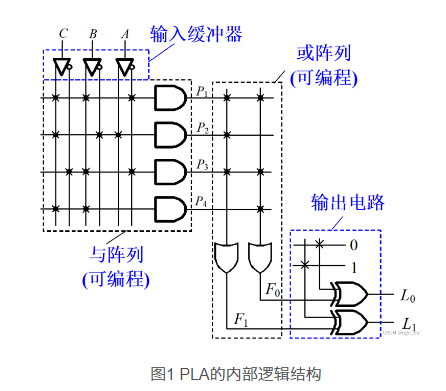

可編程邏輯陣列PLA內(nèi)部邏輯結(jié)構(gòu)示意

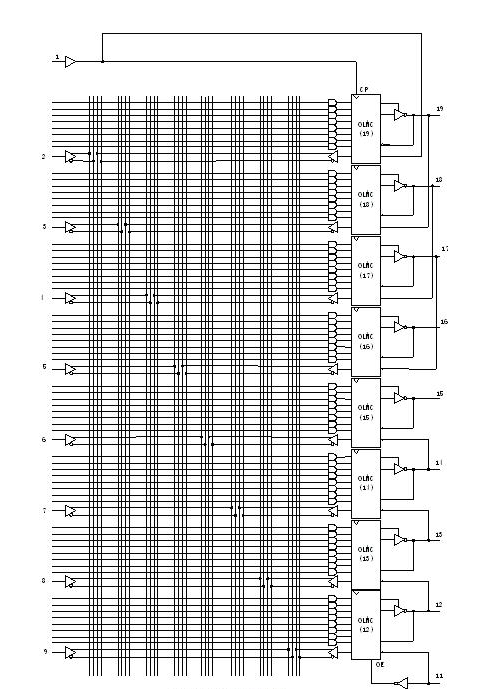

通用陣列邏輯(GAL)電路結(jié)構(gòu)設(shè)計(jì)分析

Cyclone IV 器件的邏輯單元和邏輯陣列模塊

通用陣列邏輯GAL實(shí)現(xiàn)基本門電路的設(shè)計(jì)

可編程陣列邏輯(Programmable Array Log

可編程陣列邏輯PAL簡介

可編程邏輯陣列(PLA)簡介

現(xiàn)場可編程邏輯門陣列器件 FPGA原理及應(yīng)用設(shè)計(jì)

磁盤陣列有什么用

可編程陣列邏輯的構(gòu)造及運(yùn)用

可編程邏輯陣列(PLA)有什么用?

什么叫與邏輯陣列 與邏輯陣列的點(diǎn)有什么用

什么叫與邏輯陣列 與邏輯陣列的點(diǎn)有什么用

評(píng)論