當(dāng)邏輯電路由多個邏輯門組成且不含存儲電路,對于給定的輸入變量組合將產(chǎn)生確定的輸出,則這種邏輯電路稱為組合邏輯電路。在組合邏輯電路中,電路任一時刻的輸出電平只取決于該時刻各輸入電平的組合。

基本組合邏輯電路,積之和(SOP)表達(dá)式由與門(AND)和或門(OR)來實(shí)現(xiàn),一個與門對應(yīng)于一個乘積項(xiàng),而或門實(shí)現(xiàn)對所有的乘積項(xiàng)相加,這種積之和表達(dá)式的實(shí)現(xiàn)稱為與或(AND-OR)邏輯,它是實(shí)現(xiàn)標(biāo)準(zhǔn)布爾函數(shù)的基本形式。本節(jié)將介紹與或邏輯!

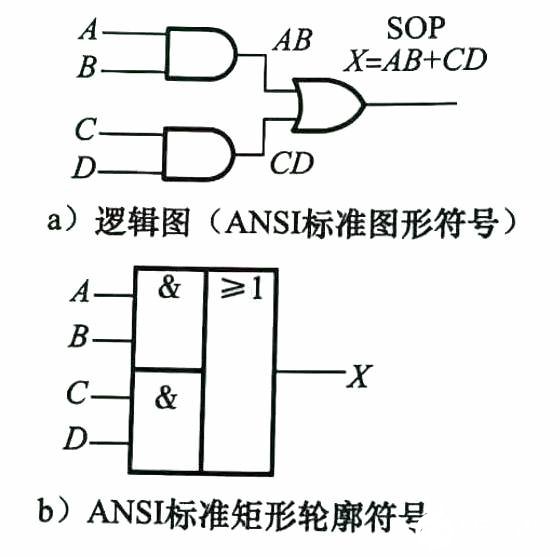

與或邏輯生成一個積之和表達(dá)式,圖a中給出了一個用ANSI標(biāo)準(zhǔn)圖形符號表示的與或電路,由兩個二輸入與門和一個二輸入或門組成;圖b是對應(yīng)的ANSI標(biāo)準(zhǔn)矩形輪廓符號。

上圖所示的四輸入與或邏輯電路的真值表如表所示,同時第一級與門的輸出(AB和CD列)也列在真值表中。

與或(AND-OR)電路的邏輯運(yùn)算表述如下:對于四輸入與或邏輯電路,如果輸入A和輸入B都是高電平(1)或者輸入C和輸入D都是高電平(1),則輸出X就是高電平。

上圖中輸出表達(dá)式上方所標(biāo)注的術(shù)語SOP表示積之和(sum-of product, SOP)。在前面中已經(jīng)明確了與運(yùn)算實(shí)質(zhì)就是布爾乘法,因此,當(dāng)兩個或多個變量進(jìn)行與運(yùn)算時所對應(yīng)的結(jié)果就是一一個乘積項(xiàng)。由此可知AB和CD均是布爾乘積項(xiàng)。而或運(yùn)算實(shí)質(zhì)就是布爾加法,當(dāng)乘積項(xiàng)AB和CD做或運(yùn)算時,結(jié)果實(shí)現(xiàn)的是兩個乘積項(xiàng)的布爾加法。因此,表達(dá)式x=AB+CD是一個積之和表達(dá)式。一個SOP表達(dá)式可是多個與項(xiàng)(乘積項(xiàng))相或的結(jié)果。

審核編輯:黃飛

-

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43306 -

存儲電路

+關(guān)注

關(guān)注

2文章

11瀏覽量

13236 -

and

+關(guān)注

關(guān)注

0文章

32瀏覽量

7522

發(fā)布評論請先 登錄

組合邏輯電路實(shí)驗(yàn)

基本組合邏輯電路

組合邏輯電路的分析與設(shè)計(jì)-邏輯代數(shù)

組合邏輯電路的設(shè)計(jì)

組合邏輯電路的分析與設(shè)計(jì)

什么是組合邏輯電路,組合邏輯電路的基本特點(diǎn)和種類詳解

組合邏輯電路實(shí)驗(yàn)原理

組合邏輯電路和時序邏輯電路比較_組合邏輯電路和時序邏輯電路有什么區(qū)別

什么是組合邏輯電路 如何使用verilog描述組合邏輯電路

組合邏輯電路之與或邏輯

組合邏輯電路之與或邏輯

評論