近期,加利福尼亞大學(xué)河濱分校電子與計(jì)算機(jī)工程副教授曾宏偉在其題為《同時(shí)和異構(gòu)多線程》(Simultaneous and Heterogeneous Multithreading,簡稱 SHMT)的研究論文中提出,計(jì)算機(jī)體系架構(gòu)正面臨重大變革。

他指出,目前,運(yùn)算設(shè)備日趨依賴 GPU、人工智能和機(jī)器學(xué)習(xí)相關(guān)的硬件加速器及數(shù)字信號處理單元。然而,這種單一處理器方式容易導(dǎo)致瓶頸問題。

SHMT 模型可充分利用ARM多核處理器、英偉達(dá) GPU以及谷歌張量處理器等硬件加速器,無需額外采購新的處理器就可實(shí)現(xiàn)1.96倍的性能提升和51%的能耗降低。此舉既有益于降低硬件投入,也有助于減緩數(shù)據(jù)中心運(yùn)營中的碳排放現(xiàn)象。

-

gpu

+關(guān)注

關(guān)注

28文章

4923瀏覽量

130853 -

人工智能

+關(guān)注

關(guān)注

1805文章

48863瀏覽量

247650 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8499瀏覽量

134273

發(fā)布評論請先 登錄

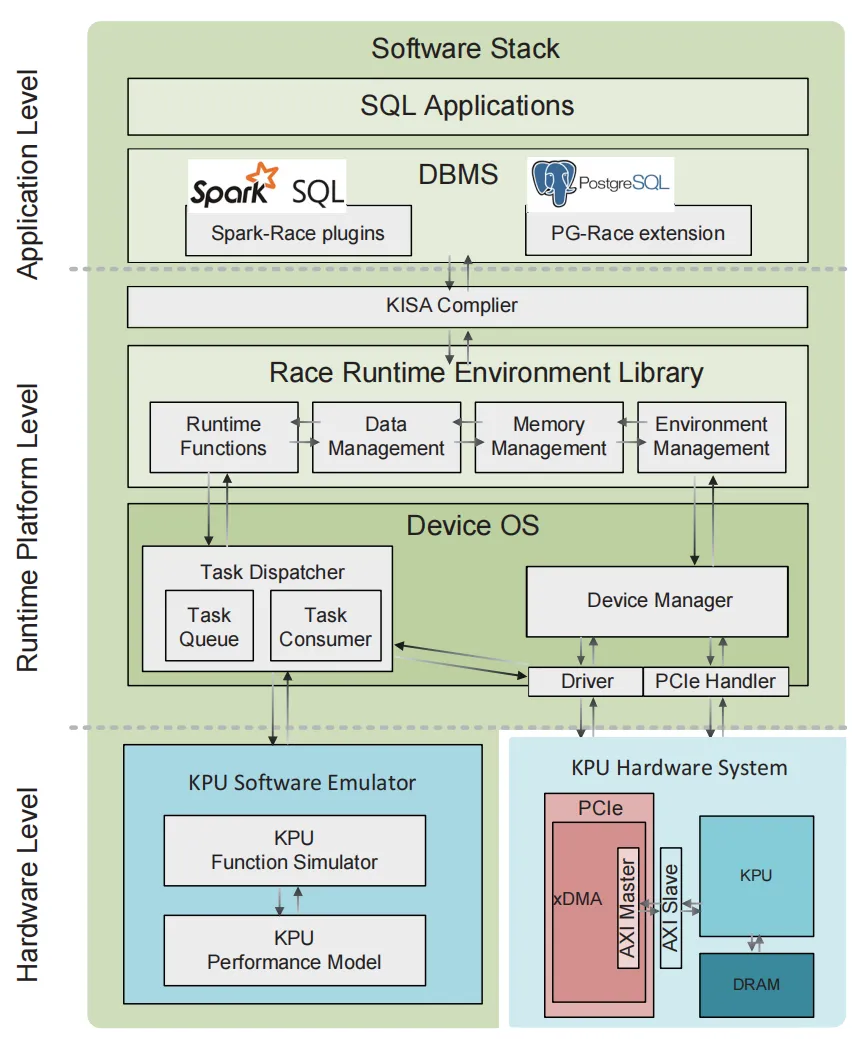

DPU核心技術(shù)論文再次登陸體系結(jié)構(gòu)領(lǐng)域旗艦期刊《IEEE Transactions on Computers》

睿創(chuàng)微納AI芯片技術(shù)登上國際計(jì)算機(jī)體系結(jié)構(gòu)領(lǐng)域頂級會(huì)議

【「RISC-V體系結(jié)構(gòu)編程與實(shí)踐」閱讀體驗(yàn)】-- SBI及NEMU環(huán)境

量子計(jì)算機(jī)與普通計(jì)算機(jī)工作原理的區(qū)別

什么是RISC-V?以及RISC-V和ARM、X86的區(qū)別

寄存器間接尋址和寄存器尋址的區(qū)別

計(jì)算機(jī)主機(jī)內(nèi)部結(jié)構(gòu)

CPU時(shí)鐘周期與主頻的關(guān)系和區(qū)別

CPU時(shí)鐘周期的組成和作用

內(nèi)存緩沖區(qū)和內(nèi)存的關(guān)系

RISC-V的理論與實(shí)踐探討

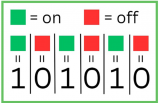

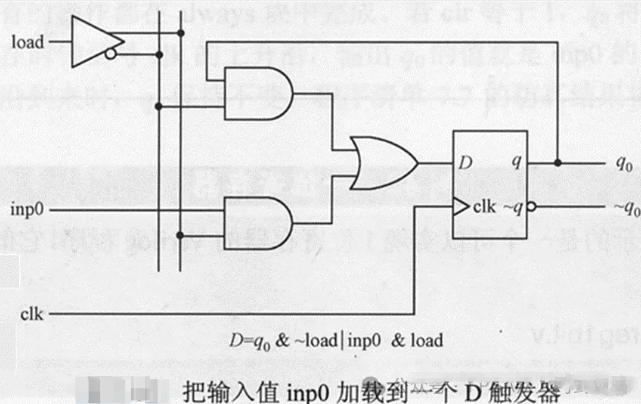

數(shù)字寄存器的原理和使用

新手如何學(xué)單片機(jī)

寄存器是什么意思?寄存器是如何構(gòu)成的?

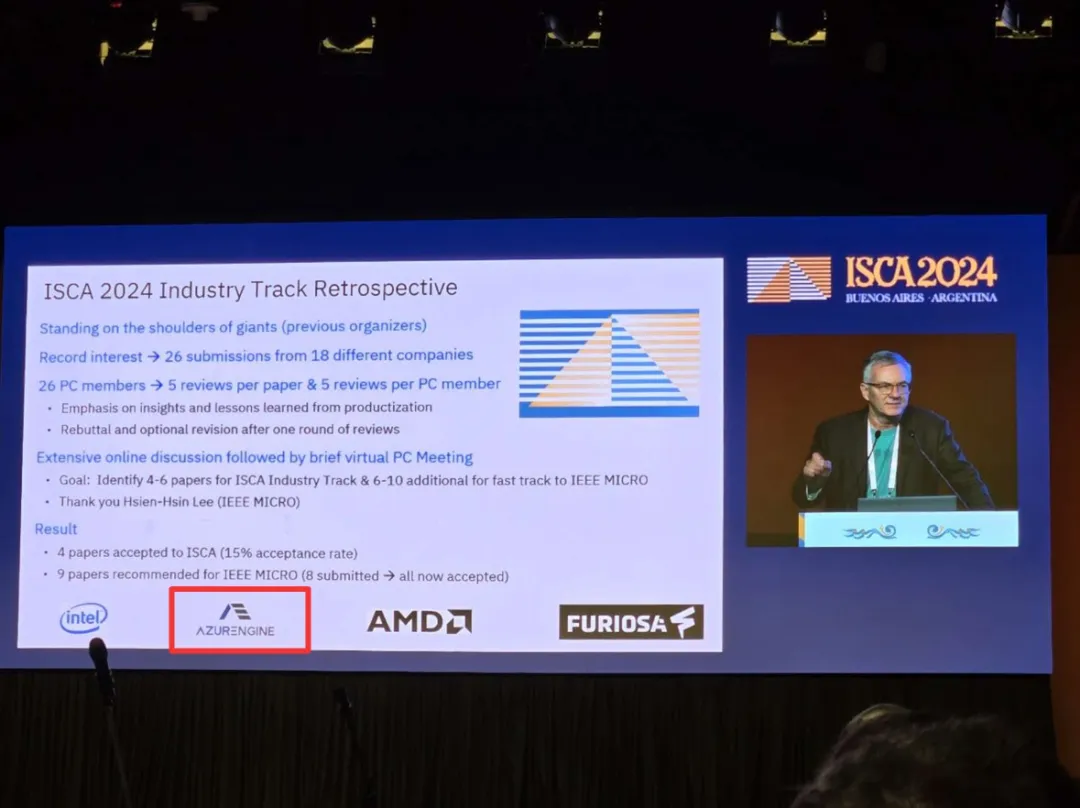

芯動(dòng)力科技論文入選ISCA 2024,與國際巨頭同臺交流研究成果

美國加州大學(xué)河濱分校教授引領(lǐng)計(jì)算機(jī)體系結(jié)構(gòu)范式變革

美國加州大學(xué)河濱分校教授引領(lǐng)計(jì)算機(jī)體系結(jié)構(gòu)范式變革

評論