FPGA(現(xiàn)場可編程門陣列)芯片中的觸發(fā)器是一種重要的存儲元件,它在數(shù)字電路設(shè)計(jì)中起著至關(guān)重要的作用。觸發(fā)器的主要功能是存儲和同步數(shù)字信號,確保電路在正確的時(shí)刻捕獲和保持信號狀態(tài)。

首先,從定義上來說,觸發(fā)器是一種存儲元素,它可以在時(shí)鐘信號的邊沿觸發(fā)時(shí)捕獲和存儲輸入信號的狀態(tài)。這意味著觸發(fā)器能夠記住某個(gè)特定時(shí)間點(diǎn)的信號值,并在需要時(shí)將其輸出。這種特性使得觸發(fā)器在數(shù)字信號處理、時(shí)序控制以及狀態(tài)機(jī)實(shí)現(xiàn)等應(yīng)用中非常有用。

其次,觸發(fā)器在FPGA中的用處廣泛而多樣。在時(shí)序電路設(shè)計(jì)中,觸發(fā)器用于實(shí)現(xiàn)時(shí)序控制,確保電路的穩(wěn)定性和可靠性。它們可以幫助設(shè)計(jì)師精確控制信號的傳輸和存儲時(shí)間,從而實(shí)現(xiàn)復(fù)雜的邏輯功能。此外,觸發(fā)器還可以作為寄存器的組成部分,用于存儲數(shù)據(jù)以備后續(xù)處理。

再者,F(xiàn)PGA中的觸發(fā)器類型多樣,每種類型都有其特定的應(yīng)用場景。例如,D觸發(fā)器(Data Trigger)通常用于數(shù)據(jù)的存儲與傳輸;T觸發(fā)器(Toggle Trigger)可以在時(shí)鐘信號的上升沿或下降沿改變其輸出狀態(tài);而JK觸發(fā)器(Jack Kilby Trigger)則具有更復(fù)雜的邏輯功能,可以在時(shí)鐘信號的邊沿根據(jù)輸入信號的狀態(tài)改變其輸出。

最后,值得一提的是,觸發(fā)器與寄存器雖然都是FPGA中的存儲元件,但它們的功能和應(yīng)用場景有所不同。觸發(fā)器主要用于同步存儲,而寄存器則可以通過時(shí)序組合邏輯實(shí)現(xiàn)狀態(tài)的存儲和更新,無需時(shí)鐘信號的觸發(fā)。因此,在FPGA設(shè)計(jì)中,觸發(fā)器通常用于需要保持存儲數(shù)據(jù)以備下一次計(jì)算使用的場景,如數(shù)字濾波器、狀態(tài)機(jī)等。

綜上所述,F(xiàn)PGA芯片中的觸發(fā)器是一種關(guān)鍵的存儲元件,具有廣泛的應(yīng)用場景和重要作用。它們不僅能夠幫助實(shí)現(xiàn)復(fù)雜的邏輯功能,還可以提高數(shù)字電路的穩(wěn)定性和可靠性。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22020瀏覽量

617114 -

芯片

+關(guān)注

關(guān)注

459文章

52395瀏覽量

439198 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2037瀏覽量

62045

發(fā)布評論請先 登錄

觸發(fā)器功能的模擬實(shí)驗(yàn)

什么是觸發(fā)器 觸發(fā)器的工作原理及作用

jk觸發(fā)器設(shè)計(jì)d觸發(fā)器

FPGA觸發(fā)器與寄存器的區(qū)別在哪

施密特觸發(fā)器,施密特觸發(fā)器是什么意思

基于CPLD的觸發(fā)器功能的模擬實(shí)現(xiàn)

施密特觸發(fā)器芯片有哪些_施密特觸發(fā)器的特點(diǎn)及作用

單穩(wěn)態(tài)觸發(fā)器芯片有哪些_單穩(wěn)態(tài)觸發(fā)器工作原理

Virtex-7 FPGA系列的片式觸發(fā)器資源

電平觸發(fā)器,脈沖觸發(fā)器和邊沿觸發(fā)器的觸發(fā)因素是什么

(14)FPGA觸發(fā)器與寄存器區(qū)別

FPGA設(shè)計(jì)的D觸發(fā)器與亞穩(wěn)態(tài)

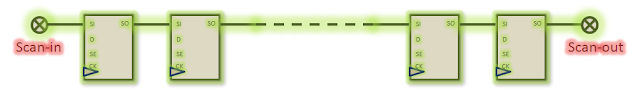

普通觸發(fā)器如何轉(zhuǎn)換為掃描觸發(fā)器

FPGA芯片中的觸發(fā)器是什么?它有哪些用處?

FPGA芯片中的觸發(fā)器是什么?它有哪些用處?

評論