文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了邏輯集成電路制造中有關良率提升以及對各種失效的分析。

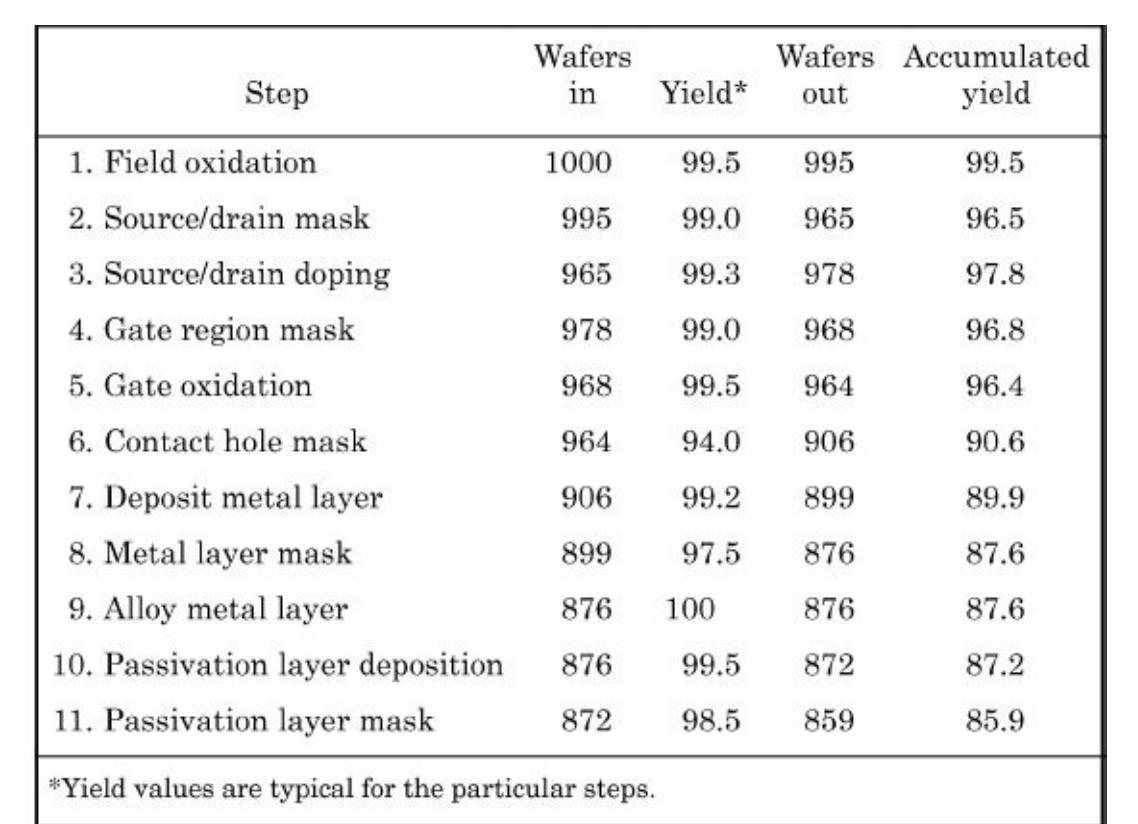

良率是衡量生產線能力的重要指標,在制造過程中,每個環節都有可能引起產品失效,良率會受到多種因素的影響,包括機臺參數漂移、工藝波動等。

工藝引起的器件失效可以分為參數性失效和功能性失效。參數性失效主要與器件的物理參數有關,如柵極尺寸、有源區尺寸等,而蝕刻工藝對參數性失效有很大影響。功能性失效則往往由晶圓上的缺陷引起,如物理性異物、化學性污染等,等離子體蝕刻對功能性失效也有顯著影響。

良率與缺陷

在邏輯集成電路制造中,良率提升是一個復雜而關鍵的過程,其中缺陷管理起著至關重要的作用。缺陷可以分為隨機缺陷和系統性缺陷,兩者對良率的影響不同,需要采取不同的策略進行改善。

隨機缺陷與系統型缺陷

隨機缺陷在時間和空間上隨機出現,通常保持在很低的水平,且難以完全消除。這類缺陷一般通過統計方法進行監控和管理,以確保它們對良率的影響控制在可接受范圍內。

相比之下,系統性缺陷與特定的工藝條件或版圖特征緊密相關,具有較高的發生概率。例如,蝕刻反應腔室掉落的顆粒物,如果數量較多且頻繁,就屬于系統性缺陷。這類缺陷可以通過改進工藝設備、優化工藝參數或改變材料等方法來消除或降低其影響。以蝕刻工藝為例,通過改進腔室內材料或涂層、定期清理腔室以及優化蝕刻參數等措施,可以有效減少顆粒物的掉落,從而提升良率。

良率提升與缺陷查找

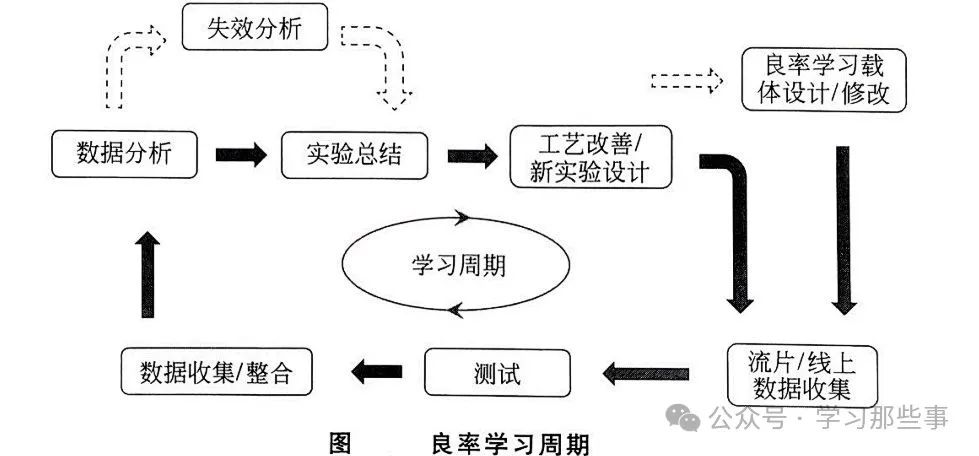

良率提升的實質是一個不斷學習和改進的過程。每個學習周期包括實驗設計、結果分析、工藝優化和反饋實施等環節。為了快速提升良率,需要縮短學習周期,盡快將實驗結果反饋到生產線上進行下一輪的工藝改善。

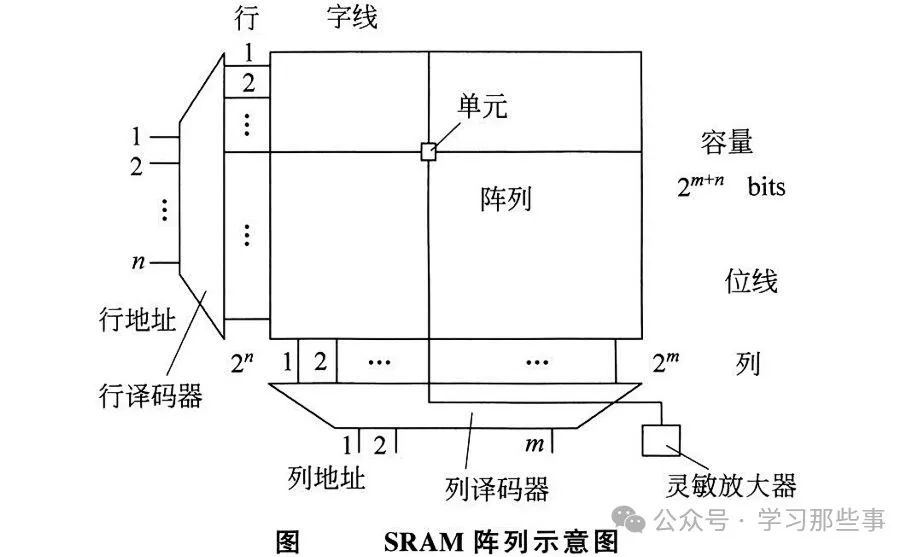

在制造廠開發新一代成套工藝時,通常會使用SRAM作為良率學習載體。SRAM具有較高的密度和缺陷覆蓋能力,能夠快速并精準地定位缺陷,便于進行失效分析和工藝優化。然而,需要注意的是,SRAM并不能完全覆蓋邏輯電路版圖中的各種難點,因此在邏輯產品上也需要進行良率學習。SRAM良率學習的經驗可以為邏輯產品良率的提升提供有益的參考。

為了有效分析良率數據并確認影響良率的原因,可以將良率分解為各種因素單獨起作用時的良率。其中,缺陷有限良率(DLY)是一個重要的指標,它反映了只有缺陷這一種機理起作用時產品能達到的最高良率。通過監控DLY,可以更準確地評估工藝上的缺陷情況,并采取相應的措施進行改善。

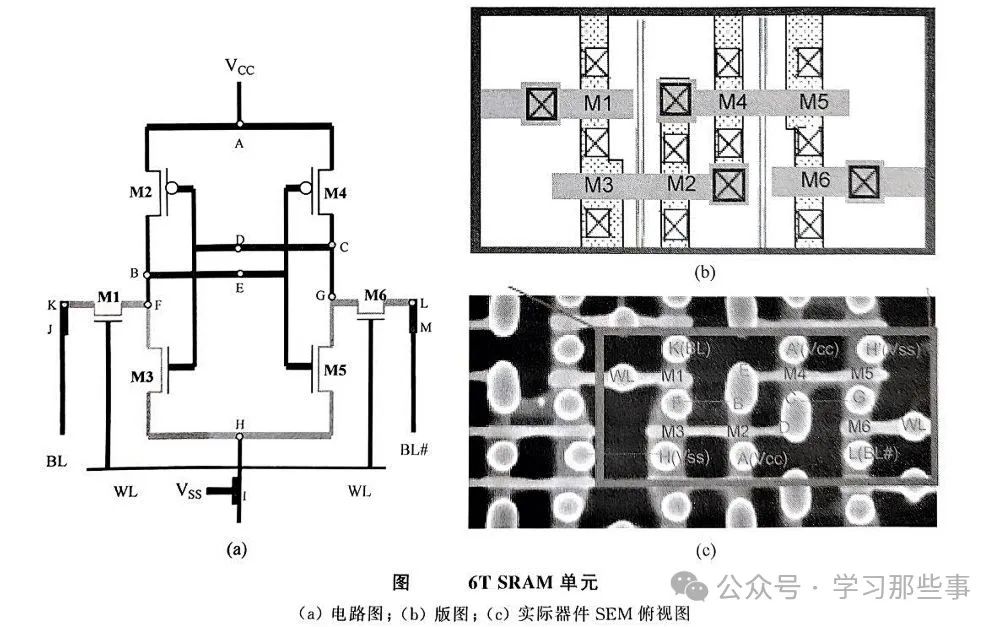

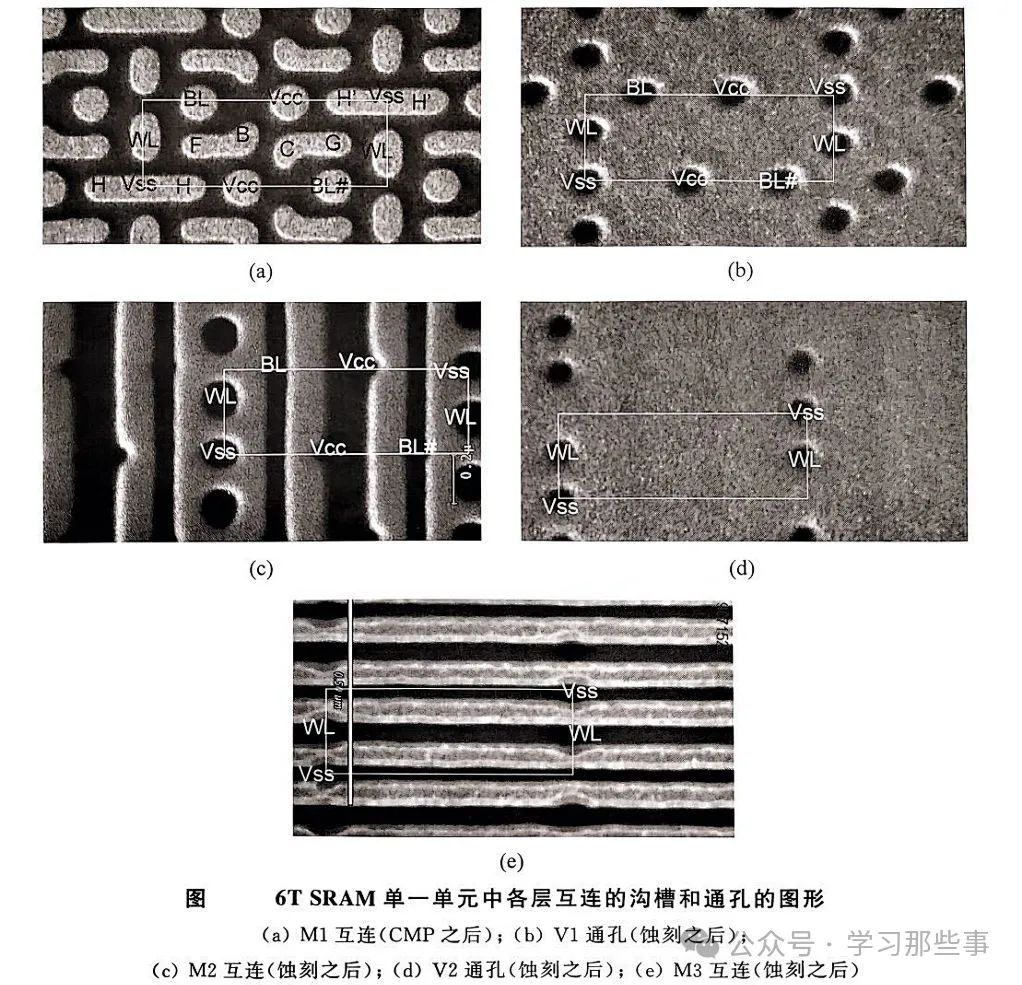

在SRAM單元的結構中,6T SRAM是一種常見的類型,由6個MOSFET構成。這些晶體管通過接觸孔和各層金屬層進行互連,形成存儲陣列。隨著集成電路尺寸的不斷微縮,光刻工藝的極限成為了制約因素之一。因此,在先進工藝節點下,需要采用多層掩膜版等技術來降低圖形密度,提高可制造性。同時,銅互連和雙大馬士革工藝等先進技術的應用也為良率的提升提供了有力支持。

失效分析

在6T SRAM良率測試完成后,為了確定失效的具體原因,需要進行失效定位(Failure Isolation)和失效分析(Failure Analysis, FA)。這一過程中,我們依賴于多種電氣失效分析(EFA)和物理失效分析(PFA)的方法和技術。

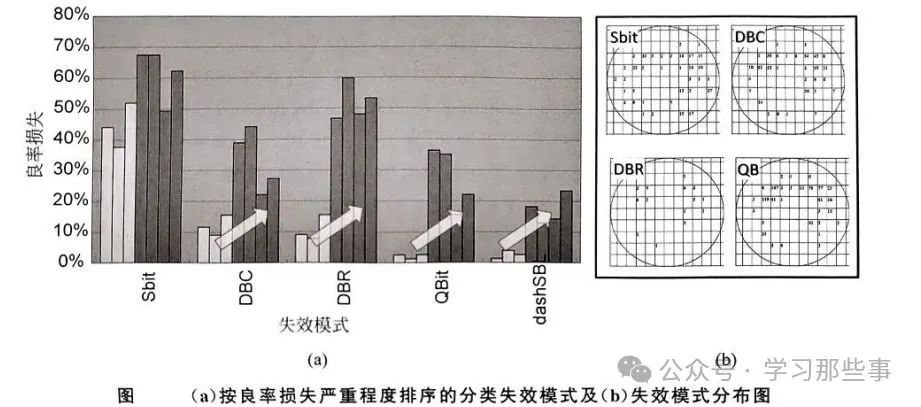

電氣失效分析(EFA)是一種通過電氣測試手段來定位和分類失效單元的方法。它能夠幫助我們識別出SRAM陣列中所有失效的單元,并根據失效模式(Failure Mode)對它們進行分類。這些失效模式包括但不限于單比特失效(SB)、雙比特列失效(DBC)、雙比特行失效(DBR)、四比特失效(QB)、位線失效(BL)、字線失效(WL)以及塊狀區域失效(Block)。通過分析這些失效模式,我們可以對失效的原因進行初步的判斷。例如,如果Vcc通孔斷路,可能會導致上下兩個單元失效,形成DBC模式;而如果WL通孔斷路,則會導致左右兩個單元失效,形成DBR模式。

為了更深入地了解失效的分布和特性,我們可以將失效模式按嚴重性進行排序,并比較不同晶圓間失效模式的差異。通過繪制失效模式在晶圓上的分布圖,我們可以發現某些失效模式在晶圓上的特定區域更為集中。這種特殊圖形的分布可以作為懷疑某些特定工藝與失效存在關聯性的重要線索。

一旦通過EFA定位了失效位置,我們就可以使用物理失效分析(PFA)的方法來進一步找出失效的根源。PFA依賴于一系列高精度的物理測試手段,如聚焦離子束(FIB)、掃描電子顯微鏡(SEM)、透射電子顯微鏡(TEM)以及能量分散光譜儀(EDS)等。這些工具能夠幫助我們直接觀察和分析失效區域的微觀結構和化學成分,從而揭示失效的根本原因。

操作實例

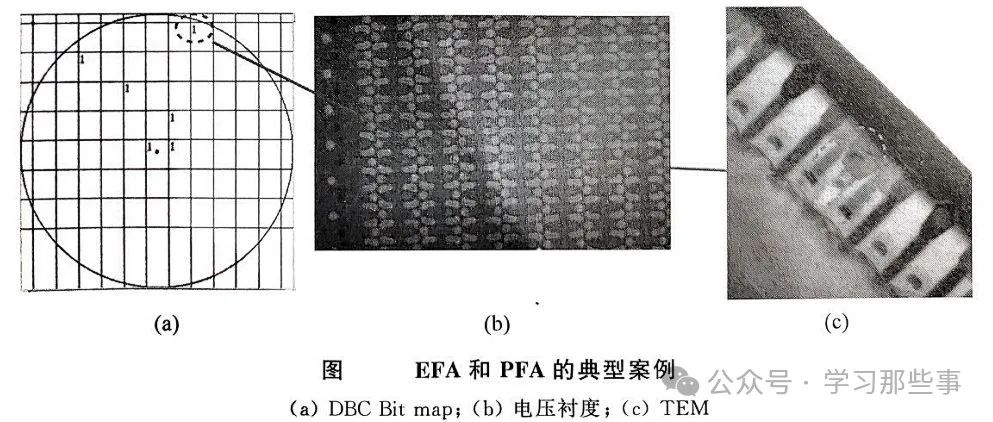

以一個典型的失效分析案例為例,通過Bitmap我們發現晶圓邊緣位置存在DBC失效。

隨后,我們使用電壓襯度(VC)方法在M1金屬層上發現了某一塊金屬(BL位置)在電壓下發暗,與周圍類似區域表現不一致。進一步切開后,剖面顯示接觸孔(CT)填充存在問題,這就是導致失效的根本原因。

-

集成電路

+關注

關注

5422文章

12032瀏覽量

368191 -

MOSFET

+關注

關注

150文章

8533瀏覽量

220080 -

工藝

+關注

關注

4文章

680瀏覽量

29409 -

邏輯集成電路

+關注

關注

0文章

3瀏覽量

5637

原文標題:詳談邏輯電路良率

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

集成電路制造技術的應用

良率提升工程數據分析系統工具

集成電路的設計與分工

什么是集成電路?

如何保證半導體良率

良品學習在高良率制造業中缺陷檢測的應用

邏輯集成電路制造中良率提升與缺陷查找

邏輯集成電路制造中良率提升與缺陷查找

評論