概述

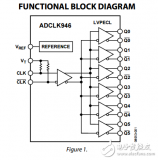

ADCLK946是一款采用ADI公司專有的XFCB3硅鍺(SiGe)雙極性工藝制造的超快型時鐘扇出緩沖器。這款器件設計用于要求低抖動性能的高速應用。

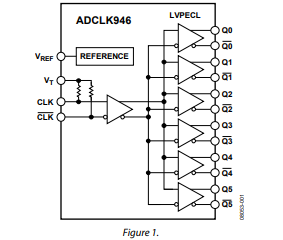

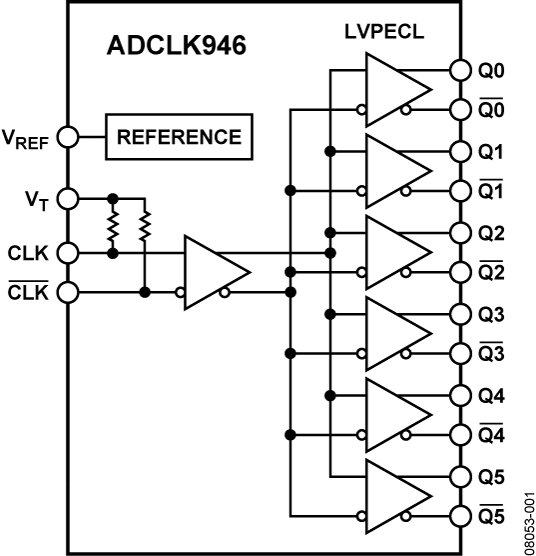

這款器件具有一個帶中心抽頭、差分、100 Ω片上端接電阻的差分輸入。支持直流耦合LVPECL、CML和3.3 V CMOS(單端)和交流耦合1.8 V CMOS、LVDS和LVPECL輸入。VREF引腳可用來為交流耦合輸入提供偏置。

ADCLK946具有六個全擺幅的發射極耦合邏輯(ECL)輸出驅動器。對于LVPECL(正ECL)輸出,將VCC偏置到正電源, VEE偏置到地。對于ECL輸出,將VCC偏置到地,VEE偏置到負電源。

ECL輸出級設計成將每端800 mV直接驅動至端接于VCC至2 V的50 Ω電阻,從而獲得1.6 V的總差分輸出擺幅。

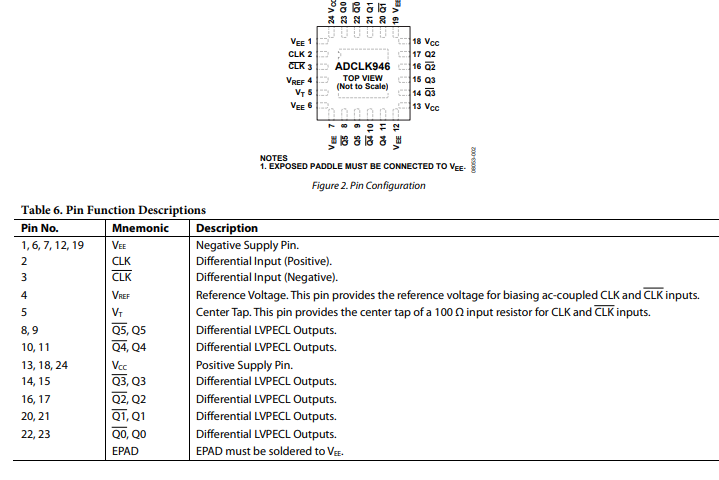

ADCLK946采用24引腳LFCSP封裝,額定工作溫度范圍為?40℃至+85℃的標準工業溫度范圍。

數據表:*附件:ADCLK946采用SiGe工藝的6 LVPECL輸出時鐘扇出緩沖器技術手冊.pdf

應用

特性

- 工作頻率:4.8 GHz

- 寬帶隨機抖動:75 fs

- 片上輸入端接

- 3.3 V電源

框圖

引腳配置描述

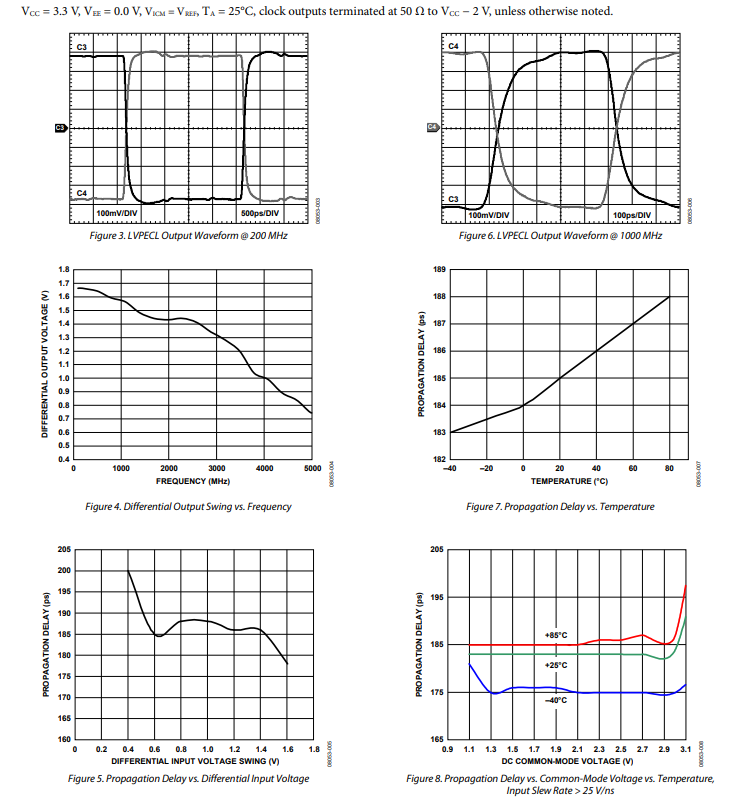

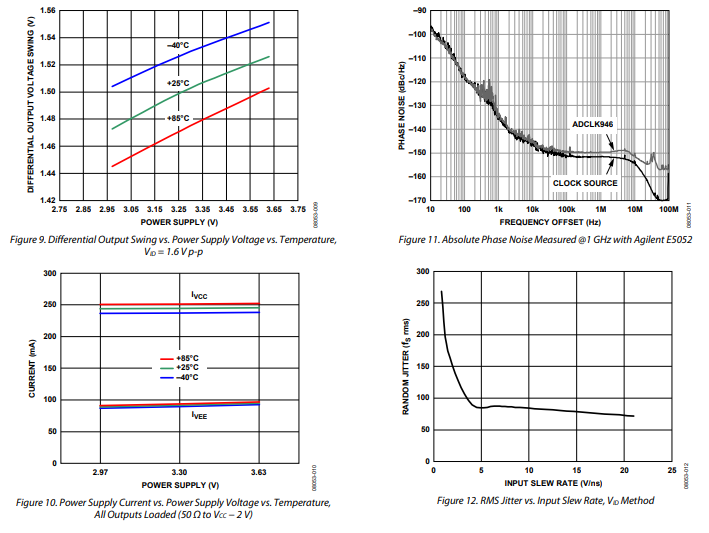

典型性能特征

功能描述

時鐘輸入

ADCLK946接收一個差分時鐘輸入,并將其分配到所有LVPECL輸出。規定的最大頻率是輸出電壓擺幅為標準LVPECL擺幅50%時的點(見圖4)。

該器件具有一個配備中心抽頭差分的100 Ω片上端接電阻的自由運行輸入。該輸入可接受交流耦合的1.8 V CMOS、LVDS和LVPECL輸入。有一個Vaux引腳可用于為交流耦合輸入提供偏置(見圖1)。將差分輸入電壓擺幅保持在約400 mV峰峰值至不超過3.4 V峰峰值之間。有關各種時鐘輸入端接方案,請見圖14 - 圖17。

如圖12所示,輸入斜率低于1 V/ns時,輸出抖動性能會下降。ADCLK946經過專門設計,可在較寬的輸入斜率范圍內將額外的隨機抖動降至最低。只要有可能,應使用快速肖特基二極管衰減器來降低過大輸入信號的斜率,因為衰減器應采用低損耗電介質或具有良好高頻特性的電纜。

時鐘輸出

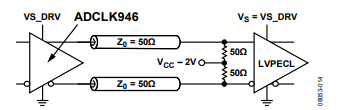

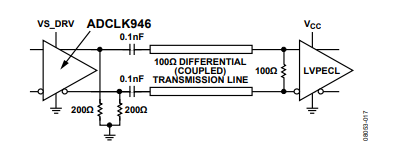

規定的性能要求使用合適的傳輸線終端。ADCLK946的LVPECL輸出旨在直接驅動800 mV至50 Ω電纜,或驅動至以VCC - 2 V為參考端接50 Ω的微帶線/帶狀線傳輸線,如圖14所示。LVPECL輸出級如圖13所示。這些輸出經過優化,可實現最佳的線路匹配。如果高速信號布線長度超過一厘米,無論是微帶線還是帶狀線技術,都需要適當的傳輸線端接,以確保正確的定時,并防止過度的輸出振鈴和與脈沖寬度相關的傳播延遲色散。

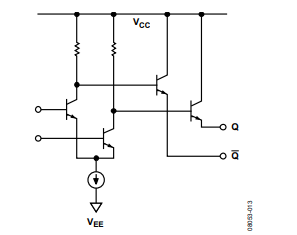

圖13. LVPECL輸出級的簡化示意圖

圖14 - 圖17描繪了各種直流耦合的LVPECL輸出端接方案。當直流耦合時,接收緩沖器的V?應與VS_DRV匹配。

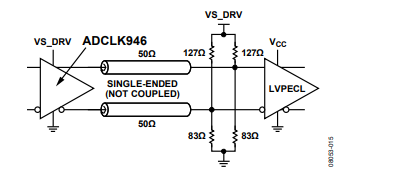

戴維南等效端接使用電阻網絡為LVPECL驅動器提供50 Ω直流端接,該直流電壓低于VS_DRV。在此方案中,VS_DRV上的直流偏置點應等于接收緩沖器的V?。盡管圖15所示的電阻組合會產生VS_DRV - 2 V的直流偏置點,但實際的共模電壓為VS_DRV - 1.3 V,因為有額外電流從ADCLK946 LVPECL驅動器的下拉電阻流出。

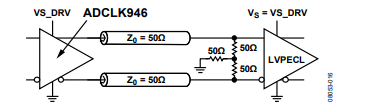

LVPECL Y端接是一種出色的端接方案,它使用最少的組件,同時提供奇模和偶模阻抗匹配。偶模阻抗匹配在高頻下緊密耦合傳輸線時很重要。其主要缺點是,它在改變LVPECL驅動器射極跟隨器的驅動強度方面靈活性有限。在驅動長走線時,這通常不是問題。

圖14. 直流耦合,3.3 V LVPECL

圖15. 直流耦合,3.3 V LVPECL 遠端戴維南端接

圖16. 直流耦合,3.3 V LVPECL Y端接

圖17. 交流耦合,帶并行傳輸線的LVPECL

-

緩沖器

+關注

關注

6文章

2048瀏覽量

46957 -

SiGe

+關注

關注

0文章

99瀏覽量

24017 -

時鐘

+關注

關注

11文章

1895瀏覽量

133128

發布評論請先 登錄

ADCLK946是否可以直接給AD9739作為時鐘驅動LVDS

ADCLK946,pdf datasheet (SiGe C

低電壓輸出SiGe時鐘扇出緩沖器的adclk94數據表

ADCLK946 采用SiGe工藝的6 LVPECL輸出時鐘扇出緩沖器

ADCLK846:1.8 V、6 LVDS/12 CMOS輸出低功耗時鐘扇出緩沖器

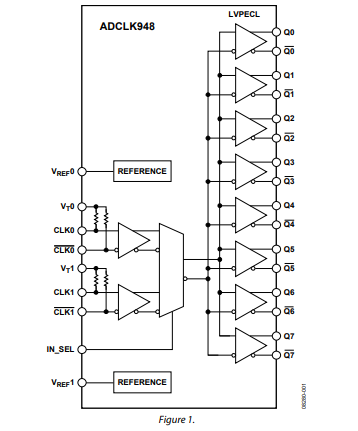

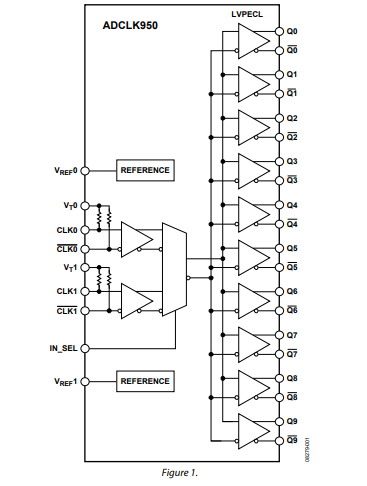

ADCLK950:兩個可選輸入、10個LVPECL輸出、SiGe時鐘扇出緩沖器數據表

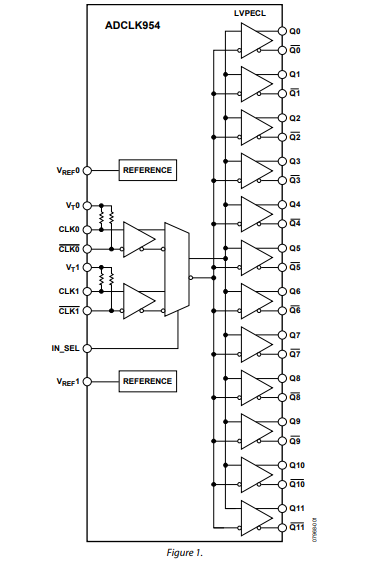

ADCLK954:兩個可選輸入、12個LVPECL輸出、SiGe時鐘扇出緩沖器數據表

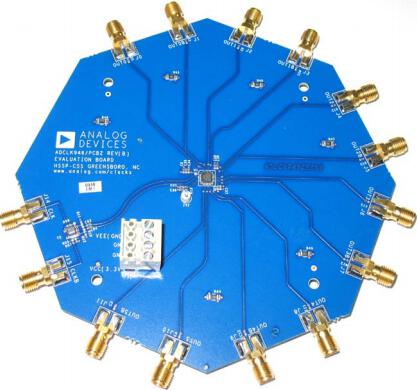

基于ADCLK946/PCBZ時鐘緩沖器的參考設計

ADCLK946采用SiGe工藝的6 LVPECL輸出時鐘扇出緩沖器技術手冊

ADCLK946采用SiGe工藝的6 LVPECL輸出時鐘扇出緩沖器技術手冊

評論