文章來(lái)源:半導(dǎo)體與物理

原文作者:jjfly686

本文介紹了在芯片制造中的應(yīng)變硅技術(shù)的原理、材料選擇和核心方法。

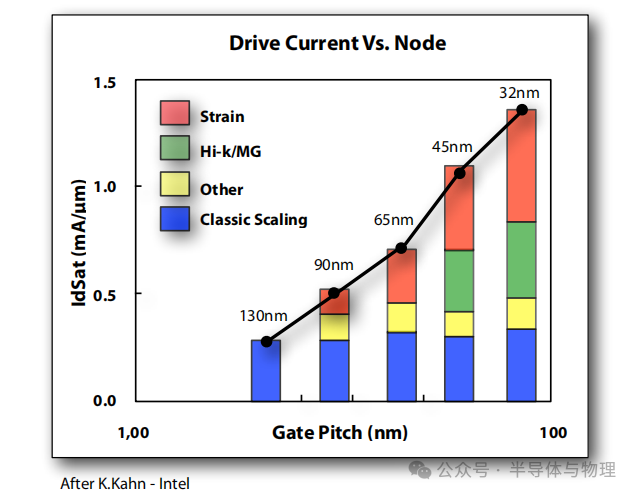

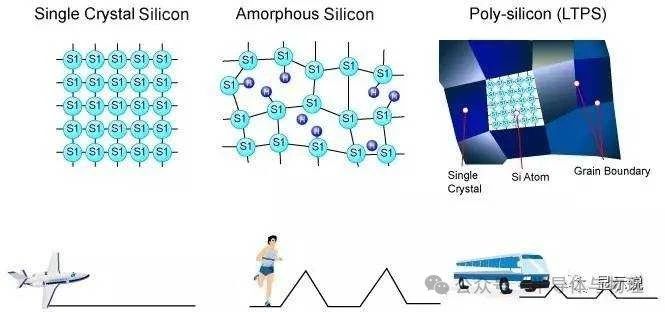

隨著晶體管尺寸進(jìn)入納米級(jí),傳統(tǒng)硅基器件的性能面臨物理極限,包括量子隧穿效應(yīng)導(dǎo)致漏電流激增,柵介質(zhì)變薄引發(fā)遷移率退化,以及短溝道效應(yīng)加劇。應(yīng)變硅技術(shù)通過(guò)對(duì)溝道施加機(jī)械應(yīng)力改變硅晶格結(jié)構(gòu),從而優(yōu)化載流子遷移率,成為延續(xù)摩爾定律的關(guān)鍵手段。

PMOS與NMOS的材料選擇:SiGe與SiC

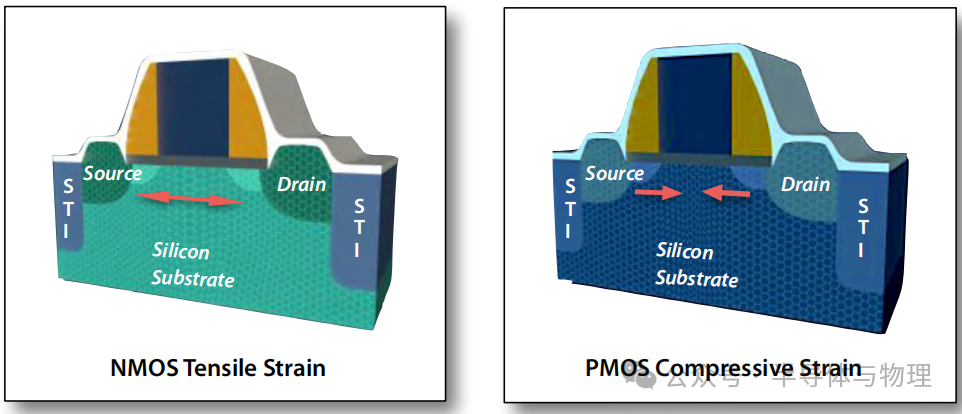

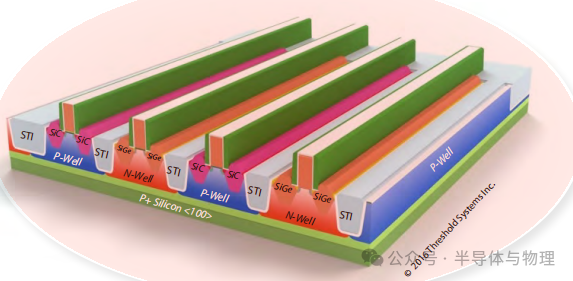

為了分別滿足PMOS(空穴導(dǎo)電)和NMOS(電子導(dǎo)電)的需求,需采用不同材料引入特定應(yīng)力:

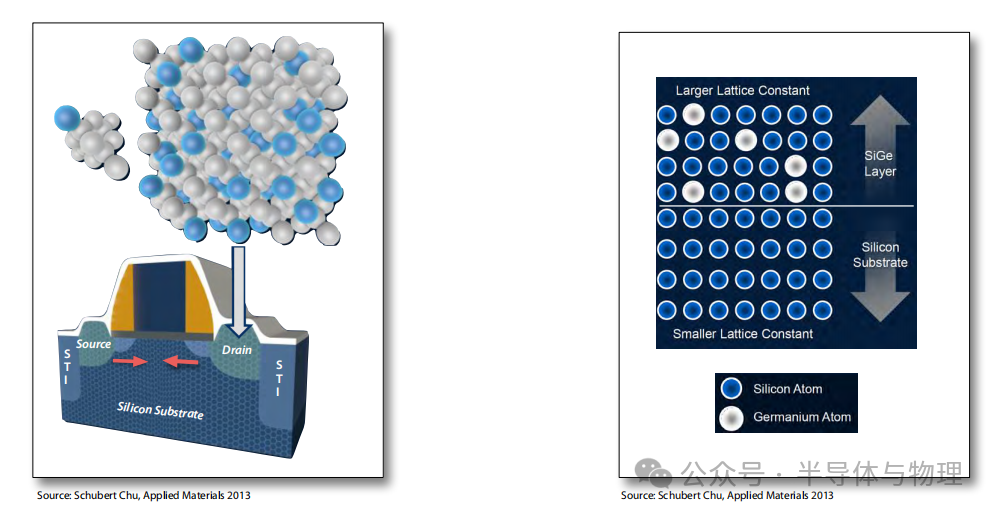

PMOS:SiGe(鍺硅合金)引入壓應(yīng)力

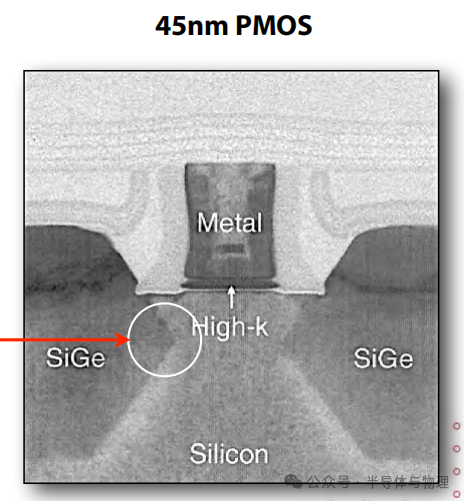

鍺(Ge)的晶格常數(shù)比硅大4.2%。當(dāng)PMOS的源漏區(qū)替換為SiGe時(shí),其晶格膨脹會(huì)擠壓溝道硅層,產(chǎn)生壓應(yīng)力,使空穴遷移率提升50%以上。在20 nm節(jié)點(diǎn)中,SiGe中鍺含量達(dá)55%,通過(guò)優(yōu)化外延層位置(如將SiGe晶體邊緣靠近溝道)進(jìn)一步增強(qiáng)應(yīng)力。

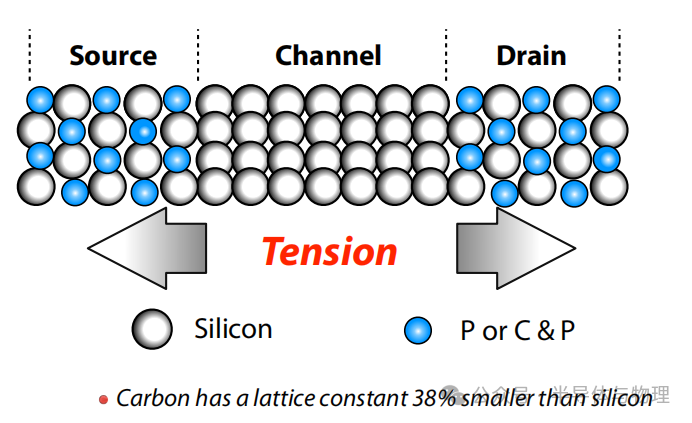

NMOS:SiC(碳化硅)或摻碳/磷硅引入張應(yīng)力

碳(C)的晶格常數(shù)比硅小38%。在NMOS源漏區(qū)引入摻碳硅外延層(如Si:C或Si:C/P),可拉伸溝道晶格,產(chǎn)生張應(yīng)力,使電子遷移率提升20%。需平衡材料穩(wěn)定性與應(yīng)力強(qiáng)度。例如,碳摻雜需精確控制濃度以避免晶格缺陷。

應(yīng)變引入的核心方法

選擇性外延替換源漏區(qū)

刻蝕原有源漏區(qū)→外延生長(zhǎng)SiGe(PMOS)或Si:C(NMOS)→退火激活摻雜原子。

應(yīng)力記憶技術(shù)(Stress Memorization Technique, SMT)

通過(guò)掩膜邊緣位錯(cuò)誘導(dǎo)張應(yīng)力。例如,在45/32 nm節(jié)點(diǎn)中,采用預(yù)非晶化離子注入(PAI)+氮化硅應(yīng)力覆蓋層,退火后形成位錯(cuò),提升NMOS短溝道遷移率10%。

-

NMOS

+關(guān)注

關(guān)注

3文章

358瀏覽量

35495 -

晶體管

+關(guān)注

關(guān)注

77文章

10002瀏覽量

141120 -

芯片制造

+關(guān)注

關(guān)注

10文章

681瀏覽量

29618

原文標(biāo)題:芯片制造中的應(yīng)變硅技術(shù)

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

硅襯底LED芯片主要制造工藝

【「大話芯片制造」閱讀體驗(yàn)】+ 芯片制造過(guò)程和生產(chǎn)工藝

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測(cè)

可控硅及組件-廠家介紹

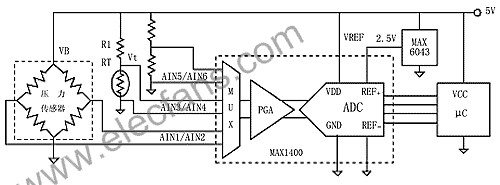

如何實(shí)現(xiàn)具有較大信號(hào)輸出的硅應(yīng)變計(jì)與ADC的接口

硅光芯片的優(yōu)勢(shì)/市場(chǎng)定位及行業(yè)痛點(diǎn)

如何實(shí)現(xiàn)較大信號(hào)輸出的硅應(yīng)變計(jì)與模數(shù)轉(zhuǎn)換器(ADC)的接口

源漏嵌入SiC應(yīng)變技術(shù)簡(jiǎn)介

源漏嵌入SiGe應(yīng)變技術(shù)簡(jiǎn)介

先進(jìn)封裝中的TSV/硅通孔技術(shù)介紹

SiGe外延工藝及其在外延生長(zhǎng)、應(yīng)變硅應(yīng)用及GAA結(jié)構(gòu)中的作用

深入解析硅基光子芯片制造流程,揭秘科技奇跡!

芯片制造中的應(yīng)變硅技術(shù)介紹

芯片制造中的應(yīng)變硅技術(shù)介紹

評(píng)論