概述

MAX9320/MAX9320A是一種低扭曲、1:2差分驅(qū)動(dòng)器設(shè)計(jì)用于時(shí)鐘和數(shù)據(jù)分配,由一路輸入再生2路差分輸出。差分輸入經(jīng)過調(diào)整后,可以允許單端輸入,只需外加基準(zhǔn)電壓即可。

MAX9320/MAX9320A具有超低傳輸延遲(208ps)、20ps的器件至器件扭曲和6ps的輸出至輸出扭曲以及最大30mA的電源電流等特性,使其尤其適合于時(shí)鐘分配。為與差分HSTL和LVPECL信號(hào)接口,該器件工作于+2.25V至+3.8V的電源電壓,能夠?qū)崿F(xiàn)在+2.5V或+3.3V標(biāo)稱電壓系統(tǒng)中,進(jìn)行高性能的時(shí)鐘或數(shù)據(jù)分配。而對(duì)于差分LVECL工作方式,該器件工作于-2.25V至-3.8V的電源電壓。

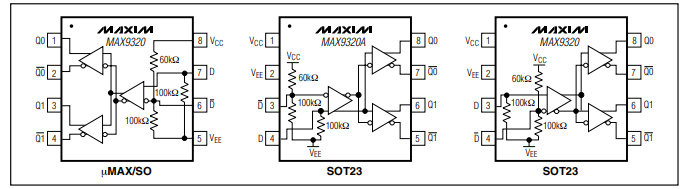

MAX9320和MAX9320A的唯一區(qū)別是引腳排列不同。為簡(jiǎn)化背板與雙面電路板任何一面的布線連接,提供有多種引腳排列。

這些器件提供節(jié)省空間的8引腳SOT23、μMAX?和SO封裝。

數(shù)據(jù)表:*附件:MAX9320 MAX9320A 1比2差分LVPECL LVECL HSTL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè).pdf

應(yīng)用

- 低抖動(dòng)數(shù)據(jù)中繼器

- 精密時(shí)鐘分配

- 保護(hù)開關(guān)

特性

- 改進(jìn)的MC10LVEP11 (MAX9320)代用產(chǎn)品

- +2.25V至+3.8V差分HSTL/LVPECL工作方式

- -2.25V至-3.8V LVECL工作方式

- 22mA (典型)的低電源電流

- 20ps (典型)器件至器件扭曲

- 6ps (典型)輸出至輸出扭曲

- 208ps (典型)的傳輸延遲

- 3GHz時(shí)最小輸出300mV

- 輸入開路時(shí),輸出為低電平

2kV的ESD保護(hù)(人體模型)

- 提供熱增強(qiáng)型、底盤裸露的SO封裝

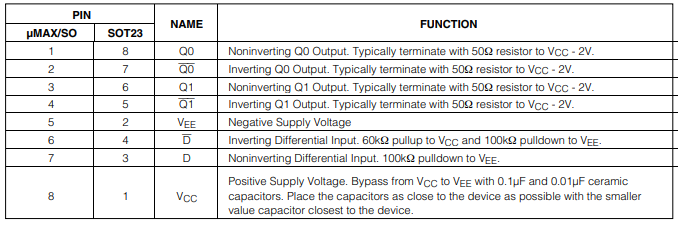

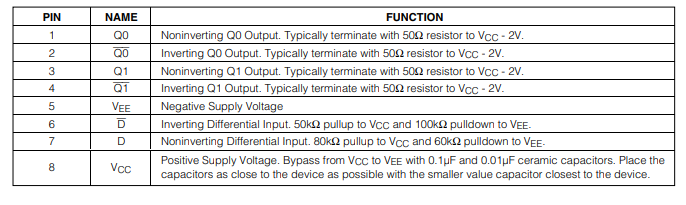

引腳配置描述

典型操作特性

詳細(xì)說明

MAX9320/MAX9320A是低偏斜的1:2差分驅(qū)動(dòng)器,專為時(shí)鐘和數(shù)據(jù)分配而設(shè)計(jì)。為了與差分HSTL和LVPECL信號(hào)進(jìn)行接口,這些器件在+2.25V至+3.8V的電源電壓范圍內(nèi)工作,能夠在具有標(biāo)稱+2.5V或+3.3V電源的系統(tǒng)中實(shí)現(xiàn)高性能的時(shí)鐘和數(shù)據(jù)分配。對(duì)于差分LVECL工作模式,這些器件的工作電壓范圍為+2.25V至+3.8V。

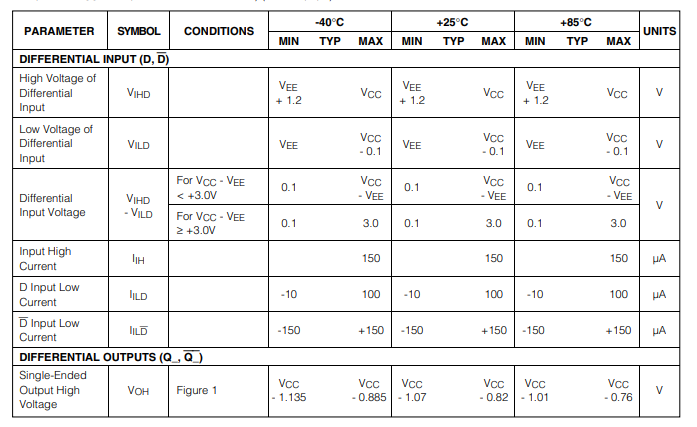

從D到D的差分輸入的最大幅度為VCC - VEE或3.0V(取較小值)。此限制也適用于任何參考電壓輸入與單端輸入之間的差值。

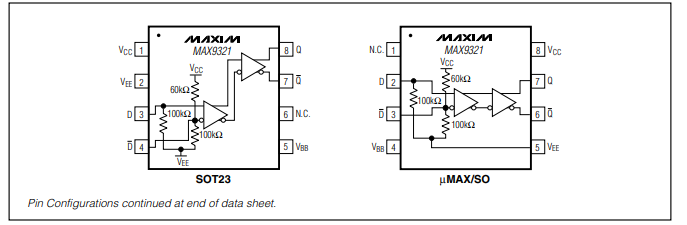

差分輸入具有偏置電阻,當(dāng)輸入開路時(shí),會(huì)將輸出驅(qū)動(dòng)為差分低電平。反相輸入D通過一個(gè)60kΩ上拉電阻偏置到Vcc,通過一個(gè)100kΩ下拉電阻偏置到VEE。同相輸入D通過一個(gè)100kΩ下拉電阻偏置到VEE。差分輸入電壓的高電平和低電平(VHD和VLD)以及差分輸入電壓(VIH - VIL)需同時(shí)滿足要求(VLD不能高于VHD)。

輸出電平以Vcc為參考,根據(jù)Vcc電源的電平,被視為L(zhǎng)VPECL或LVECL。當(dāng)Vcc連接到地且VEE連接到負(fù)電源時(shí),輸出為L(zhǎng)VPECL。當(dāng)Vcc連接到正電源且VEE連接到地時(shí),輸出為L(zhǎng)VECL。

以參考電壓為中心、幅度約為±100mV的單端輸入,或差分輸入的幅度至少為±100mV時(shí),可將輸出切換到直流電氣特性表中規(guī)定的VOH和VOL電平。

應(yīng)用信息

電源去耦

用0.1μF和0.01μF的高頻表面貼裝陶瓷電容將Vcc旁路到VEE,盡可能將電容靠近器件安裝,0.01μF電容最靠近器件。使用多個(gè)并聯(lián)過孔,以最小化電感。

走線

輸入和輸出走線特性會(huì)影響MAX9320/MAX9320A的性能。將差分輸入或輸出信號(hào)連接到50Ω特性阻抗的走線。盡量減少過孔數(shù)量,以防止阻抗不連續(xù)。通過匹配連接器和電纜保持50Ω特性阻抗,減少反射。通過匹配走線的電氣長(zhǎng)度,減少差分對(duì)內(nèi)的偏移。

外露焊盤(EP)SO封裝可焊接到PC板上,以增強(qiáng)熱性能。如果EP未焊接到PC板上,熱阻與常規(guī)SO封裝相同。EP連接到芯片的VEE電源。此外,應(yīng)確保焊盤不與其他電源接觸。有關(guān)EP封裝的使用指南,請(qǐng)聯(lián)系美信(Maxim)封裝部門。

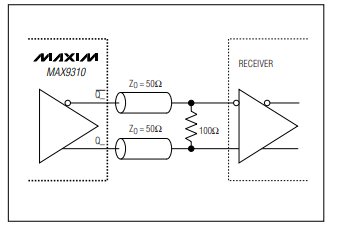

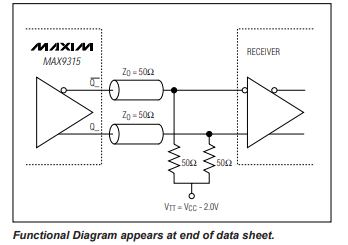

輸出端接

通過50Ω電阻將輸出端接到Vcc - 2V,或使用等效的戴維南端接。同時(shí)端接兩個(gè)輸出,并使用相同的端接方式,以實(shí)現(xiàn)最低的輸出間偏斜。當(dāng)從差分輸出獲取單端信號(hào)時(shí),需同時(shí)端接兩個(gè)輸出。例如,如果Q0用作單端輸出,則需同時(shí)端接Q0和Q0。

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8646瀏覽量

149236 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132919 -

差分驅(qū)動(dòng)器

+關(guān)注

關(guān)注

0文章

65瀏覽量

15541 -

數(shù)據(jù)分配

+關(guān)注

關(guān)注

0文章

2瀏覽量

5284

發(fā)布評(píng)論請(qǐng)先 登錄

MAX9320BEUA+T - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320EKA+T - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320BEUA+ - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320BESA+ - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320EUA+T - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320EUA+ - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320ESA+ - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9320ESA+T - (Maxim Integrated) - 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘緩沖器,驅(qū)動(dòng)器

MAX9321差分LVPECL/LVECL/HSTL接收器/驅(qū)動(dòng)器技術(shù)手冊(cè)

MAX9310 1:5時(shí)鐘驅(qū)動(dòng)器,可選的LVPECL輸入與LVDS輸出技術(shù)手冊(cè)

MAX9320B 1:2差分PECL/ECL/LVPECL/LVECL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè)

MAX9315 1:5差分LVPECL/LVECL/HSTL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè)

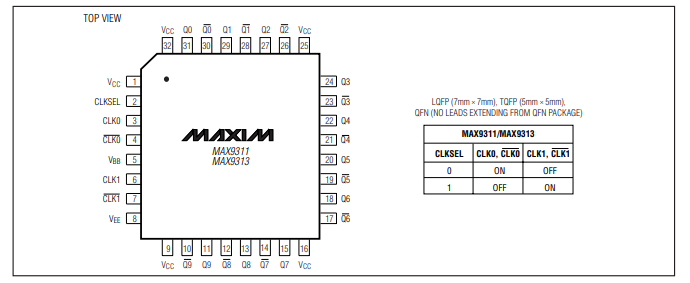

MAX9311/MAX9313 1:10差分LVPECL/LVECL/HSTL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè)

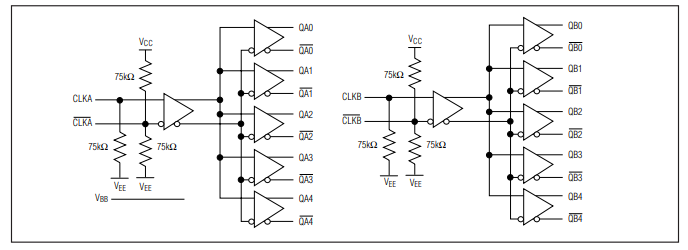

MAX9312/MAX9314雙路、1:5差分LVPECL/LVECL/HSTL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè)

MAX9320/MAX9320A 1:2差分LVPECL/LVECL/HSTL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè)

MAX9320/MAX9320A 1:2差分LVPECL/LVECL/HSTL時(shí)鐘和數(shù)據(jù)驅(qū)動(dòng)器技術(shù)手冊(cè)

評(píng)論