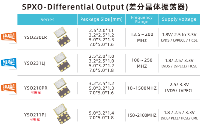

FCom FCO系列差分輸出晶體振蕩器涵蓋2.5×2.0至7.0×5.0多種封裝,提供LVPECL、LVDS與HCSL三種標(biāo)準(zhǔn)接口,頻率支持13.5MHz至220MHz,并具有出色的相位抖動(dòng)指標(biāo)(典型值0.15~0.3 ps RMS)。本指南將基于應(yīng)用場景總結(jié)輸出類型、電氣匹配建議及典型芯片平臺,輔助系統(tǒng)設(shè)計(jì)工程師快速完成時(shí)鐘器件選型。

一、差分輸出格式選擇建議

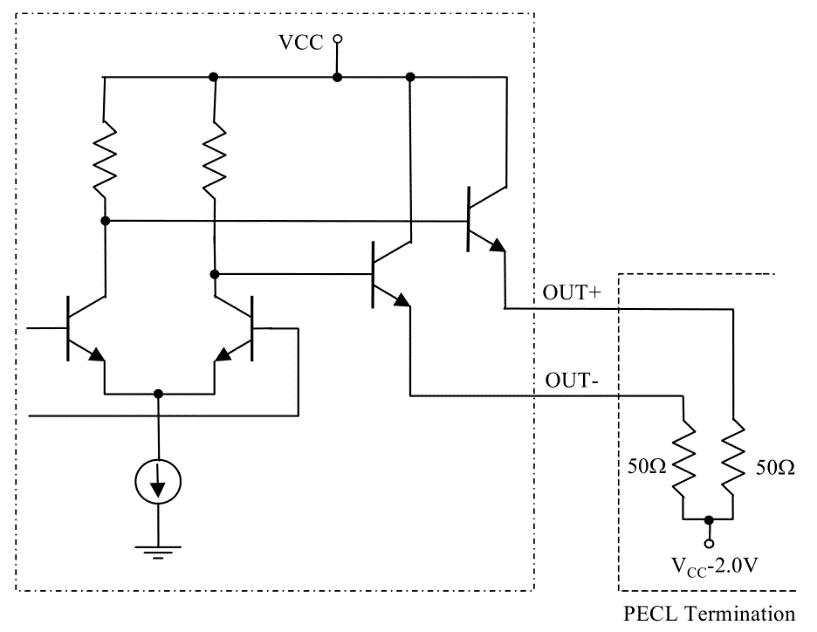

- LVPECL:推薦用于高速SerDes與光模塊,驅(qū)動(dòng)能力強(qiáng),需終端電阻至VDD-2V。

- LVDS:低功耗、低EMI,適合ADC/DAC、PHY、同步SoC等差分輸入器件,建議100Ω差分端接。

- HCSL:專為PCIe總線接口設(shè)計(jì),使用50Ω至GND端接,適用于主板類系統(tǒng)。

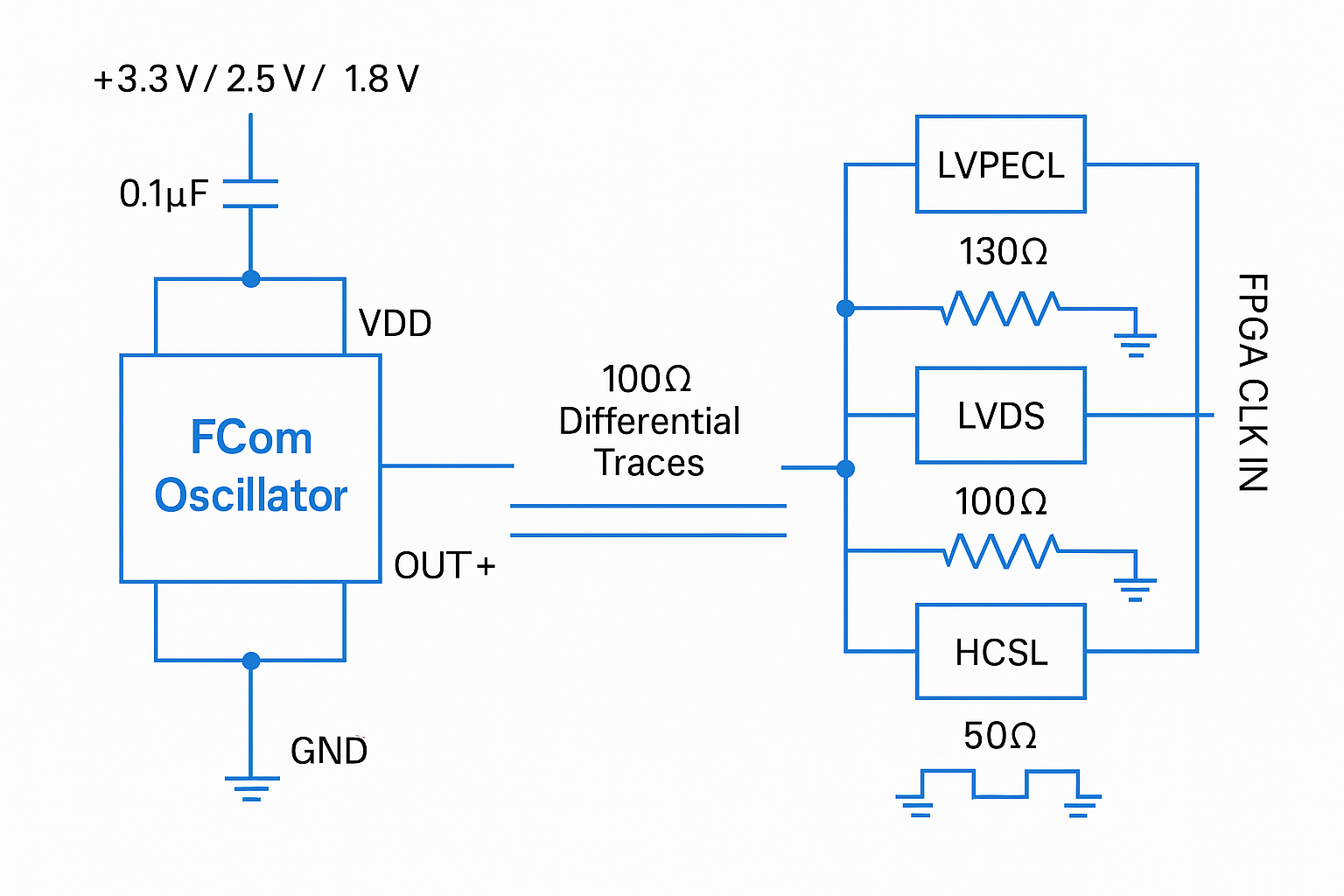

二、電源布局與信號布線建議

- 在VDD與GND之間緊貼晶振器件放置0.1μF去耦電容,可顯著抑制電源噪聲傳導(dǎo)。

- 差分輸出建議使用等長等阻抗布線(100Ω),避免跨層不連續(xù)與異層參考地問題。

- HCSL信號需每路接入50Ω至GND的終端電阻。

三、參考原理圖結(jié)構(gòu)

原理圖布局結(jié)構(gòu)

原理圖布局結(jié)構(gòu)四、封裝與系統(tǒng)平臺部署建議

- FCO-2L:適合SFP光模塊、無線模組、尺寸敏感設(shè)計(jì)

- FCO-3L:主流嵌入式平臺與同步接口控制模塊

- FCO-5L:網(wǎng)絡(luò)設(shè)備、交換機(jī)主板、工業(yè)控制系統(tǒng)

- FCO-7L:高頻服務(wù)器主板、基站控制板、大功耗場景

五、差分晶體振蕩器典型芯片匹配方案

在差分晶體振蕩器的系統(tǒng)設(shè)計(jì)中,確保時(shí)鐘信號與接收芯片的電氣特性完美匹配,是保證整體時(shí)序穩(wěn)定與抖動(dòng)抑制的關(guān)鍵。FCom在長期產(chǎn)品應(yīng)用過程中,歸納出覆蓋SerDes、高速ADC/DAC、以太網(wǎng)PHY、時(shí)鐘清理器、SoC平臺、光通信控制器及PCIe等多個(gè)核心應(yīng)用的推薦芯片搭配表。

應(yīng)用類型 | 芯片型號 | 芯片特點(diǎn)與說明 | FCom推薦型號 | 推薦頻率 | 推薦輸出模式 |

| SerDes芯片 | Analog Devices ADN2817 | SONET/SDH CDR,需LVPECL時(shí)鐘輸入 | FCO-2L | 155.52 MHz | LVPECL |

| SerDes芯片 | Semtech GN2104 | 10G/25G SerDes,常用于SFP+/QSFP模塊 | FCO-2L | 156.25 MHz | LVPECL |

| SerDes芯片 | MACOM M37046 | 28G/56G SerDes,應(yīng)用于高速有源線纜 | FCO-2L | 161.1328 MHz | LVPECL |

| SerDes芯片 | TI DS100BR410 | 3.125~10.3Gbps差分驅(qū)動(dòng)器 | FCO-3L | 100 MHz | LVDS |

| 光模塊控制器 | Semtech GN2104 | 集成CDR,適用于10G光模塊 | FCO-2L | 155.52 MHz | LVPECL |

| 高速ADC/DAC | ADI AD9208 | 14-bit, 3GSPS JESD204B接口 | FCO-5L | 122.88 MHz | LVDS |

| 高速ADC/DAC | TI DAC38RF82 | JESD204B高速DAC | FCO-5L | 122.88 MHz | LVDS |

| PHY芯片 | Marvell 88X3310 | 多速率以太網(wǎng)PHY | FCO-3L | 156.25 MHz | LVDS |

| SoC芯片 | NXP LX2160A | 16核網(wǎng)絡(luò)處理器 | FCO-5L | 100 MHz | LVDS |

| 時(shí)鐘芯片 | TI LMK04828 | 低抖動(dòng)時(shí)鐘清理分配器 | FCO-3L | 100 MHz | LVDS |

| PCIe控制器 | Renesas 9DB206 | x16 PCIe緩沖芯片 | FCO-7L | 100 MHz | HCSL |

六、常見問題與解決方案

問題 | 可能原因 | 建議措施 |

| 輸出抖動(dòng)大 | 電源噪聲或布局不良 | 靠近VDD放置去耦電容,走線對稱 |

| 頻率漂移明顯 | 未終端或負(fù)載影響 | 確認(rèn)終端阻抗,選用±25ppm或更嚴(yán)精度型號 |

| 啟動(dòng)無輸出 | OE引腳控制邏輯錯(cuò)誤 | 拉高或懸空OE測試基本功能 |

| 信號擺幅不符 | 接口類型配置不匹配 | 核對輸出模式與接收芯片規(guī)范 |

| 溫度變化頻偏 | 選型溫寬不足 | 選用-40~125℃寬溫版本 |

-

soc

+關(guān)注

關(guān)注

38文章

4356瀏覽量

221877 -

SerDes

+關(guān)注

關(guān)注

7文章

211瀏覽量

35634 -

LVDS信號

+關(guān)注

關(guān)注

0文章

18瀏覽量

7975 -

差分晶振

+關(guān)注

關(guān)注

0文章

135瀏覽量

570

發(fā)布評論請先 登錄

從SFP到OSFP:FCom差分晶振覆蓋全類型光模塊的時(shí)鐘設(shè)計(jì)方案

小型數(shù)據(jù)中心晶振選型關(guān)鍵參數(shù)全解

從SerDes到SoC,全場景適配的FCom差分晶振設(shè)計(jì)全解

從25G PHY到AI平臺:差分晶振FCO-PG系列關(guān)鍵應(yīng)用全解讀

晶振家族大揭秘:從石英晶振到陶瓷晶振,各具神通

27MHz HCSL晶體振蕩器選型與PHY對接設(shè)計(jì)指南

FPGA是什么?應(yīng)用領(lǐng)域、差分晶振作用及常用頻率全面解析

FCX-1S超小型高精度晶振——FCom富士晶振助力物聯(lián)網(wǎng)、5G、汽車電子

從SerDes到SoC,全場景適配的FCom差分晶振設(shè)計(jì)全解

從SerDes到SoC,全場景適配的FCom差分晶振設(shè)計(jì)全解

評論