在USB PD快充電源設計中,MOSFET作為功率控制與轉換的核心器件,發揮著關鍵作用。隨著充電功率向65W、100W甚至更高邁進,對MOSFET的性能提出了更嚴苛的挑戰。本文將從應用挑戰出發,結合FAE工程實踐,分析MOSFET在USB PD快充中的關鍵設計要求與應對策略。

一、應用背景:MOSFET在USB PD快充中的位置

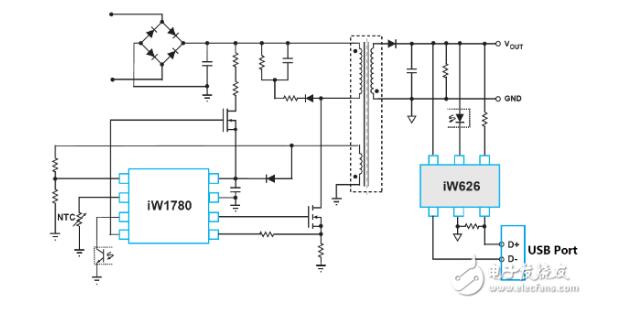

USB PD(Power Delivery)協議允許設備間進行動態電壓電流協商,實現高功率傳輸。無論是AC-DC整流端、DC-DC升降壓變換、同步整流,還是輸出保護與切換,MOSFET都被廣泛應用。它們通常處于高頻開關狀態,因此其導通損耗、開關損耗、熱性能、可靠性對整個PD電源的效率與穩定性至關重要。

二、核心挑戰

高頻切換導致的EMI與開關損耗

USB PD電源采用高頻PWM控制(一般在65~200kHz),MOSFET頻繁開關,帶來嚴重的dv/dt與di/dt應力,容易產生EMI干擾,增加PCB布線與濾波器設計難度。

低RDS(on)與體積限制的矛盾

為提升效率,設計者傾向于選用低RDS(on) MOSFET,但在小型化的PD適配器中,過大封裝會帶來熱散不良與體積不兼容的問題。

熱管理困難

PD適配器多為封閉結構,MOSFET所產生的熱量難以快速導出,特別是在同步整流部分,容易形成局部過熱,影響器件壽命。

浪涌與瞬態電壓挑戰

在PD電源插拔、短路、負載突變等狀態下,MOSFET需承受瞬時高壓/大電流,應具備良好的安全裕度與ESD能力。

三、FAE推薦的設計策略

合理選型:關注RDS(on)、Qg與封裝的綜合平衡

對于DC-DC主開關部分,需綜合考慮MOSFET的導通電阻與總柵電荷(Qg)。低Qg器件可減少驅動損耗并降低EMI。在同步整流部分,RDS(on)尤為關鍵。推薦選用采用Super Junction或Trench結構的MOSFET,并優先考慮DFN5x6、PDFN3x3等熱性能優異的小封裝產品。

開關調速+緩沖設計降低EMI

MOSFET柵極驅動應避免過快開通或關斷,建議使用合適的柵極電阻以平衡速度與EMI。必要時可在MOSFET兩端并聯TVS、RC緩沖或Snubber電路,吸收尖峰電壓。

優化PCB熱設計

大面積銅箔散熱+過孔導熱是控制MOSFET溫升的重要手段。建議布板時將MOSFET靠近PCB邊緣布置,同時將其焊盤與內層大面積銅連接,提升散熱效率。

提升系統魯棒性

選用具備良好雪崩能力與ESD保護的MOSFET,能有效應對插拔沖擊與突變干擾。建議器件VDS額定值至少為工作電壓的1.5倍以上。

辰達MOSFET在USB PD快充電源中面臨高頻、高效率、小尺寸、高可靠性的多重挑戰。作為FAE,我們建議設計人員不僅要關注參數指標,還需在系統熱、電、EMI性能之間做出平衡。通過科學選型、合理布局與適當的外圍電路設計,方能打造出高性能、高可靠性的USB PD快充方案。

-

MOSFET

+關注

關注

150文章

8527瀏覽量

220068 -

MOS

+關注

關注

32文章

1357瀏覽量

96855 -

USB PD

+關注

關注

3文章

54瀏覽量

25687

發布評論請先 登錄

如何應對USB PD在移動設備中快速充電的新挑戰?

什么是PD充電協議?

PD快充協議芯片,支持USB PD 3.0

PD快充協議芯片,PD3.0芯片

usb pd快充是目前主流的快充協議之一

入門:USB type C和USB PD快充充電協議

芯海科技CPW6410:集成PD快充與UFCS,高效、可靠的快充電源解決方案

淺談辰達MOSFET在USB PD快充電源中的應用挑戰與應對

淺談辰達MOSFET在USB PD快充電源中的應用挑戰與應對

評論