時(shí)間&地點(diǎn)

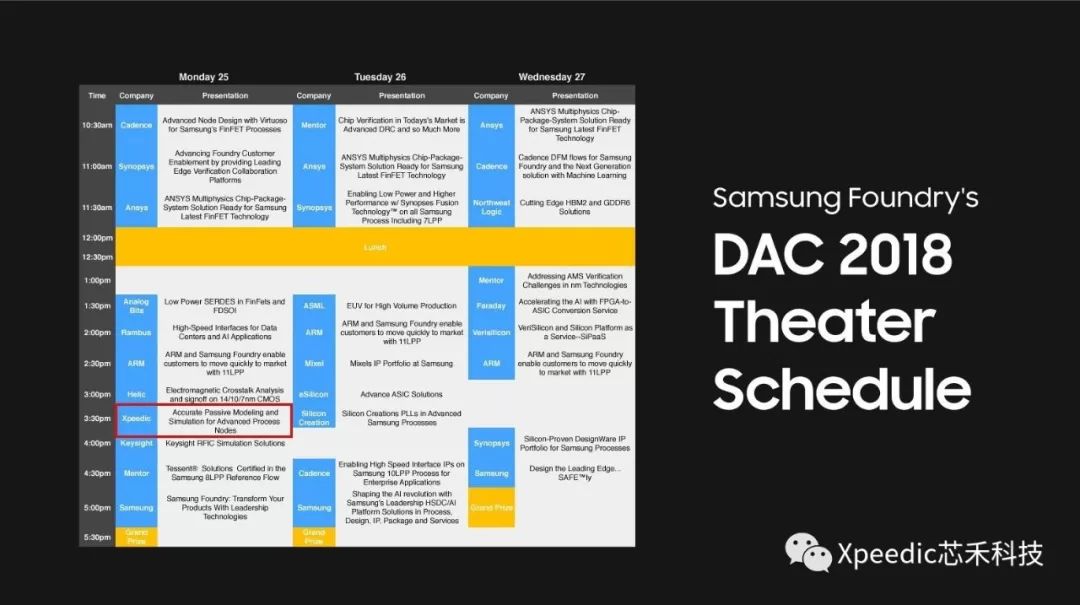

日期:2018年6月25-27日

地點(diǎn):舊金山, 美國(guó)

芯禾科技作為三星半導(dǎo)體的重要合作伙伴之一,受邀將參加下周一在美國(guó)舊金山舉行的DAC2018三星展區(qū)演示活動(dòng)。CEO凌峰博士屆時(shí)將發(fā)表題為“先進(jìn)工藝節(jié)點(diǎn)下的無(wú)源器件建模及仿真”的技術(shù)演講。

作為行業(yè)里普遍的觀點(diǎn),先進(jìn)工藝節(jié)點(diǎn)下無(wú)源器件和互連結(jié)構(gòu)的建模和仿真越來(lái)越成為半導(dǎo)體工程師的挑戰(zhàn)。而要解決這些挑戰(zhàn),以下幾個(gè)技術(shù)是最常被探討的:

一個(gè)整合的設(shè)計(jì)環(huán)境,使電磁仿真工具能夠無(wú)縫接入現(xiàn)有的設(shè)計(jì)平臺(tái)中

在設(shè)計(jì)階段中實(shí)現(xiàn)快速無(wú)源器件建模和合成

在簽核sign-off 階段實(shí)現(xiàn)精確驗(yàn)證,同時(shí)能把封裝的影響考慮進(jìn)來(lái)

在此次現(xiàn)場(chǎng)演講中,芯禾科技將演示一套集成的IRIS設(shè)計(jì)流程,它能無(wú)縫接入到Cadence Virtuoso設(shè)計(jì)平臺(tái)中,從而完全的解決半導(dǎo)體工程師遇到的以上熱點(diǎn)問(wèn)題。通過(guò)此流程,工程師不僅能在設(shè)計(jì)階段使用芯禾科技的IRIS和iModeler工具快速和精確地完成無(wú)源器件仿真和合成,還能在簽核階段通過(guò)與Ansys公司的合作把HFSS集成進(jìn)來(lái)實(shí)現(xiàn)精確驗(yàn)證以及芯片封裝聯(lián)合仿真。

除此之外,芯禾科技在DAC展會(huì)上也設(shè)有專屬展位(展位號(hào)2041),并將帶來(lái)多項(xiàng)現(xiàn)場(chǎng)演示,包括針對(duì)封裝領(lǐng)域的IPD與SiP設(shè)計(jì)電磁仿真解決方案以及針對(duì)高速系統(tǒng)的信號(hào)完整性分析解決方案。

我們期待與您在現(xiàn)場(chǎng)交流討論。

-

無(wú)源器件

+關(guān)注

關(guān)注

5文章

220瀏覽量

23921 -

三星半導(dǎo)體

+關(guān)注

關(guān)注

0文章

66瀏覽量

16950

原文標(biāo)題:芯禾科技技術(shù)演講@三星半導(dǎo)體DAC展區(qū)

文章出處:【微信號(hào):Xpeedic,微信公眾號(hào):Xpeedic】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Simcenter STAR-CCM+多相CFD仿真:自信對(duì)復(fù)雜的工業(yè)多相應(yīng)用精確建模

無(wú)源光纖能隨時(shí)斷網(wǎng)嗎

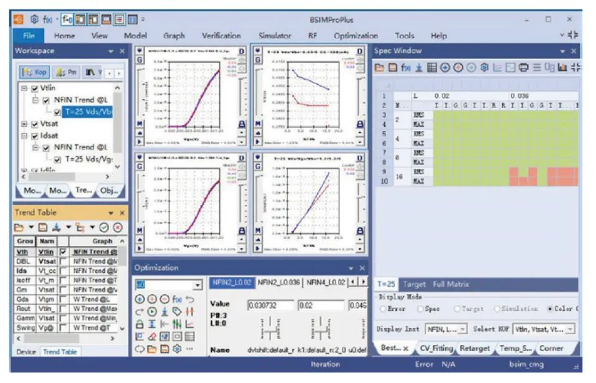

概倫電子先進(jìn)器件建模平臺(tái)BSIMProPlus介紹

先進(jìn)封裝工藝面臨的挑戰(zhàn)

SMT無(wú)鉛工藝對(duì)元器件的嚴(yán)格要求,你了解嗎?

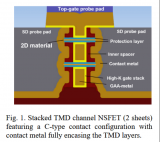

IEDM 2024先進(jìn)工藝探討(三):2D材料技術(shù)的進(jìn)展及所遇挑戰(zhàn)

ANN神經(jīng)網(wǎng)絡(luò)——器件建模

如何通過(guò)建模與仿真提升電力電子組件的設(shè)計(jì)與性能?

晶圓微凸點(diǎn)技術(shù)在先進(jìn)封裝中的應(yīng)用

如何實(shí)現(xiàn)更精確的電流限制并避免損壞受測(cè)器件

怎樣在先進(jìn)工藝節(jié)點(diǎn)下實(shí)現(xiàn)無(wú)源器件的精確建模及仿真?

怎樣在先進(jìn)工藝節(jié)點(diǎn)下實(shí)現(xiàn)無(wú)源器件的精確建模及仿真?

評(píng)論