引言

數字示波器自上個世紀七十年代誕生以來,它已成為測試工程師必備的工具之一。隨著近年來電子技術取得突破性的進展,催生了更龐大的數字示波器市場需求。此外,信號傳輸在現代工程中是很重要的一個技術環節,但在信號傳輸中,數字信號將對模擬信號產生干擾,目前采用的解決方法是利用單片機來實現模擬信號和數字信號在單線中的混合傳輸,而這其中的測試和調試就要求示波器必須能夠對數字信號和模擬信號同時進行分析和顯示。因此,這里介紹一種基于等效和實時采樣數字示波器的設計。

2 設計方案

2.1 采樣方案

選擇實時采樣和等效采樣相結合的方式,實時采樣速率小于1 MS/s,水平分辨率至少為20點/div,故系統50 kHz以下采用實時采樣方式,而50 kHz~10 MHz采用等效時間采樣方式,最高等效采樣速率可達到200 Ms/s。

2.2 頻率測量方案

由于該系統測試頻率上限為10 MHz。根據等精度測量和測周法原理,將此頻率分為兩段。因此,10 kHz以下頻率段,采用測周法;10 kHz以上的頻率段,采用等精度測量法,從而縮短測量時間。

2.3 觸發方案

采用內部軟件觸發,通過軟件設置觸發電平,軟件設置的施密特觸發器參數容易修改,可以很好抑制比較器產生的毛刺。當所采樣值大于該觸發電平時,產生一次觸發。該方案可排除硬件產生的毛刺干擾,觸發和波形較穩定,且易實現觸發電壓的調整。

2.4 采樣與保持電路方案

采用射極跟隨器、模擬開關和電容搭建采樣與保持電路。射極跟隨器可選用帶寬穩定且帶動容性負載強的運放,有較多的TI模擬開關,使其速度很容易滿足要求,再選用合適的漏電小的聚苯電容即可實現采樣與保持電路。

3 系統硬件電路設計

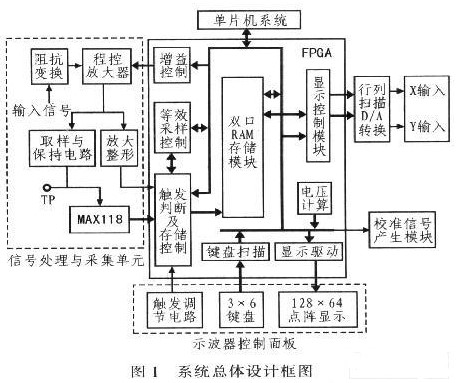

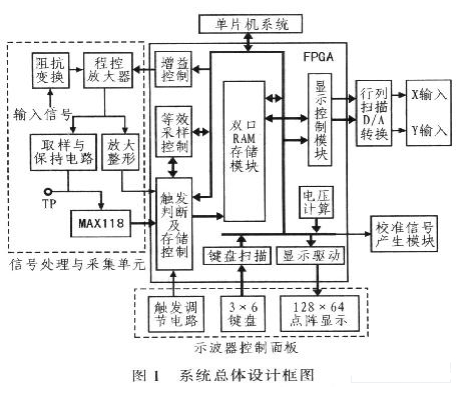

系統制定出系統總體方案:輸入信號經阻抗變換電路后進行程控放大,再經采樣與保持電路后進人MAX118進行采樣。其中程控放大倍數和A/D采樣速率由垂直靈敏度和水平掃描速度確定,采樣時刻由上升沿觸發判斷和等效采樣控制單元決定。采樣數據存入雙端口RAM,顯示控制模塊讀取RAM內容并控制DAC904輸出顯示。圖1為系統總體設計實現框圖。

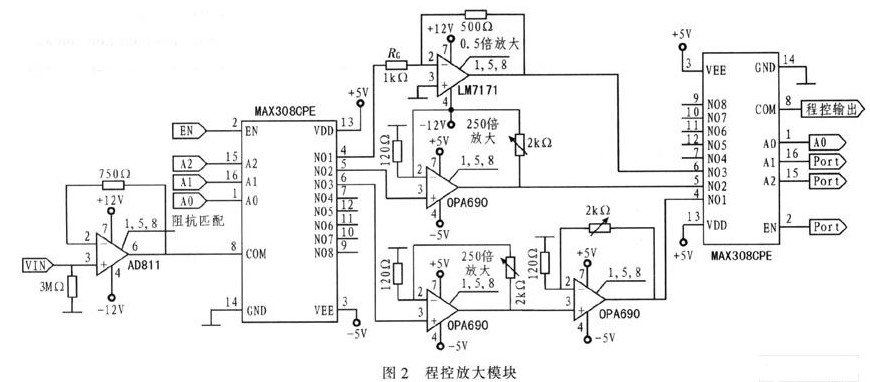

3.1 程控放大及前級阻抗匹配

信號先經前級AD811的阻抗匹配后實現系統的輸入阻抗為1 MΩ,再經過模擬開關MAX308CPE來實現不同通道放大的選擇,最后經模擬開關COM總輸出,如圖2所示。

3.2 采樣與保持電路

基于采樣頻帶要達到10 MHz,系統采用模擬開關THS3166,其特點是低導通電阻、電容,低漏電流,低捕獲時間和通斷孔徑時間,但只工作在正電壓范圍,故需前級加法器。開關前再加一級射極跟隨器,采用帶動容性負載強寬帶運放THS3001做前后級的隔離。

3.3 整形及測頻電路

高頻段整形采用高速比較器MAX913,低頻段采用低速比較器LM311。為提高輸入MAX913信號的信噪比,在其前級加一級無限增益放大,采用高頻率運算放大器LM7171,放大倍數50,這樣減小MAX913輸出脈沖邊沿抖動。同時,為避免高頻整形方波的諧波發射,比較器輸出均經74LS393分頻后送入FPGA進行等精度測頻,脈沖邊沿更陡峭,便于測量。

3.4 A/D采樣電路

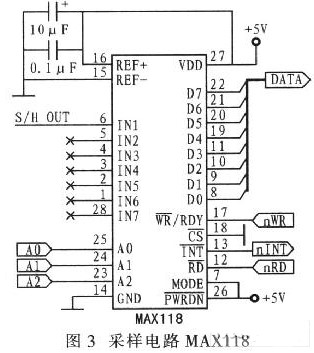

A/D轉換器采樣是信號處理的重要部分,是對模擬信號進行數字量化。采用MAx118的流水線工作模式,該模式下MAX118的工作直觀,控制簡單。圖3為MAX118的實現電路。

4 系統軟件設計

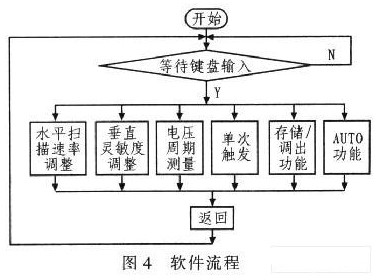

簡化后的系統軟件流程如圖4所示。系統主體功能采用模塊化的設計思想,通過按鍵進行選擇,且菜單界面良好,具有較強的人機交互性。為了在示波器上顯示穩定的波形,采用內觸發方式進行掃描,軟件對觸發電平的設置較好排除硬件毛刺產生的干擾,觸發和波形較穩定,且易實現觸發電壓的調整。另外雙端口RAM的使用還使系統具備自動調節和波形存儲的功能。

5 測試結果

5.1 使用的儀器及測試方案

PC機:清華同方P1.7 G,512 M;直流穩壓電源:SG1733SB;雙蹤示波器:泰克TDS1002;仿真機:E51/S偉福;信號源:Agilent 33120A;數字合成高頻信號發生器:SP1461。

將系統行列掃描輸出端分別與模擬示波器X軸與y軸輸入端相連,進行垂直靈敏度和水平掃描速度測試,信號幅值和周期測試。

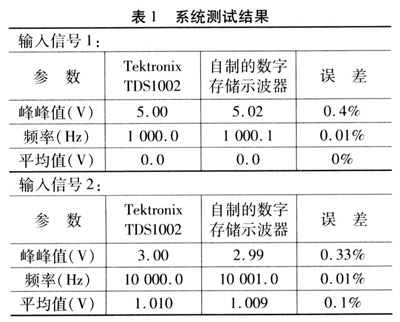

5.2 測試數據及分析

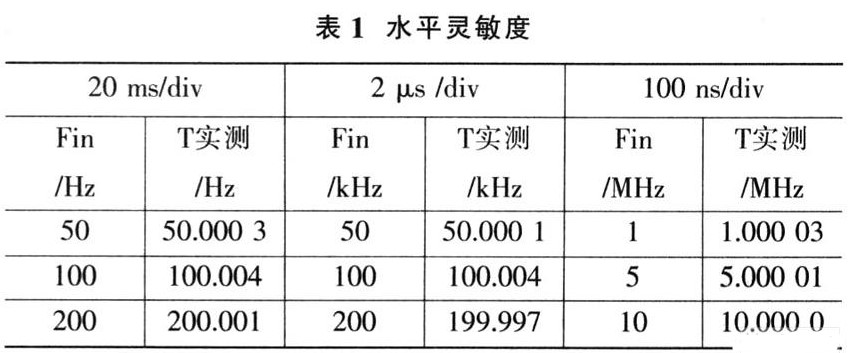

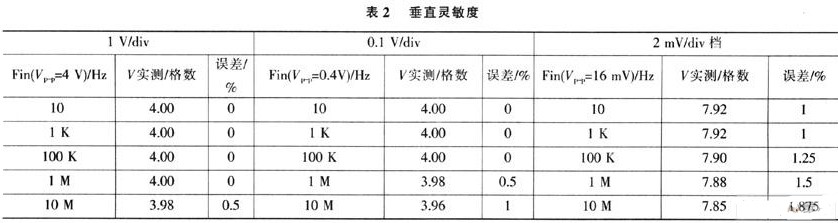

表1和表2分別給出了該系統設計的水平靈敏度和垂直靈敏度測試數據。

系統電壓測量誤差主要于前級信號調理電路,被測信號是寬帶寬,高動態范圍的信號,因而對前級放大器幅頻特性要求很高。系統頻率測量的誤差于等精度測頻中對頻標計數的±1誤差,以及比較器邊沿抖動和工作的不穩定性。

系統具有3檔垂直靈敏度,電壓測量誤差小于2%,7檔水平掃描速率,周期測量誤差小于0.01%,以及觸發電平調節和存儲波形的功能。

6 結束語

該數字示波器增加了垂直靈敏度和水平掃描速度的檔位、AUTOSET和光標顯示以及對顯示波形處理的功能,顯示波形無明顯失真,幅度測量誤差小于2%,頻率測量精度優于0.01%,并能進行單次觸發,存儲/調出波形。系統的顯示輸出采用模擬示波器和128×64點陣液晶相結合的方式,波形顯示清晰,工作穩定,操作簡單,人機界面友好。

-

FPGA

+關注

關注

1644文章

22007瀏覽量

616332 -

單片機

+關注

關注

6067文章

44960瀏覽量

648740 -

示波器

+關注

關注

113文章

6633瀏覽量

188643

發布評論請先 登錄

等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計

基于單片機的等效采樣示波器設計

采用實時采樣和等效采樣相結合實現數字示波器的設計

利用單片機和FPGA器件實現等效和實時采樣方式的數字示波器設計

利用單片機和FPGA器件實現等效和實時采樣方式的數字示波器設計

評論