概述

隨著大規(guī)模集成電路和單片機(jī)的迅速發(fā)展,復(fù)雜可編程邏輯器件(CPLD)具有使用靈活、可靠性高、功能強(qiáng)大的優(yōu)點(diǎn),在電子產(chǎn)品設(shè)計(jì)中得到了廣泛的應(yīng)用。CPLD 可實(shí)現(xiàn)在系統(tǒng)編程,重復(fù)多次,而且還兼容IEEE1149.1(JTAG)標(biāo)準(zhǔn)的測(cè)試激勵(lì)端和邊界掃描能力,使用CPLD 器件進(jìn)行開發(fā),不僅可以提高系統(tǒng)的集成化程度、可靠性和可擴(kuò)充性,而且大大縮短產(chǎn)品的設(shè)計(jì)周期。由于CPLD 采用連續(xù)連接結(jié)構(gòu),易于預(yù)測(cè)延時(shí),從而使電路仿真更加準(zhǔn)確。CPLD 是標(biāo)準(zhǔn)的大規(guī)模集成電路產(chǎn)品,可用于各種數(shù)字邏輯系統(tǒng)的設(shè)計(jì)。近年來(lái),隨著采用先進(jìn)的集成工藝和大批量生產(chǎn),CPLD 器件成本不斷下降,集成密度、速度和性能都大幅度提高,這樣一個(gè)芯片就可以實(shí)現(xiàn)一個(gè)復(fù)雜的數(shù)字電路系統(tǒng);再加上使用方便的開發(fā)工具,給設(shè)計(jì)修改帶來(lái)很大方便。

實(shí)驗(yàn)室設(shè)計(jì)開發(fā)了一款無(wú)線數(shù)據(jù)接收平臺(tái),上下行速率可以達(dá)到1Mbps。射頻部分采用了Maxim 的射頻套片,基帶部分采用了OMAP 平臺(tái),基帶射頻接口采用了ADI 公司的混合信號(hào)前端(MxFE?)基帶傳輸芯片AD9861,系統(tǒng)的邏輯控制和數(shù)據(jù)的緩沖采用了ALTERA 的CPLD EPM240GT100C3。

2 EPM240GT100C3 實(shí)現(xiàn)的功能與總體要求

EPM240GT100C3要完成AD9861的時(shí)序控制、AD9861和OMAP之間的數(shù)據(jù)緩存以及提供網(wǎng)口芯片LAN91C93所需的控制信號(hào)。在這幾項(xiàng)功能中,最主要的是數(shù)據(jù)緩存功能。要想正確地實(shí)現(xiàn)緩存功能,就必須要求緩存的收發(fā)I、Q數(shù)據(jù)不丟失,不顛倒,不錯(cuò)相,同時(shí)保證數(shù)據(jù)的先寫后讀。按照這樣的思想,再結(jié)合兩邊的接口時(shí)序正確地配置讀寫地址、讀寫時(shí)鐘,就可以完成所需功能。

3 CPLD 程序的詳細(xì)設(shè)計(jì)

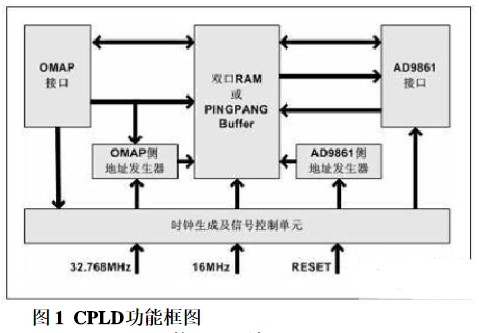

CPLD的主要功能是完成數(shù)據(jù)緩存和一些時(shí)鐘控制信號(hào)的產(chǎn)生。其功能框圖如圖1所示,主要包括雙口RAM存儲(chǔ)體單元,時(shí)鐘和控制信號(hào)產(chǎn)生單元,OMAP側(cè)地址發(fā)生單元,AD9861側(cè)地址發(fā)生單元。

3.1 雙口RAM 的設(shè)計(jì)方法

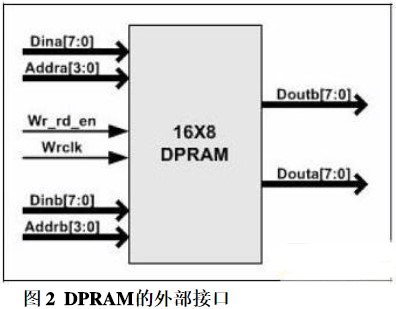

因?yàn)镺MAP和AD9861兩邊都有讀寫操作,于是選擇了雙口RAM(DPRAM)作為數(shù)據(jù)的緩存。由于CPLD內(nèi)部的邏輯資源和布線資源有限,并且沒有獨(dú)立的DPRAM區(qū),只能用DFF來(lái)完成緩存功能,這就限制了DPRAM的大小。因?yàn)橄到y(tǒng)要求每個(gè)DMA中斷讀寫8個(gè)數(shù)據(jù),為了減小讀寫沖突的可能性,同時(shí)盡量地降低FF資源的利用,最終采用了相當(dāng)于兩個(gè)8×8大小乒乓緩沖的16×8雙口RAM緩沖區(qū)。DPRAM的外部接口如圖2所示:

其中dina和douta接OMAP的數(shù)據(jù)線,dinb和doutb接AD9861的數(shù)據(jù)線,addra和addrb為內(nèi)部產(chǎn)生的讀寫地址。Wr_rd_en控制讀寫的方向,和TX_RX相連,即當(dāng)Wr_rd_en=’1’時(shí),為發(fā)射,數(shù)據(jù)由OMAP寫入,AD讀出,數(shù)據(jù)流向從dina->doub; 當(dāng)Wr_rd_en=’0’時(shí),為接收,數(shù)據(jù)由AD端寫入,AD讀出,數(shù)據(jù)流向從dinb->doua;wrclk在四種時(shí)鐘之間切換,分別為3.2768M,6.4M,75M,84M,由TX_RX和V_D_SEL信號(hào)的高低來(lái)控制。為了降低布線資源的使用,讀數(shù)時(shí)沒有用讀時(shí)鐘,而是直接把a(bǔ)ddra和addrb地址上的數(shù)據(jù)輸出,因?yàn)閍ddra和addrb本來(lái)就是與讀寫時(shí)鐘同步的。

3.2 時(shí)鐘產(chǎn)生

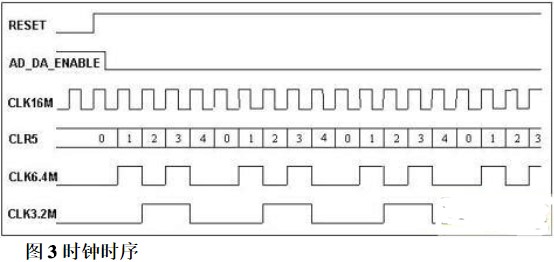

CPLD輸入時(shí)鐘有來(lái)自射頻的16M時(shí)鐘,來(lái)自外部晶振的32.768M時(shí)鐘和來(lái)自O(shè)MAP接口的75M時(shí)鐘CLK。其中16M時(shí)鐘用于產(chǎn)生數(shù)據(jù)應(yīng)用時(shí)AD9861所需要的3.2M、6.4M轉(zhuǎn)換時(shí)鐘,32.768M時(shí)鐘用于產(chǎn)生語(yǔ)音應(yīng)用時(shí)AD9861所需要的1.6384M、3.2768M時(shí)鐘以及CODEC AIC1110所需要的8K和2.048M時(shí)鐘。SDCLK本可以作為OMAP讀寫的主時(shí)鐘,但必須要使用CAS信號(hào)作為讀寫允許配合使用才行,為了節(jié)省布線資源,不用讀寫允許,就直接用CAS作為寫時(shí)鐘及OMAP側(cè)的地址產(chǎn)生使用,而SDCLK則用于產(chǎn)生一些同步脈沖。這些產(chǎn)生的時(shí)鐘除了輸出給外部芯片外,還在CPLD內(nèi)部作為地址產(chǎn)生的時(shí)鐘使用。3.2M和6.4M的時(shí)鐘產(chǎn)生是把16M的時(shí)鐘從0到4計(jì)數(shù),由reset和ad_da_enable給計(jì)數(shù)器清零,這樣的模5計(jì)數(shù)器的最低位即為6.4M,次低位為3.2M時(shí)鐘。這種時(shí)鐘產(chǎn)生的方式只需要三個(gè)DFF,節(jié)省邏輯資源,而且不會(huì)產(chǎn)生毛刺,但產(chǎn)生的時(shí)鐘占空比不是50%,實(shí)踐證明在低速應(yīng)用時(shí),AD9861是可以正常工作的。系統(tǒng)的時(shí)鐘時(shí)序如圖3所示。

1.6384M和3.2768M時(shí)鐘的方法同理,只是需要把32.768M的時(shí)鐘20分頻而已,同樣計(jì)數(shù)器的清零由reset和ad_da_enable控制,這樣得到的模20計(jì)數(shù)器的第2位即為3.2768M,第三位為1.6384時(shí)鐘,時(shí)序跟上圖相似,這里就不再給出。

這四個(gè)時(shí)鐘被分時(shí)賦給AD9861的主時(shí)鐘ADA_CLK,具體是哪個(gè)時(shí)鐘被賦ADA_CLK,由收發(fā)切換信號(hào)TX_RX,語(yǔ)音和數(shù)據(jù)選擇信號(hào)V_D_SEL控制。當(dāng)TX_RX=’0’ 且V_D_SEL=’0’時(shí),輸出給ADA_CLK的時(shí)鐘為1.6384M;當(dāng)TX_RX=’1’且V_D_SEL=’0’時(shí),輸出給ADA_CLK的時(shí)鐘為3.2768M;當(dāng)TX_RX=’0’ 且D_SEL=’1’時(shí),輸出給ADA_CLK的時(shí)鐘為3.2M;當(dāng)TX_RX=’1’ 且V_D_SEL=’1’時(shí),輸出給ADA_CLK的時(shí)鐘為6.4M。

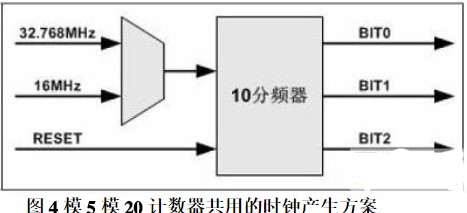

為了進(jìn)一步節(jié)省資源,可以考慮把模5和模20的計(jì)數(shù)器共用,方案如圖4所示,BIT1和BIT2即為所需的時(shí)鐘,這時(shí)前端時(shí)鐘源由V_D_SEL選擇,BIT1和BIT2的選擇輸出由TX_RX控制。

2.048M的時(shí)鐘產(chǎn)生由32.768M時(shí)鐘16分頻得到,計(jì)數(shù)器的復(fù)位由reset和語(yǔ)音允許audcken控制,這樣得到的模16的計(jì)數(shù)器的高位即為2.048M時(shí)鐘。8K時(shí)鐘是對(duì)產(chǎn)生的2.048M時(shí)鐘256分頻得到。

3.3 地址產(chǎn)生

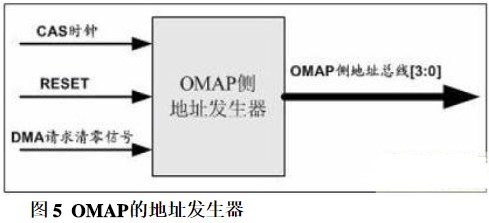

在使用雙口RAM作為數(shù)據(jù)緩存時(shí),有兩部分地址產(chǎn)生電路:OMAP側(cè)地址產(chǎn)生電路和AD9861側(cè)地址產(chǎn)生電路。AD9861側(cè)地址產(chǎn)生電路和OMAP側(cè)地址產(chǎn)生電路大致相同,但由于這2個(gè)地址發(fā)生器同時(shí)使用,所以不能復(fù)用。OMAP的地址發(fā)生器框圖如下:

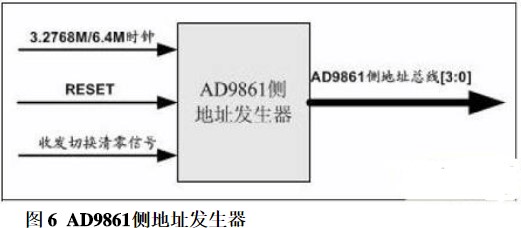

CAS 時(shí)鐘只負(fù)責(zé)對(duì)低3 位地址進(jìn)行計(jì)數(shù),而最高位由于選擇2 個(gè)8×8RAM 中的一個(gè),為防止adda 和OMAP 同時(shí)讀寫同一個(gè)RAM,將OMAP 側(cè)的高位地址線取值為AD9861 側(cè)的地址最高位的反相。DMA 請(qǐng)求清零信號(hào)作用:在AD9861 側(cè)每觸發(fā)一次DMA 請(qǐng)求,就生成一個(gè)DMA 請(qǐng)求清零信號(hào),用于復(fù)位OMAP 側(cè)地址發(fā)生器,避免由于某此誤觸發(fā)引起OMAP 讀寫地址混亂。AD9861 側(cè)地址發(fā)生器如下:

4位地址總線的低3位用于選擇同一片RAM中的8個(gè)地址,最高位用于選擇2個(gè)8×8RAM中的一個(gè),收發(fā)切換信號(hào)用于在收發(fā)切換時(shí)給地址發(fā)生器清零,復(fù)位由于邏輯誤觸發(fā)導(dǎo)致的地址總線錯(cuò)誤。

3.4 LAN 控制信號(hào)產(chǎn)生

lan91c93是一款嵌入式以太網(wǎng)控制器,和OMAP一起構(gòu)成了嵌入式的以太網(wǎng)網(wǎng)絡(luò)接口卡。OMAP用異步的FLASH接口時(shí)序來(lái)訪問(wèn)lan91c93,由于lan91c93沒有片選輸入端,所以把flash的片選和讀寫信號(hào)通過(guò)作一定處理后輸出給lan91c93。OMAP把CS1空間分配給了lan91c93,當(dāng)nFLASH_CS1為低時(shí),把nFLASH_WE,nFLASH_OE輸出給nLAN_WE,nLAN_OE,否則nLAN_WE,nLAN_OE為高電平。同時(shí)把LAN_RDY信號(hào)通過(guò)CPLD透?jìng)鹘oOMAP,通知OMAP lan91c93準(zhǔn)備好數(shù)據(jù)的交換。

4 仿真和實(shí)測(cè)

4.1 數(shù)據(jù)接收狀態(tài)仿真

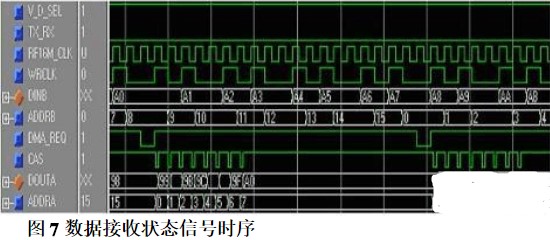

置V_D_SEL 為高,TX_RX 也為低,表示現(xiàn)在處于數(shù)據(jù)接收狀態(tài)。依據(jù)時(shí)序關(guān)系產(chǎn)生所需的時(shí)鐘,復(fù)位信號(hào);產(chǎn)生AD9861 數(shù)據(jù)線上的數(shù)據(jù),模擬AD 的輸出; 產(chǎn)生ADA 使能輸入控制信號(hào)AD_DA_ENABLE;SDRAM CAS 信號(hào)等等。如下圖所示,DINB為AD9861數(shù)據(jù)線上的數(shù)據(jù),WRCLK為內(nèi)部產(chǎn)生的6.4M鎖存時(shí)鐘,用來(lái)把DA數(shù)據(jù)線上的數(shù)據(jù)寫入雙口RAM中,AD9861側(cè)的地址ADDRB是對(duì)寫時(shí)鐘WRCLK的下降沿計(jì)數(shù)得到的。當(dāng)ADDRB為8或0時(shí),產(chǎn)生一DMA中斷,觸發(fā)OMAP通過(guò)EMIFF接口把數(shù)據(jù)讀到DSP的MEMORY進(jìn)行處理,每個(gè)DMA請(qǐng)求讀8個(gè)數(shù)據(jù),產(chǎn)生8個(gè)低脈沖的CAS信號(hào),對(duì)CAS的脈沖個(gè)數(shù)進(jìn)行計(jì)數(shù),得到OMAP側(cè)地址的低3位,最高位由ADDRB的MSB取反得到,這樣能避免讀寫沖突。可以看出AD的輸出數(shù)據(jù)能夠被正確地復(fù)現(xiàn)在OMAP的EMIFF接口數(shù)據(jù)線上,并被OMAP正確地讀進(jìn)去。

4.2 數(shù)據(jù)發(fā)射狀態(tài)仿真

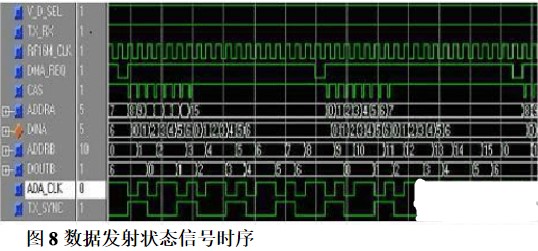

置V_D_SEL 為高,TX_RX 為高,表示現(xiàn)在處于數(shù)據(jù)發(fā)射狀態(tài)。依據(jù)時(shí)序關(guān)系產(chǎn)生所需的時(shí)鐘,復(fù)位信號(hào);產(chǎn)生EMIFF 接口數(shù)據(jù)線上的數(shù)據(jù),模擬OMAP 輸出的發(fā)射數(shù)據(jù); 模擬產(chǎn)生ADA 使能輸入控制信號(hào)AD_DA_ENABLE;SDRAM CAS 信號(hào)等等。如下圖所示,ADA_CLK為內(nèi)部產(chǎn)生的6.4M時(shí)鐘,輸出作為ad9861的DA轉(zhuǎn)換的主時(shí)鐘。對(duì)ADA_CLK的上升沿計(jì)數(shù)得到AD9861側(cè)的地址ADDRB,當(dāng)ADDRB為8或0時(shí),產(chǎn)生一DMA中斷,觸發(fā)OMAP通過(guò)EMIFF接口把發(fā)射數(shù)據(jù)輸出到EMIFF接口數(shù)據(jù)總線上,每個(gè)DMA請(qǐng)求寫8個(gè)數(shù)據(jù),產(chǎn)生8個(gè)低脈沖的CAS信號(hào),對(duì)CAS的脈沖個(gè)數(shù)進(jìn)行計(jì)數(shù),得到OMAP側(cè)地址的低3位,最高位由ADDRB的MSB取反得到,這樣能避免讀寫沖突。DINA為EMIFF接口數(shù)據(jù)線上的數(shù)據(jù),用CAS延遲信號(hào)的下降沿來(lái)鎖存DINA,滿足EMIFF的SDRAM寫時(shí)序,可以正確地把數(shù)據(jù)寫入到雙口RAM中。DOUTB為輸出給DA的數(shù)據(jù),同時(shí)按照時(shí)序要求產(chǎn)生一發(fā)射同步信號(hào)TX_SYNC,用來(lái)指示發(fā)射的I和Q,用ADA_CLK的上升沿采樣,正好能采樣到DOUTB和TX_SYNC的中間,確保數(shù)據(jù)的穩(wěn)定性。

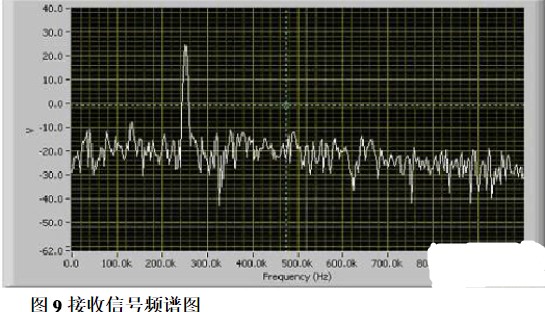

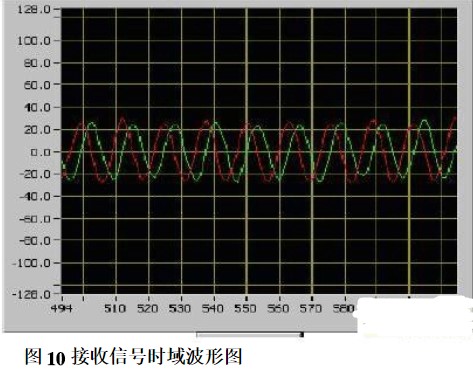

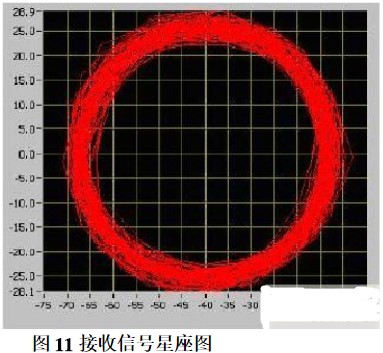

4.3 數(shù)據(jù)實(shí)測(cè)結(jié)果

記錄的頻譜圖,時(shí)域波形圖和星座圖如下,頻譜為250K,跟信號(hào)源設(shè)置的頻偏一致。時(shí)域波形I 落后Q 90 度,且I 的最大值對(duì)應(yīng)于Q 的零點(diǎn),兩者的正交性得到了保證,星座圖是一個(gè)圓同樣證明了這一點(diǎn)。

-

單片機(jī)

+關(guān)注

關(guān)注

6066文章

44951瀏覽量

648555 -

無(wú)線

+關(guān)注

關(guān)注

31文章

5543瀏覽量

175649 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44644

發(fā)布評(píng)論請(qǐng)先 登錄

可編程邏輯器件

怎么采用可編程邏輯器件設(shè)計(jì)數(shù)字系統(tǒng)?

PLD可編程邏輯器件

基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速AD采集

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

基于單片機(jī)的復(fù)雜可編程邏輯器件快速配置方法

什么是PLD(可編程邏輯器件)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

采用復(fù)雜可編程邏輯器件設(shè)計(jì)無(wú)線數(shù)據(jù)接收平臺(tái)

采用復(fù)雜可編程邏輯器件設(shè)計(jì)無(wú)線數(shù)據(jù)接收平臺(tái)

評(píng)論