引言

在廣播和傳送系統(tǒng)中,采用一種或者兩種串行接口來(lái)傳輸數(shù)字視頻:沒(méi)有壓縮的數(shù)據(jù)使用視頻串行數(shù)字接口(SDI),壓縮數(shù)據(jù)使用異步串行接口(ASI)。在視頻設(shè)備中,主要采用移動(dòng)圖像和電視工程師聯(lián)盟(SMPTE)定義的SDI來(lái)傳送視頻和音頻數(shù)據(jù)。

視頻設(shè)備能夠支持標(biāo)準(zhǔn)清晰度(SD)數(shù)字視頻格式、高清晰度(HD)數(shù)字視頻格式,或者同時(shí)支持。SD視頻傳輸?shù)腟DI速率為270Mbps, 360 Mbps或者540 Mbps,而HD視頻傳輸?shù)腟DI速率為1.485 Gbps或者1.485/1.001 Gbps。HD提供高質(zhì)量的視頻,代表了今后數(shù)字視頻廣播的發(fā)展方向。隨著HD視頻需求的增長(zhǎng),要求硬件能夠處理HD技術(shù)所需的大數(shù)據(jù)吞吐量。

在數(shù)字視頻傳送環(huán)境中,數(shù)據(jù)傳送的主要方式是ASI的270 Mbps單節(jié)目傳送流(SPTS)或者多節(jié)目傳送流(MPTS),這些方式由數(shù)字視頻廣播(DVB)協(xié)會(huì)定義。

廣播設(shè)備開(kāi)發(fā)人員通常使用ASSP來(lái)實(shí)現(xiàn)SDI和DVB-ASI功能,也可以利用可編程邏輯器件(PLD),使用PLD中的邏輯和其它嵌入式資源構(gòu)建所需的各種數(shù)字功能,來(lái)實(shí)現(xiàn)這些接口。通過(guò)使用PLD(而不是ASSP),可以顯著降低總成本。某些情況下,在每ASI通道或者每SDI端口的基礎(chǔ)上,PLD不到ASSP成本的1/10。

SDI的可編程邏輯解決方案

要達(dá)到SDI和DVB-ASI需要的270Mbps數(shù)據(jù)速率,可編程解決方案需要提供以下功能:

LVDS I/O

足夠的邏輯容量

數(shù)據(jù)恢復(fù)能力

對(duì)于HD-SDI數(shù)據(jù)速率,需要采用支持嵌入式SERDES技術(shù)、時(shí)鐘數(shù)據(jù)恢復(fù),并集成了高速收發(fā)器通道的PLD,例如Altera的Stratix GX系列FPGA。

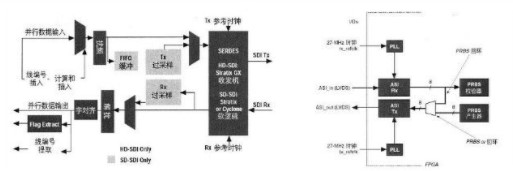

圖1所示為Altera可編程邏輯中實(shí)現(xiàn)SD-SDI和HD-SDI功能所需的構(gòu)成單元。SD-SDI解決方案在邏輯單元(LE)中利用過(guò)采樣技術(shù)來(lái)恢復(fù)數(shù)據(jù)。FPGA中的基本構(gòu)建模塊LE在SERDES模塊中表示為“軟邏輯”。在HD-SDI解決方案中,嵌入式SERDES和CDR電路完成時(shí)鐘和數(shù)據(jù)恢復(fù)功能。

HD-SDI方案中的其它功能包括發(fā)射機(jī)側(cè)的線編號(hào)插入和循環(huán)冗余校驗(yàn)(CRC)計(jì)算,以及接收機(jī)側(cè)的線編號(hào)提取和循環(huán)冗余校驗(yàn)。

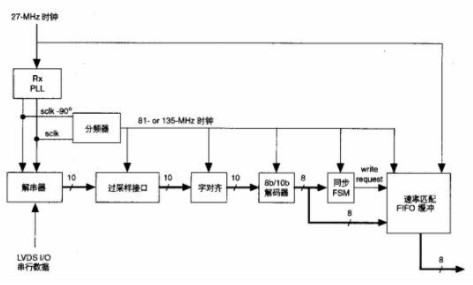

基于可編程邏輯的DVB-ASI解決方案

可以采用FPGA來(lái)實(shí)現(xiàn)DVB-ASI所需的數(shù)據(jù)速率,F(xiàn)PGA為ASI接收機(jī)和發(fā)射機(jī)提供LVDS I/O,并為接收機(jī)和發(fā)射機(jī)輸入基準(zhǔn)時(shí)鐘提供PLL。Altera的Cyclone、Stratix和Stratix GX系列FPGA具備這些功能。圖2所示為在FPGA中實(shí)現(xiàn)DVB-ASI所需的構(gòu)成單元,包括發(fā)射機(jī)和接收機(jī)耦合的回環(huán)通道,以及用于內(nèi)置測(cè)試操作的偽隨機(jī)二進(jìn)制序列(PRBS)校驗(yàn)器和PRBS產(chǎn)生器。

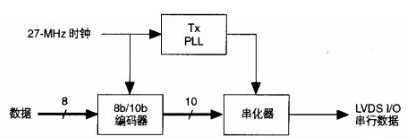

ASI接收機(jī)組成:

解串器,將到達(dá)的串行數(shù)據(jù)轉(zhuǎn)換為10比特寬的并行數(shù)據(jù)

過(guò)采樣接口,實(shí)現(xiàn)數(shù)據(jù)恢復(fù)和位同步

字對(duì)齊

8位/10位編碼器,將10位并行數(shù)據(jù)轉(zhuǎn)換為8位寬原始數(shù)據(jù)

同步狀態(tài)機(jī)探測(cè)字同步或者同步丟失

速率匹配FIFO緩沖匹配到達(dá)比特和發(fā)送(或者系統(tǒng))時(shí)鐘的速率。

圖3. ASI接收機(jī)結(jié)構(gòu)框圖

ASI發(fā)射機(jī)含有一個(gè)8位/10位編碼器和一個(gè)串化器,編碼器將8位寬的字轉(zhuǎn)換為10位,串化器將10位并行字轉(zhuǎn)換為串行數(shù)據(jù),采用一個(gè)10位移位寄存器實(shí)現(xiàn)該功能,以字速率從編碼器輸入,以LVDS輸出緩沖比特率輸出。27MHz基準(zhǔn)時(shí)鐘乘以10的PLL提供比特率時(shí)鐘,支持抖動(dòng)受控ASI傳輸串化。ASI發(fā)射機(jī)構(gòu)成單元如圖4所示。

在可編程邏輯中實(shí)現(xiàn)SDI和DVB-ASI

一般情況下,采用FPGA實(shí)現(xiàn)一個(gè)ASI通道需要的LE數(shù)量少于1,000。Cyclone II FPGA每通道成本低于1美元比現(xiàn)有ASSP方案低得多。

一個(gè)10位SD-SDI全雙工端口在Altera FPGA中只需要400個(gè)LE。對(duì)于Cyclone II FPGA中的10位SD-SDI數(shù)據(jù),其每端口成本也遠(yuǎn)遠(yuǎn)低于現(xiàn)有的ASSP方案。對(duì)于20位HD-SDI數(shù)據(jù),收發(fā)器通道邏輯大約需要1,000個(gè)LE,在Stratix GX器件中實(shí)現(xiàn)這些邏輯時(shí),每端口成本等于甚至低于ASSP的每端口成本。當(dāng)考慮到可編程邏輯的其它集成性能時(shí), Stratix GX方案的優(yōu)勢(shì)更加突出。

可編程邏輯集成功能還具有其它優(yōu)勢(shì)

在典型應(yīng)用中,DVB-ASI和SDI只是廣播設(shè)備全部功能的一部分。例如,DVB-ASI通常用于廣播數(shù)據(jù)轉(zhuǎn)發(fā)系統(tǒng),需要進(jìn)行視頻復(fù)用、壓縮、調(diào)制和解調(diào)、時(shí)隙復(fù)用、編解碼等信號(hào)處理。這些操作需要前向糾錯(cuò)(FEC)、濾波、間插、正交振幅調(diào)制(QAM)映射、Viterbi和Reed-Solomon解碼等數(shù)字信號(hào)處理功能。這些功能可以利用FPGA中的資源來(lái)實(shí)現(xiàn),包括LE、Cyclone II器件中的乘法器,以及Stratix器件中的DSP模塊。

圖4. ASI發(fā)射機(jī)結(jié)構(gòu)框圖

通過(guò)將這些功能集成到幾個(gè)器件中,基于FPGA的解決方案進(jìn)一步降低了開(kāi)發(fā)成本,節(jié)省了電路板空間,降低了系統(tǒng)復(fù)雜性。FPGA所具有的靈活性使開(kāi)發(fā)人員能夠定制實(shí)現(xiàn)設(shè)計(jì)中每一單元之間的接口,在最短的時(shí)間內(nèi)加入各種功能,突出設(shè)計(jì)質(zhì)量。設(shè)計(jì)人員還可以得到與單個(gè)可編程器件相同的ASI通道或者SDI端口數(shù),而采用ASSP就必須使用多個(gè)分立器件。

參考設(shè)計(jì)加速產(chǎn)品上市

在SDI參考設(shè)計(jì)中,對(duì)三個(gè)SMPTE建議抖動(dòng)參數(shù)進(jìn)行了評(píng)估:

抖動(dòng)產(chǎn)生器——器件或者系統(tǒng)產(chǎn)生一個(gè)串行數(shù)字信號(hào)(在這種情況下是HD-SDI),它含有某一振幅和頻率的正弦抖動(dòng)。產(chǎn)生的抖動(dòng)也可以是非正弦的。

接收抖動(dòng)容限——當(dāng)應(yīng)用于器件或者系統(tǒng)輸入時(shí),正弦抖動(dòng)的峰-峰值振幅會(huì)導(dǎo)致性能劣化。

抖動(dòng)傳送——輸入抖動(dòng)導(dǎo)致的器件或者系統(tǒng)輸出抖動(dòng)。

DVB-ASI標(biāo)準(zhǔn)并沒(méi)有針對(duì)抖動(dòng)容限提供任何規(guī)范,但可以采用下面的抖動(dòng)參數(shù)用于評(píng)估Altera的DVB-ASI參考設(shè)計(jì):

發(fā)射機(jī)的抖動(dòng)產(chǎn)生

接收機(jī)的抖動(dòng)容限

接收機(jī)靈敏度

輸出振幅和邊沿速率

Cyclone視頻演示板和Stratix GX串行視頻演示說(shuō)明板可以演示這些參考設(shè)計(jì)。

結(jié)語(yǔ)

與ASSP相比,Altera的DVB-ASI和SDI可編程邏輯解決方案能夠顯著降低廣播設(shè)備的開(kāi)發(fā)成本。將DVB-ASI和SDI功能集成到少量器件中,進(jìn)一步降低了成本、節(jié)省了電路板空間,降低了復(fù)雜性。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22020瀏覽量

617113 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3664瀏覽量

107758 -

發(fā)射機(jī)

+關(guān)注

關(guān)注

7文章

514瀏覽量

48532

發(fā)布評(píng)論請(qǐng)先 登錄

什么是可編程邏輯

可編程邏輯器件發(fā)展歷史

請(qǐng)問(wèn)有人知道Spartan6 LXT設(shè)備中DVB-ASI TS接口的工作解決方案嗎?

PLD可編程邏輯器件

可編程邏輯控制器的特點(diǎn)

FPGA視頻教程:可編程邏輯器件基礎(chǔ)

可編程邏輯器件向什么目標(biāo)前進(jìn)

可編程邏輯器件的分類(lèi)有哪些

FPGA面向汽車(chē)電子的可編程邏輯解決方案

可編程邏輯器件測(cè)試方法

基于國(guó)產(chǎn)可編程邏輯芯片的工業(yè)網(wǎng)絡(luò)解決方案

什么叫可編程邏輯器件 可編程邏輯器件有哪些特征和優(yōu)勢(shì)?

LMH0340/040/070/050 DVB-ASI SDI串行器和電纜驅(qū)動(dòng)器數(shù)據(jù)表

基于可編程邏輯的DVB-ASI解決方案提高廣播應(yīng)用的集成度

基于可編程邏輯的DVB-ASI解決方案提高廣播應(yīng)用的集成度

評(píng)論