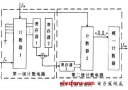

分頻器是一種基本電路,通常用來對(duì)某個(gè)給定頻率進(jìn)行分頻,得到所需的頻率。整數(shù)分頻器的實(shí)現(xiàn)非常簡單,可采用標(biāo)準(zhǔn)的計(jì)數(shù)器,也可以采用可編邏輯器件設(shè)計(jì)實(shí)現(xiàn)。但在某些場合下,時(shí)鐘源與所需的頻率不成整數(shù)倍關(guān)系,此時(shí)可采用小數(shù)分頻器進(jìn)行分頻。

-

分頻器

+關(guān)注

關(guān)注

43文章

491瀏覽量

51033 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2291瀏覽量

96280 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1893瀏覽量

133057

發(fā)布評(píng)論請(qǐng)先 登錄

新人求助 用VHDL實(shí)現(xiàn)任意小數(shù)分頻代碼

【夢(mèng)翼師兄今日分享】 任意時(shí)鐘分頻程序設(shè)計(jì)講解

基于FPGA 的等占空比任意整數(shù)分頻器的設(shè)計(jì)

基于FPGA的小數(shù)分頻實(shí)現(xiàn)方法

基于Verilog的FPGA分頻設(shè)計(jì)

此通用電路可以實(shí)現(xiàn)任意奇數(shù)分頻電路

verilog語言實(shí)現(xiàn)任意分頻

FPGA學(xué)習(xí)系列:13. 任意分頻器設(shè)計(jì)

分頻器的作用是什么 半整數(shù)分頻器原理圖分析

基于復(fù)雜可編程邏輯器件和VHDL語言實(shí)現(xiàn)半整數(shù)分頻器的設(shè)計(jì)

基于CPLD/FPGA的半整數(shù)分頻器設(shè)計(jì)方案

偶數(shù)分頻器的設(shè)計(jì)

偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻和小數(shù)分頻詳解

實(shí)現(xiàn)任意整數(shù)分頻的原理與方法講解

實(shí)現(xiàn)任意整數(shù)分頻的原理與方法講解

評(píng)論