本文是RISC-V基礎(chǔ)知識的入門篇。介紹了開放式架構(gòu)理念,模塊化ISA的技術(shù)描述,以及一些商業(yè)RISC-V微處理器實現(xiàn)。 RISC-V開放式指令集架構(gòu)是當(dāng)今專有架構(gòu)(如ARM架構(gòu))的流行替代方案

2022-07-06 14:52:24 742

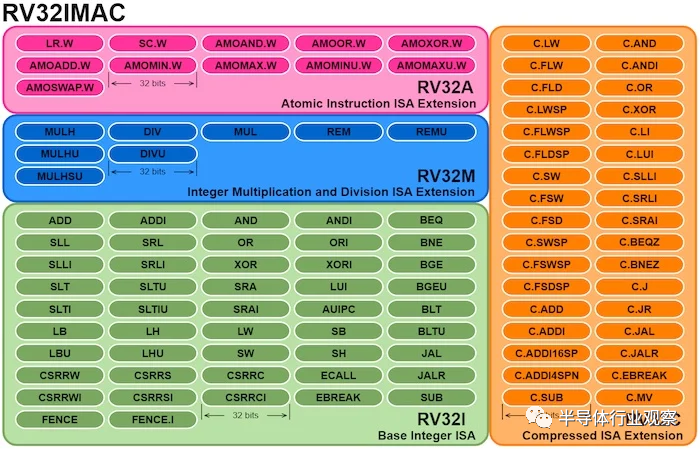

742 RISC-V ISA 命名規(guī)范RISC-V ISA 采用模塊化的方式進(jìn)行組織,每一個模塊使用一個英文字母表示,其命名格式可以參考如下:RV[字寬][指令集模塊]RV:RISC-V字寬(處理器寄存器

2021-12-09 06:31:44

縮寫

[###]

用于標(biāo)識處理器位寬,取值[32, 64,128],也就是處理器的寄存器位寬

[abc...xyz]

標(biāo)識該處理器支持的指令模塊集合

比如:RV64IMAC, 表示64 位 RISC-V

2024-03-12 10:25:21

推動未來的指令集體系結(jié)構(gòu)(ISA)的演進(jìn)。活動會議的特色是主要的技術(shù)公司和研究機構(gòu)討論:RISC-V體系結(jié)構(gòu)、商業(yè)和開源實施、軟件和硅半導(dǎo)體、向量和安全、應(yīng)用程序和加速器、模擬基礎(chǔ)設(shè)施等。訪問事件處理

2020-06-22 16:51:57

RISC-V處理器是開源的,那開發(fā)環(huán)境需要廠商自己開發(fā)還是沿用傳統(tǒng)的開發(fā)環(huán)境呢?比如keil

2024-01-13 19:18:35

精簡指令集計算機。RISC-V是基于RISC原理建立的免費開放指令集架構(gòu)(ISA),V是羅馬字母,代表第五代RISC(精簡指令集計算機),可讀作RISC-FIVE。通過開放式標(biāo)準(zhǔn)協(xié)作實現(xiàn)處理器創(chuàng)新的新時代

2020-08-13 15:13:41

RISC-V和開源處理器之間是什么關(guān)系?

2023-03-09 10:06:52

本文是RISC-V基礎(chǔ)知識的入門篇。介紹了開放式架構(gòu)理念,模塊化ISA的技術(shù)描述,以及一些商業(yè)RISC-V微處理器實現(xiàn)。RISC-V開放式指令集架構(gòu)是當(dāng)今專有架構(gòu)(如ARM架構(gòu))的流行替代方案。自

2022-12-23 17:51:49

本期文章目錄一個小型RISC-V開源處理器核介紹!#SOC#FPGA#RISC-V點擊閱讀數(shù)字積木從零開始寫RISC-V處理器(超詳細(xì))#RISC-V點擊閱讀數(shù)字積木為什么說模擬工程...

2021-07-23 09:42:00

RISC-V是什么?有哪些特點?如何去設(shè)計RISC-V處理器?

2021-06-18 09:24:03

面積降低制造成本,實現(xiàn)低功耗的微處理器,也可以用于實現(xiàn)高性能的應(yīng)用處理器。他進(jìn)一步指出,通過RISC-V,全球可以創(chuàng)建一個充滿活力的生態(tài)系統(tǒng),集合設(shè)計工具硬件軟件等,以經(jīng)濟(jì)高效的方式進(jìn)入迅速發(fā)展的新興市場

2020-06-22 16:55:03

完全自由免費使用,同時也容許企業(yè)添加自有指令集拓展而不必開放共享以實現(xiàn)差異化發(fā)展。 第二點是簡單,這也是RISC-V架構(gòu)的設(shè)計哲學(xué)。在處理器領(lǐng)域,X86與ARM架構(gòu)的發(fā)展過程也伴隨了現(xiàn)代處理器架構(gòu)技術(shù)

2020-08-25 11:17:39

RISC-V架構(gòu) RISC-V(發(fā)音為“risk-five”)是一個基于精簡指令集(RISC)原則的開源指令集架構(gòu)(ISA)。 與大多數(shù)指令集相比,RISC-V指令集可以自由地用于任何目的

2023-04-03 15:29:09

【摘要】 本文首先對RISC-V的架構(gòu)做了簡要的介紹,在此基礎(chǔ)上實現(xiàn)了LiteOS在RISC-V架構(gòu)上的適配過程的具體步驟,希望對你有所幫助。1 RISC-V架構(gòu)簡介RISC-V是一個基于精簡指令

2021-07-28 07:46:13

使用ISA,設(shè)計新處理器也是一項艱巨的任務(wù),但是支持RISC-V項目的許多公司,包括Western Digital這樣的巨頭,也已經(jīng)開放了其芯片設(shè)計的外包,從而將其騰出空間供其他人修改或使用。或者

2020-11-14 09:31:01

的Risc-V內(nèi)核高精度AI 處理器。K510-CORE是核心模組,板載一顆K510芯片,CPU采用雙核64bit RISC-V架構(gòu),K510搭載自主研發(fā)的第二代神經(jīng)網(wǎng)絡(luò)處理器KPU2.0,采用獨創(chuàng)計算

2022-11-18 14:15:24

64bit RISC-V架構(gòu),K510搭載自主研發(fā)的第二代神經(jīng)網(wǎng)絡(luò)處理器KPU2.0,采用獨創(chuàng)計算數(shù)據(jù)流技術(shù),算力較上一代提升3倍同時降低功耗。板載內(nèi)存為512MB LPDDR3@1600MHz。支持兩路

2022-11-18 15:10:22

公司從成立之初就一直堅持使用自主產(chǎn)權(quán)的內(nèi)核和MCU所需要的各種IP。雖然通過技術(shù)研發(fā)創(chuàng)新來實現(xiàn)微處理器的自主可控十分艱難,但堅持下來的價值和優(yōu)勢也十分明顯。針對目前RISC-V MCU的發(fā)展痛點,愛普特

2023-04-05 12:16:42

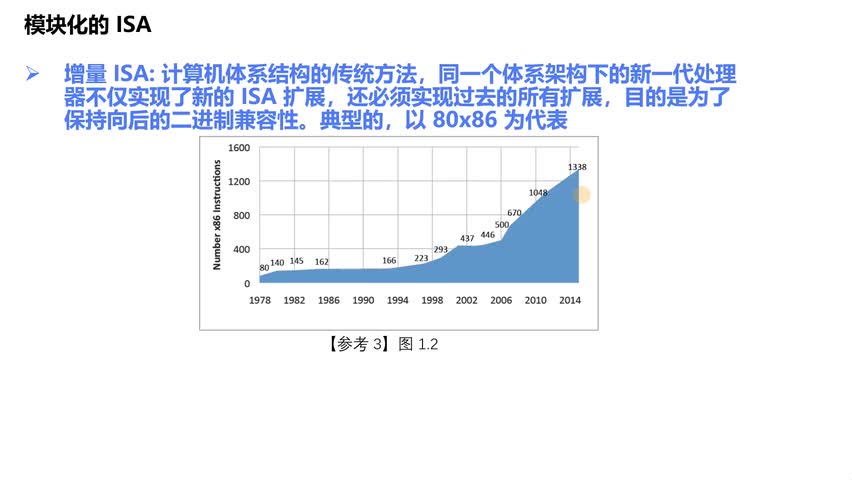

RISC-V架構(gòu)秉承簡單的設(shè)計哲學(xué)。體現(xiàn)為:在處理器領(lǐng)域,主流的架構(gòu)為x86與ARM架構(gòu)。x86與ARM架構(gòu)的發(fā)展的過程也伴隨了現(xiàn)代處理器架構(gòu)技術(shù)的不斷發(fā)展成熟,但作為商用的架構(gòu),為了能夠保持架構(gòu)的向后兼容性

2021-06-18 19:41:21

RISC-V簡介??RISC-V 是一個自由和開放的 ISA(開源指令集架構(gòu)),通過開放的標(biāo)準(zhǔn)協(xié)作實現(xiàn)處理器創(chuàng)新的新時代。RISC-V ISA在架構(gòu)上提供了一個新的自由、可擴展的軟件和硬件自由級別

2023-02-27 19:56:30

10 月 19 日,2021 云棲大會上,平頭哥開源了玄鐵RISC-V系列處理器,并開放了工具及系統(tǒng)軟件。這次的開源對國內(nèi)的RISC-V生態(tài)圈具有非常重要的意義。關(guān)注了一下這次開源發(fā)布的東...

2022-02-28 08:15:04

Piovaccari關(guān)于RISC-V架構(gòu)的理解Alessandro: RISC-V是一種指令集架構(gòu)(ISA),不關(guān)注RISC-V處理器微架構(gòu)的具體設(shè)計。當(dāng)前,有幾種實現(xiàn)方法,商業(yè)化的設(shè)計,如

2020-08-02 11:58:14

的玄鐵系列在物聯(lián)網(wǎng)芯片市場廣受認(rèn)可,目前已在人工智能、網(wǎng)絡(luò)通訊、工業(yè)控制等30多個行業(yè)實現(xiàn)了商業(yè)落地,出貨量超過30億顆,是中國RISC-V領(lǐng)域影響力和市占率最大的處理器;中科藍(lán)訊藍(lán)牙SoC芯片累計

2023-05-30 14:11:59

1 引言 提到微處理器大家都會想到Intel公司和AMD公司的產(chǎn)品,但在當(dāng)今嵌入式系統(tǒng) 應(yīng)用 中還有一個同樣響亮的名字ARM微處理器,它是一種RISC 架構(gòu)下嵌入式系統(tǒng)的核心部件,被廣泛地應(yīng)用到 工業(yè) 控制、無線通訊、消費類 電子 產(chǎn)品等很多領(lǐng)域。

2019-07-15 06:49:14

首先應(yīng)用RISC技術(shù)開發(fā)出PA-8000,主頻為180MHz,MIPS公司也推出了自己的RISC處理器——R2000;次年,SUN和德州儀器合作開發(fā)的Sparc處理器問世。 Sparc處理器憑借

2023-03-30 16:34:57

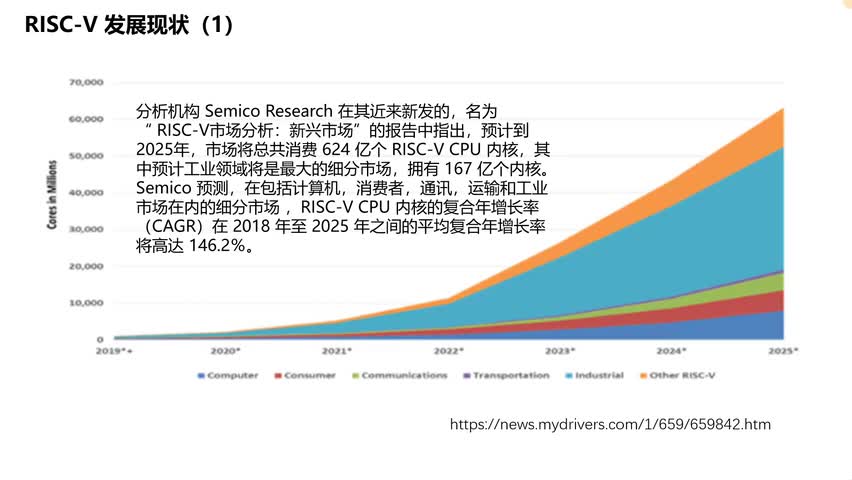

RISC-V是一個開源的指令集架構(gòu),它屬于一個開放的、非營利性質(zhì)的基金會,而基金會將謹(jǐn)慎地發(fā)展和維護(hù)這個開源的指令集架構(gòu)。 計算機體系結(jié)構(gòu)的傳統(tǒng)方法是增量ISA,新處理器不僅必須實現(xiàn)新的ISA擴展,還必須實現(xiàn)

2023-03-30 16:40:41

十幾年間不斷的推陳出新,導(dǎo)致了他們的指令集異常復(fù)雜,指令手冊讀起來非常難受,理解起來更是困難。RISC-V處理器架構(gòu)我必須得隆重的向大家介紹這樣的一個處理器架構(gòu),這個架構(gòu)不算新,因為它誕生于2010年,由

2023-04-14 10:53:25

速度大為提高。RISC技術(shù)極大地簡化了流水線的設(shè)計,使流水線技術(shù)更容易實現(xiàn),以較低的成本實現(xiàn)了較高的性能。高時鐘頻率和單周期執(zhí)行。在20世紀(jì)80年代初,CISC微處理器并沒有完全發(fā)揮半導(dǎo)體存儲器的性能

2022-04-24 10:02:29

ARM(Advanced RISC Machines),既可認(rèn)為是一個公司的名字,也可認(rèn)為是對一類微處理器的統(tǒng)稱。中文名ARM嵌入式外文名Advanced RISC Machines屬 于一類微處理器的統(tǒng)稱產(chǎn) 品RISC處理器、相關(guān)技術(shù)及軟件目錄1 簡介? 企業(yè)? 處理器2

2021-09-09 07:29:36

自己特色,根據(jù)不同用途有不同型號的處理器架構(gòu)。 關(guān)于RISC-V RISC:Reduced Instruction Set Computer,即精簡指令集計算機。 RISC-V是基于RISC原理建立

2021-04-25 09:13:19

設(shè)計RISC微處理器需要遵循哪些原則?基于FPGA技術(shù)用VHDL語言實現(xiàn)的8位RISC微處理器

2021-04-13 06:11:51

1.1簡介FreeRTOS中面向RISC-V的接口是易于拓展的,其提供了一系列基本的接口,用于操作適用于所有RISC-V實現(xiàn)中的通用寄存器,以及一系列的宏來處理特定的硬件實現(xiàn)中涉及到的特性以及拓展

2023-04-09 09:26:41

MIPS Technologies不再設(shè)計MIPS處理器。相反,它加入了RISC-V陣營,放棄了具有悠久歷史和技術(shù)聯(lián)系的同名架構(gòu)。此舉顯然預(yù)示著MIPS作為CPU系列的終結(jié),并進(jìn)一步減少了可用處理器

2021-03-09 19:30:07

,退出了破產(chǎn)狀態(tài),這令人驚訝,但并非完全不合理:在新的官方聲明中,(新)MIPS已成為RISC-V International的成員,該非營利組織負(fù)責(zé)管理完全開放式硬件的ISA,用事實上的開放式芯片標(biāo)準(zhǔn)

2021-03-09 19:31:13

位 FPU,以及兩顆來自美光的 16GB HBM2e 內(nèi)存。處理器的內(nèi)核通過中介層實現(xiàn)互連,雙塊 CPU 可提供 0.75 FP64 TFLOPS 的性能和 6 FP8 TFLOPS 算力。那么Occamy RISC-V 前景如何呢?

2023-05-13 08:44:36

的處理器指令集,是構(gòu)建芯片生態(tài)和發(fā)展芯片技術(shù)的核心部分,其重要性不言而喻。在此背景下,RISC-V有望成為新的選擇。盡管具有通用、開放與免費的先期優(yōu)勢,但相比已經(jīng)成熟的Arm和Intel x86,國內(nèi)

2020-11-14 09:26:41

瑞薩電子推出圍繞64位RISC-V CPU內(nèi)核構(gòu)建的RZ/5個通用微處理器單元(MPU),具體的型號是多少?性能怎么樣?

2024-01-11 13:03:31

具備與多種處理器架構(gòu)協(xié)同工作的潛質(zhì),其B系列更是可以達(dá)到最高6TFLOPS的算力,對于視覺計算優(yōu)異但3D圖形處理仍然偏科的RISC-V來說,可以說是一個很好的輔助,尤其是對于圖形性能有一定要求的消費類

2022-03-24 15:53:12

中出現(xiàn)的RISC-V拓展。

這本書的開篇講的是,為什么我們需要RISC-V指令集?

從過去的ISA的特點進(jìn)行引入,先以目前主流的x86指令集架構(gòu)為例列出了增量式指令集架構(gòu)中普遍含有的的一個缺點,并從指令集設(shè)計導(dǎo)論中

2024-01-22 16:24:25

本人沒有芯片設(shè)計,或者指令集方面較深的基礎(chǔ)知識,不過認(rèn)真看這本書也令我學(xué)到了不少。

書中一開始便提到RISC-V的目標(biāo)是稱為一款通用的指令集架構(gòu):需要適合設(shè)計各種規(guī)模的處理器,能兼容各種流行的軟件棧

2024-03-05 22:01:02

本文描述了RISC-V非特權(quán)體系結(jié)構(gòu)。標(biāo)記為“已批準(zhǔn)”的ISA模塊此時已被批準(zhǔn)。標(biāo)記為凍結(jié)的模塊,在提交批準(zhǔn)之前,預(yù)計不會有重大變化。標(biāo)記的模塊草案有望在批準(zhǔn)前修改。本文件包含RISC-V ISA模塊的以下版本:

2020-08-28 14:57:40

盡快聯(lián)系我們!另外,研討會的PPT也已經(jīng)開放下載了!開源指令集架構(gòu)(ISA) RISC-V近年迅速興起,并躍為新一代主流嵌入式處理器技術(shù),生態(tài)系蓬勃發(fā)展,特別適合AI、IoT、5G等新興應(yīng)用。 晶心

2021-08-18 13:55:33

?。 前云天勵飛市場中心總經(jīng)理;前SiFive China市場開發(fā)總監(jiān);前國科微電?副總裁;前全志科技營銷總監(jiān)等。議題四擴展RISC-V 的芯邊界-Andes最新的處理器核介紹RISC-V國際協(xié)會自

2023-01-06 14:27:42

(Integer)指令集用字母“ I ”表示,這是RISC-V處理器最基本也是唯一強制要求實現(xiàn)的指令集。其他指令集均為可選模塊,可自行選擇是否支持。RISC-V指令模塊描述如下:類型指令集指令數(shù)狀態(tài)描述

2023-03-28 16:57:06

,在美國開發(fā)的開源RISC-V處理器(不考慮托管平臺的因素),也是不會受到美國出口管制。RISC-V基金會負(fù)責(zé)指令集規(guī)范的定義,但并不負(fù)責(zé)基于指令集規(guī)范的具體實現(xiàn)。因此,即使RISC-V基金會總部留在

2020-06-22 16:49:27

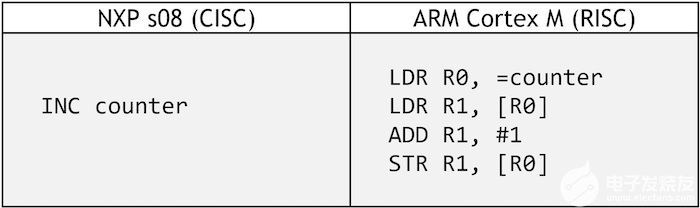

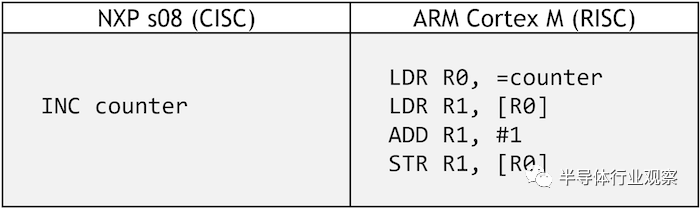

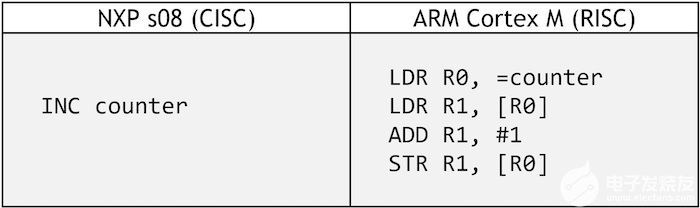

,然后返回到內(nèi)存中。RISC-V 和 ARM 都支持 32 位或 64 位指令集。

二、RISC-V 和 ARM 的區(qū)別

盡管 RISC-V 和 ARM 處理器技術(shù)的功能相似,但也有顯著區(qū)別。

1.

2023-06-21 20:31:32

RISC-V是一種開放式ISA(指令集體系結(jié)構(gòu)),為處理器體系結(jié)構(gòu)的創(chuàng)新開創(chuàng)了新紀(jì)元。RISC-V基金會由325多家成員公司組成。這是該技術(shù)的主要優(yōu)勢。軟件架構(gòu)師/固件工程師/軟件開發(fā)

2020-07-27 17:38:30

siFive搞RISC-V

賽昉搞RISC-V

香山搞RISC-V

到底什么是RISC-V?

先不問有什么用,RISC-V目前的能力來說,工業(yè)有沒有可能?

2024-02-02 10:41:21

什么是RISC-V?RISC-V指令具有哪些特點應(yīng)用?自己怎么才能設(shè)計出設(shè)計一套指令集?

2021-10-14 09:05:03

來源:liangkangnan的博客更新于 2021-01-31tinyriscv 一個從零開始寫的極簡易懂的RISC-V處理器核從零開始寫RISC-V處理器之一 前言從零開始寫RISC-V處理器

2022-08-22 18:25:55

來源:liangkangnan的博客更新于 2021-01-31tinyriscv 一個從零開始寫的極簡易懂的RISC-V處理器核從零開始寫RISC-V處理器之一 前言從零開始寫RISC-V處理器

2022-08-23 15:05:44

分析/監(jiān)控工具成了處理器開發(fā)時必不可少的軟件。盡管RISC-V的ISA規(guī)范已經(jīng)定義了硬件性能監(jiān)控(HPM),但總體支持程度上仍未完善。就以Linux上的性能分析工具Perf為例,該工具可以借助PMU

2021-12-27 08:00:00

解RISC-V與開源處理器。以下為幾個要點:指令集規(guī)范(Specification)和處理器實現(xiàn)(Implementation)是兩個不同層次的概念,要區(qū)分開。指令集(ISA)是規(guī)范標(biāo)準(zhǔn),往往用一本書或幾張紙

2020-06-22 16:47:55

基于 RISC-V 處理器的開發(fā)板。LoFive FE310 開發(fā)板GroupGets LLC 的 LoFive-R1 開發(fā)板正是其中之一(圖 1)。首先,LoFive R1 包含的 RISC-V

2020-08-21 18:35:32

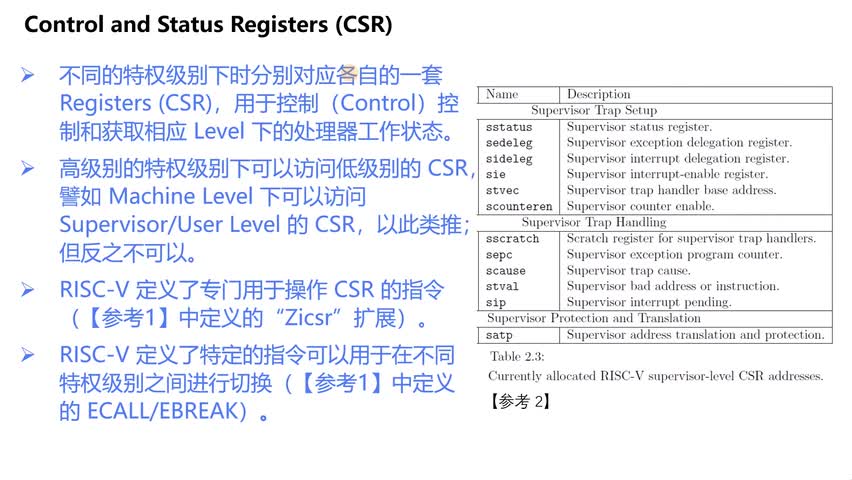

,用于實現(xiàn)一些特別功能。例如芯來科技的Bumblebee內(nèi)核就擴展了數(shù)個CSR用于處理中斷嵌套,記錄處理器當(dāng)前的異常類型等。RISC-V的可擴展特性給了廠商比較大的靈活性,可擴展特性也引起了碎片化

2022-08-25 15:51:38

RISC-V指令集體系結(jié)構(gòu)(ISA)易于擴展,并且沒有指定關(guān)于特定RISC-V微控制器或片上系統(tǒng)(SoC)實現(xiàn)的所有內(nèi)容。因此,F(xiàn)reeRTOS RISC-V移植也是可擴展的-它提供了一個處理所有

2019-11-29 15:54:41

,并涌現(xiàn)了眾多開源處理器及SoC采用RISC-V架構(gòu),這些處理器既有標(biāo)量處理器,也有超標(biāo)量處理器,既有單核處理器,也有多核處理器,本文接下來將簡單介紹RISC-V架構(gòu)的基本設(shè)計,隨后將詳細(xì)描述目前采用

2020-07-27 18:09:27

的 RISC-V 計算平臺,促進(jìn)形成貫穿 IP 核、芯片、軟件、系統(tǒng)、應(yīng)用等環(huán)節(jié)的 RISC-V 產(chǎn)業(yè)生態(tài)鏈。中國聯(lián)通指出,RISC-V 是基于精簡指令集計算(RISC)原理建立的開放指令集架構(gòu)(ISA

2023-03-16 14:56:58

RISC-V 處理器的設(shè)計和開發(fā)》下載地址 :https://eyun.baidu.com/s/3nwvO0rf密碼:3r5d本次課程胡老師主要從以下幾個地方展開講解那么,讓我們看一下技術(shù)大牛是如何看待當(dāng)下

2020-07-27 17:50:25

開發(fā)出商用的RISC-V處理器還需要哪些開發(fā)工具和環(huán)境?

處理器是軟硬件的交匯點,所以必須有完善的編譯器、開發(fā)工具和軟件開發(fā)環(huán)境(IDE),處理器內(nèi)核才能夠被用戶順利使用起來。目前RISC-V具有

2023-11-18 06:05:15

使用,同時也容許企業(yè)添加自有指令集拓展而不必開放共享以實現(xiàn)差異化發(fā)展。 架構(gòu)簡單 RISC-V架構(gòu)秉承簡單的設(shè)計哲學(xué)。體現(xiàn)為: 在處理器領(lǐng)域,主流的架構(gòu)為x86與ARM架構(gòu)。x86與ARM架構(gòu)的發(fā)展的過程

2023-03-19 10:52:16

協(xié)處理器進(jìn)行g(shù)pio操作,執(zhí)行完成后 ULP RISC-V 協(xié)處理器退出,等待下一個ULP喚醒周期。可當(dāng)在主MCU程序中使能 esp_sleep_enable_ulp_wakeup() 函數(shù)后,每當(dāng)

2023-02-09 06:52:26

的譚姓學(xué)生宣稱的“技術(shù)上看,RISC-V 相比Arm架構(gòu)處理器功耗低 5-6倍、面積效率提升5倍“ 看看笑笑就好,這種PR的話就別當(dāng)真了,真要當(dāng)真了你該懷疑這位加州大學(xué)伯克利分校的高材生的水平

2018-09-11 17:44:01

以及S-Mode模式環(huán)境可以通過更高層的特權(quán)來管理。玄鐵C系列處理器的安全拓展雖然RISC-V架構(gòu)的處理器具備物理內(nèi)存保護(hù)、多層權(quán)限模型、內(nèi)存管理單元等技術(shù)來支持可信執(zhí)行環(huán)境功能的實現(xiàn),但處理器仍然

2021-09-01 14:38:04

推動未來的指令集體系結(jié)構(gòu)(ISA)的演進(jìn)。活動會議的特色是主要的技術(shù)公司和研究機構(gòu)討論:RISC-V體系結(jié)構(gòu)、商業(yè)和開源實施、軟件和硅半導(dǎo)體、向量和安全、應(yīng)用程序和加速器、模擬基礎(chǔ)設(shè)施等。訪問事件處理

2020-08-02 11:50:33

精簡指令集計算機。RISC-V是基于RISC原理建立的免費開放指令集架構(gòu)(ISA),V是羅馬字母,代表第五代RISC(精簡指令集計算機),可讀作RISC-FIVE。通過開放式標(biāo)準(zhǔn)協(xié)作實現(xiàn)處理器創(chuàng)新的新時代

2019-07-29 07:57:16

我非常想了解如果想設(shè)計一個類似risc-v的處理器,整個開發(fā)流程是怎樣的?

2023-12-09 18:39:01

如題,現(xiàn)在risc-v發(fā)展的如此迅猛,不知道這些處理器主要應(yīng)用在哪些行業(yè)比較多呢?

2023-12-09 18:37:01

我在ULP RISC-V協(xié)處理器的例程中,沒有發(fā)現(xiàn)有對ADC的操作,請問RISC-V協(xié)處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數(shù)據(jù)。

2023-02-13 06:34:36

我在ULP RISC-V協(xié)處理器的例程中,沒有發(fā)現(xiàn)有對ADC的操作,請問RISC-V協(xié)處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數(shù)據(jù)。

2023-03-06 06:33:44

是由美國伯克利大學(xué)的 Krest 教授及其研究團(tuán)隊提出的,當(dāng)時提出的初衷是為了計算機/電子類方向的學(xué)生做課程實踐服務(wù)的。由于這是伯克利大學(xué)研究并流片的第五代RISC架構(gòu)處理器,因此就命名為RISC-V

2023-09-28 11:58:35

本帖最后由 余一yui 于 2023-4-26 10:44 編輯

《玄鐵RISC-V處理器入門與實戰(zhàn)》是一本介紹開源ISA(指令集架構(gòu))RISC-V的電子書。RISC-V是由加州大學(xué)伯克利分校

2023-04-12 11:16:58

的授權(quán),同時會產(chǎn)生一些費用,這也帶來了一個問題:假如有一天ARM公司不授權(quán)怎么辦?RISC-V架構(gòu)就是為了解決這個問題的!RISC-V最早在2010年起源于加州大學(xué)伯克利分校,由于受夠了現(xiàn)有處理器架構(gòu)

2023-04-14 22:10:56

與架構(gòu)等基礎(chǔ)概念,引出了RISC-V 基礎(chǔ)介紹,簡單介紹了RISC-V 由來。后續(xù)針對risc-v 會根據(jù)自身學(xué)習(xí)情況做相應(yīng)介紹。

原文鏈接:https://mp.weixin.qq.com/s/OZeLxR3ndk7J6bSPAgB7Fg

轉(zhuǎn)載自:嵌入式微處理器

原文鏈接:適合新手的RISC-V入門基礎(chǔ)知識

2023-02-23 20:25:05

面臨應(yīng)用碎片化、開發(fā)效率低、軟硬件適配難等問題,軟硬件生態(tài)尚未成熟。玄鐵RISC-V系列處理器采用自研技術(shù),覆蓋從低功耗到高性能的各類場景,支持AliOS、FreeRTOS、RT-Thread

2021-10-20 14:09:00

簡介

青稞處理器是沁恒微電子自研的32位微處理器,遵循和兼容開源的RISC-V指令集架構(gòu)規(guī)范,并提供可選的功能擴展。支持IMAFC指令集和自定義壓縮指令,并提供硬件壓棧(HPE)、免表中斷(VTF

2023-10-11 10:42:49

Piovaccari關(guān)于RISC-V架構(gòu)的理解Alessandro:RISC-V是一種指令集架構(gòu)(ISA),不關(guān)注RISC-V處理器微架構(gòu)的具體設(shè)計。當(dāng)前,有幾種實現(xiàn)方法,商業(yè)化的設(shè)計,如Si-Five

2020-10-13 16:40:41

https://github.com/JiaoXianjun/XiangShan談到RISC-V,應(yīng)該都會想到香山處理器。其經(jīng)歷了幾代的演進(jìn),性能越來越高。采用Chisel Rocketchip框架,能夠方便的定制屬于你的RISC-V處理器。對此,你有什么看法?

2023-04-14 15:51:59

Silicon Labs首席技術(shù)官Alessandro Piovaccari 關(guān)于RISC-V架構(gòu)的理解Alessandro: RISC-V是一種指令集架構(gòu)(ISA),不關(guān)注RISC-V處理器微架構(gòu)

2020-06-08 16:48:05 8242

8242 隨著這些年的發(fā)展,RISC-V的受重視程度與與日俱增。這主要因為它是免費的、靈活的,并且速度很快。這使RISC-V成為許多開發(fā)人員的安全便捷選擇。但是您會認(rèn)為RISC-V是通用RISC處理器還是定制的隨心所欲處理器?

2020-11-17 16:11:56 3167

3167 RISC-V ISA 命名規(guī)范RISC-V ISA 采用模塊化的方式進(jìn)行組織,每一個模塊使用一個英文字母表示,其命名格式可以參考如下:RV[字寬][指令集模塊]RV:RISC-V字寬(處理器寄存器

2021-11-26 16:36:13 5

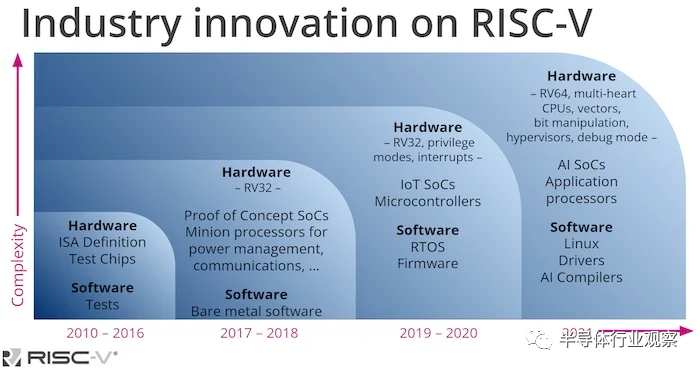

5 本文是 RISC-V 基礎(chǔ)知識的入門讀物。公開了開放式架構(gòu)理念,以及模塊化 ISA 的技術(shù)描述,以及一些商業(yè) RISC-V 微處理器實現(xiàn)。 RISC-V 開放指令集架構(gòu)是當(dāng)今可用的專有架構(gòu)(例如

2022-08-25 17:10:57 2081

2081

抽象-RISC-V是一種開放ISA(指令集架構(gòu))實現(xiàn)了處理器架構(gòu)創(chuàng)新的新時代。RISC-V包括開源處理器內(nèi)核、工具鏈、,模擬器和其他關(guān)鍵支持組件。RISC-V生態(tài)系統(tǒng)使處理器創(chuàng)新達(dá)到新水平體系結(jié)構(gòu)將是實現(xiàn)所需收益的關(guān)鍵驅(qū)動因素未來十年的性能和能效。

2022-11-23 16:56:56 2

2 英特爾的 x86 或 ARM 的 RISC 處理器的專有 ISA 一直是 Apple、戴爾、三星等 OEM 的選擇,但現(xiàn)在為什么我們需要像 RISC-V 這樣的開放 ISA,而不是所有這些經(jīng)過充分驗證的ISA。

2022-12-27 09:10:31 3750

3750

電子發(fā)燒友App

電子發(fā)燒友App

評論