引 言

??在當今變化的市場環境中,產品是否便于現場升級,是否便于靈活使用成為產品能否進入市場的關鍵因素。在這種背景下,Altera公司的基于SRAM LUT結構的FPGA器件得到了廣泛的應用。雖然這些器件應用廣泛,但由于其內部采用SRAM工藝,它的配置數據存儲在SRAM中。由于SRAM的易失性,每次系統上電時,必須重新配置數據,即ICR(In-Circuit Reconfigurability),只有在數據配置正確的情況下系統才能正常工作。在線配置方式一般有兩類:一是通過下載電纜由計算機直接對其進行配置,二是通過配置芯片對其進行配置。通過PC機對FPGA進行在系統重配置,雖然在調試時非常方便,但在應用現場是很不現實的。上電后,自動加載配置對FPGA應用來說是必需的。Altera公司提供的配置芯片有一次可編程型和可擦除編程型兩種:一次可編程型芯片只能寫入一次,不適合開發階段反復調試、修改及產品的方便升級;可擦除編程型價格昂貴,且容量有限,對容量較大的可編程邏輯器件,需要多片配置芯片組成菊花鏈形進行配置,增加系統設計的難度。

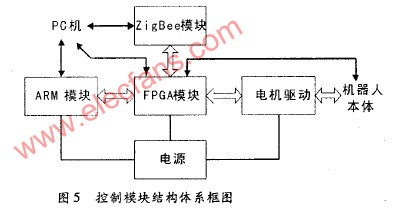

為了降低成本,目前在開發階段多用可擦除型配置芯片;最終產品用不可擦寫的配置芯片,但一次簡單的代碼更換就需要更換一次器件,這在產品升級時很不實用。至今還沒有低成本的配置芯片出現,而我們采用的這套配置方案充分考慮了在FPGA實際使用中,對設計的保密性和設計的可升級的要求,不但可以實現代替價格昂貴的不可擦寫和可擦寫配置芯片,而且可以實現多任務電路結構重配置。該方案有PC機控制程序、單片機和外部串行存儲器組成,只要通過替換外部串行存儲器,就可實現對不同容量的多種配置芯片的代替。PC機是用來將配置數據寫入存儲器的,在寫好數據后該配置系統不再需要PC機的控制,在單片機的控制下實現ICR或多任務電路結構重配置。多任務電路結構重配置即將多個配置文件分區存儲到外部存儲器中,然后由單片機接收不同的命令,以選擇讀取不同存儲器區的數據下載到FPGA器件,實現在線配置成多種不同的工作模式。

1 FPGA器件的配置方式和配置文件

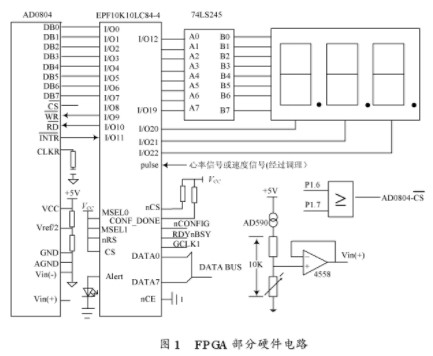

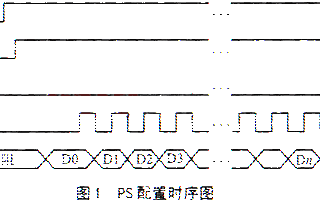

Altera公司生產的具有ICR功能的FPGA器件有FLEX6000、FLEX10K、APEX和ACEX等系列。它們的配置方式可分為PS(被動串行)、PPS(被動并行同步)、PPA(被動并行異步)、PSA(被動串行異步)和JTAG(Joint Test Action Group)等五種方式。這五種方式都能適用于單片機配置。PS方式因電路簡單,對配置時鐘的要求相對較低,而被廣泛應用。我們的配置方案也采用PS配置方式來實現ICR功能,圖1是PS配置方式的時序圖。

被動串行工作過程:當nconfig產生下降沿脈沖時啟動配置過程,在dclk上升沿,將數據移入目標芯片。在配置過程中,系統需要實時監測,一旦出現錯誤,nSTATUS將被拉低,系統識別到這個信號后,立即重新啟動配置過程。配置數據全部正確地移入目標芯片內部后,CONF_DONE信號跳變為高,此后,DCLK必須提供幾個周期的時鐘(具體周期數與DCLK的頻率有關),確保目標芯片被正確初始化,進入用戶工作模式。

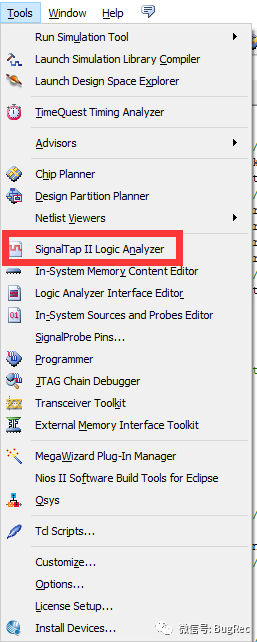

Altera的MAX+PLUS II或Quartus II開發工具可以生成多種配置或編譯文件,用于不同配置方法的配置系統,而對于不同系列的目標器件配置數據的大小也不同,配置文件的大小一般有.rbf文件決定。.rbf文件即二進制文件。該文件包括所有的配置數據,一個字節的 .rbf文件有8位配置數據,每一字節在配置時最低位最先被裝載。微處理器可以讀取這個二進制文件,并把它裝載到目標器件中。Altera提供的軟件工具不自動生成 .rbf文件,須按照下面的步驟生成:① 在MAX+PLUS II編譯狀態,選擇文件菜單的變換SRAM目標文件命令; ② 在變換SRAM目標文件對話框,指定要轉換的文件并且選擇輸出文件格式為 .rbf(Sequential),然后確定。

2 配置電路結構和原理

2.1 串行通信的電路結構和原理

PC機與單片機的接口如圖2所示。AT89C2051單片機通過串行口直接接收PC機傳送來的串行數據,然后把接收到的數據存入數據存儲器。由于PC機的串行口都是RS-232C標準的接口,所以,其輸入輸出在電平上和采用TTL電平的AT89C2051在接口時會產生電平不同的問題。為了解決這個問題,在PC機和單片機的串行通信電路中加入了MAX232芯片,以實現TTL電平和RS-232C接口電平之間的轉換。這樣PC機和AT89C2051單片機進行串行通信時就可以順利進行了。除了電路結構之外,要實現PC機和AT89C2051之間的通信,還需要有合適的通信軟件。

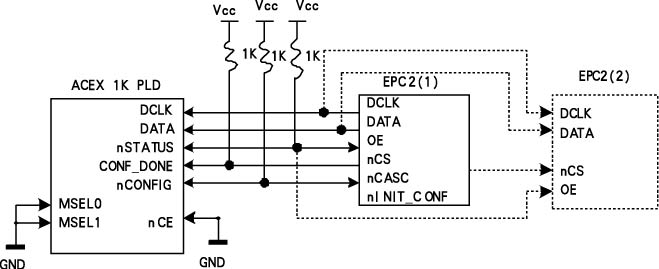

2.2 ICR控制電路原理

ICR電路原理如圖3所示。AT24C256用來存儲FPGA的配置數據。

ICR控制電路的工作過程為:經MAXPLUS II編譯生產的配置文件(.sof)通過格式轉換成為 (.rbf)。然后,利用PC機端的控制程序,通過PC機的串行通信口,經U1存儲在U2中。U1再根據系統的要求,通過P1.2、P1.3、P1.4、P3.0和P3.1等5個I/O口,將其存儲在U2中的配置數據下載到電路中的FPGA器件中去。

因作者設計電路中的FPGA是Altera公司的FLEX系列的EPF10K10,其配置文件的容量為15KB,故電路中采用1片AT24C128就可存儲EPF10K10的配置數據。我們選用AT24C256器件可以存儲兩個配置文件,是為了實現多任務電路重構,此時整個ICR控制電路只有2片IC。可以說,它是目前結構最簡單、成本最低的ICR控制電路。如果配置的FPGA是EPF10K30或更大門數的器件,則需要大容量的存儲器件或多片AT24C256。(在兩線串行總線上最多可接4片AT24C256。)

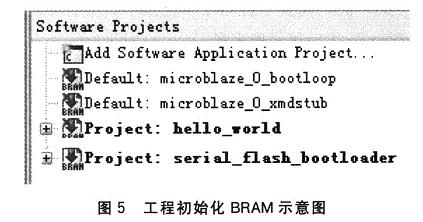

3 軟件設計

在該配置方案中,軟件包括在PC機端的控制軟件和在AT89C2051端的控制軟件兩部分。PC機端的軟件采用Visual Basic語言編程,而AT89C2051采用匯編語言進行編程。

3.1 PC機端的軟件

PC機端的軟件采用Visual Basic語言編程。VB支持面向對象的程序設計,具有結構化的事件驅動編程模式,而且可以十分簡便地作出良好的人機界面。PC機端的控制程序主要實現讀取.rbf文件并將其通過串口送出的功能。讀取文件時,主要使用讀取二進制文件命令。在串口通信方面,使用VB提供的具有強大功能的串口通信控件MSCOMM。該控件可設置串口狀態及串口通信的信息格式和協議。

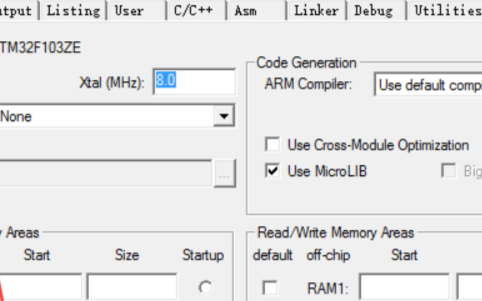

在實際工作中,要實現AT89C2051和PC機之間的有效通信,必須使其具有相同的波特率和相同的通信協議。作者采用了9600bps的波特率和N.8.1幀結構。N.8.1幀結構表示1幀串行數據有10位:起始位占用1位(低電平),用來表示字符開始;后8位為數據編碼,無奇偶校驗位;最后為停止位(高電平),用來表示字符傳送結束。單片機的串行口工作在方式1。方式1是標準的10位異步通信方式,10位數據和PC機的標準串口相對應,傳送的波特率由單片機工作時鐘和T1的溢出率共同決定。

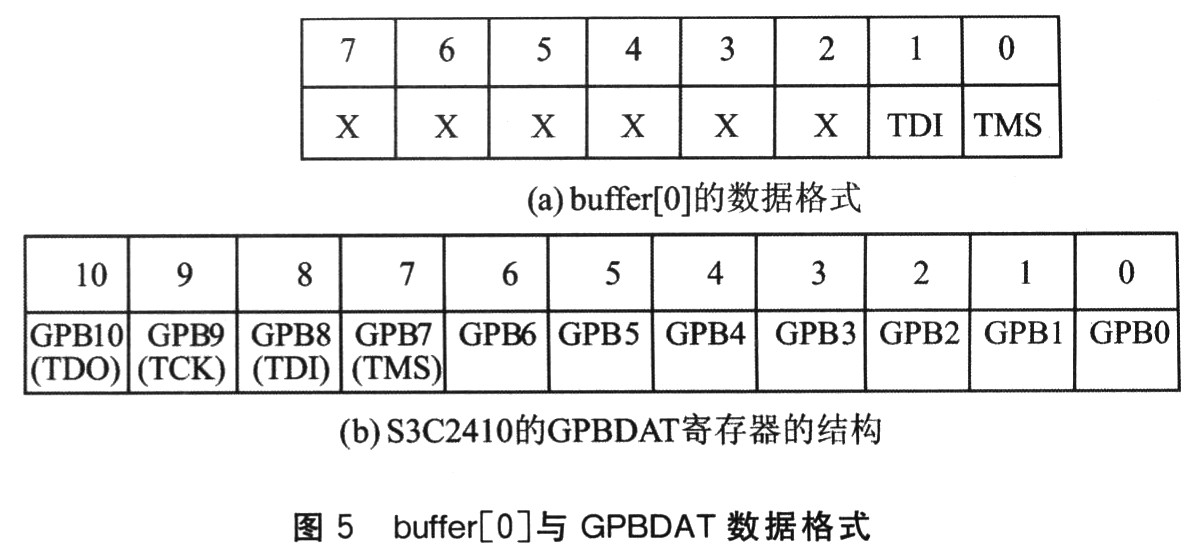

3.2 ICR控制電路軟件

在圖3介紹的ICR控制電路中,其存儲FPGA配置數據的存儲器 AT24C256采用I2C串行總線進行數據交換。其數據交換速度較慢,而FPGA配置數據又比較大,因此如何提高圖3介紹的ICR控制電路的配置速度將是軟件設計上的一個重點。限制速度的瓶頸主要是從AT24C256讀取數據和將數據寫入FPGA器件中。從AT24C256讀取數據,有讀當前地址、隨機讀和順序讀三種方式。這三種方式中,順序讀最簡單、速度最快。因為在同一片AT24C256中,僅需要寫入一次讀命令就可以按順序從0地址開始直至讀完整片AT24C256中的全部數據。向FPGA器件寫數據時,可以使用串行口的移位寄存器工作方式,即方式0。方式0數據的傳送以8位為1幀,無論是發送或是接收都是最低有效位居先。這和FPGA對數據的要求一致,傳送的波特率固定為振蕩頻率的1/12。本系統只需用到輸出方式,串行數據通過RXD端輸出,而用TXD端輸出移位脈沖。當1字節數據寫入串行數據緩沖器SBUF時,就開始發送。在此期間,發送控制器送出移位信號,使發送移位寄存器的內容右移1位,直至最高位(D7位)移出后,停止發送數據和移位時鐘脈沖。發送完1字節數據后,硬件置發送標志位TI為1,通過判斷TI的狀態決定是否向SBUF寫入數據。采用這種方式比采用普通(I/O)口要快很多。

4 結 論

我們設計的基于微控制器的FPGA器件的 ICR控制系統,具有線路結構簡單、開發容易、體積小、成本低的優點;可以支持3.3V和5V系統的配置;適用于需要ICR功能的電子裝置中。該ICR控制電路是為配置Altera公司FLEX系列的FPGA器件而設計的,稍加修改也適用于其它系列的FPGA器件。這個配置電路的主要弱點在于配置速率較慢,只能適用于配置速率要求不高的應用。

王玉化:工程師,研究方向EDA技術和嵌入式可編程系統。

- 配置方法(7747)

- 組圖FP(5547)

相關推薦

FPGA芯片配置方式及常見配置方法

9490

9490FPGA可重復配置和測試系統的實現

1414

1414

遠程在線更新FPGA程序的方法

27516

27516

基于SPI FLASH的FPGA多重配置

13669

13669

FPGA 是如何分類的?FPGA的使用方法

FPGA在線配置

FPGA在線配置模塊和自動測試模塊實現過程

FPGA配置電路

FPGA配置問題

FPGA中SPI復用配置的編程方法

FPGA實戰演練邏輯篇13:配置電路

FPGA實戰演練邏輯篇69:基于FPGA的在線系統調試概述

FPGA的接口配置如何進行配置?

FPGA芯片_GW2AN-55器件原理圖指導手冊

fpga 多配置的問題

Altium designer高版本如何在線搜索元器件

STM32單片機是怎樣配置FPGA的

Xilinx FPGA在線更新配置數據交流

Xilinx FPGA入門連載17:PWM蜂鳴器驅動之復位與FPGA重配置功能

一種基于DSP和JTAG接口的FPGA系統在線編程設計

使用高速SPI Nor Flash的FPGA配置

例說FPGA連載13:靈活定制——配置電路

例說FPGA連載18:配置電路設計

幾組實用FPGA原理設計圖

勇敢的芯伴你玩轉Altera FPGA連載14:FPGA下載配置電路

勇敢的芯伴你玩轉Altera FPGA連載52:Altera FPGA配置方式之AS/PS/JTAG配置方式

勇敢的芯伴你玩轉Altera FPGA連載53:PWM蜂鳴器驅動之FPGA在線下載配置

如何使用高速NOR閃存配置FPGA

支持重構的FPGA器件

有什么FPGA可重構方法可以對EPCS在線編程?

有什么好的FPGA在線培訓班嗎?

玩轉Zynq連載5——基于Vivado的在線板級調試概述

電源組用的元器件

談談Altera FPGA的配置

可在線升級的FPGA并行配置方法的實現

23

23FPGA器件在嵌入式系統中的配置方式的探討

10

10DSP和FPGA共用FLASH進行配置的方法

12

12基于單片機的Cyclone系列FPGA配置方法

64

64FPGA的全局動態可重配置技術

54

54FPGA器件的在線配置方法

448

448ACEX 1K系列CPLD配置方法探討

478

478

FPGA器件的在線配置方法

1062

1062

FPGA 重復配置和測試的實現

528

528

基于對EPCS在線編程的FPGA可重構方法

1310

1310FPGA中SPI復用配置的編程方法

3061

3061

FPGA重復配置和測試的實現

544

544

基于JTAG接口實現ARM的FPGA在線配置設計

3141

3141

ARM設計的FPGA可重構配置方法的實現及應用

1326

1326

使用CPLD和Flash實現FPGA的配置

8194

8194

一種基于SRAM的FPGA的加密方法

48

48Leon3的接口配置設計

1474

1474

Leon3軟核的FPGA SelectMap接口配置設計

3151

3151

微處理器系統中連接簡單的被動串行配置方法和被動并行異步配置方法

1

1V5 FPGA配置回讀

8730

8730反熔絲FPGA配置和編程方法

10165

10165

FPGA配置與測試的詳細方法分析與特點

5921

5921

關于fpga編程flash芯片和配置數據技巧

24007

24007

AS配置方式由FPGA器件引導配置操作過程

11628

11628

FPGA的配置/加載方式

17251

17251基于ICR技術的FPGA配置電路硬件設計及其工作原理

4908

4908

FPGA配置相關筆記

481

481FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明

17

17以Flash控制器為核心的FPGA在線更新功能實現設計流程介紹

2746

2746

Spartan-6 FPGA的配置教程說明

25

25FPGA的三種配置方式詳解

7500

7500基于FPGA器件EP20K200E芯片的配置方式在嵌入式系統中的應用研究

878

878

FPGA有哪些主要配置方式?

11307

11307

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法

21

21FPGA芯片配置分類及配置方式

6052

6052FPGA CPLD可編程邏輯器件的在系統配置方法

13

13?在配置FPGA器件時的常見問題及其解決方法

1140

1140FPGA配置模式和配置設計

862

862FPGA在線調試的方法簡單總結

1225

1225

使用高速NOR閃存配置FPGA

331

331

電子發燒友App

電子發燒友App

評論